基于FPGA的SAR数据源时序测试设计与实现*

赵 君,蔡晓乐,张宇坤,郭建奇

(西安航空计算技术研究所,西安 710065)

0 引言

星载数传分系统是遥感卫星中合成孔径雷达(SAR)的重要组成部分。当卫星在轨运行时,数传分系统主要针对星上有效载荷捕获的高分辨率图像数据完成接收、存储与传输功能[1-2]。针对数传分系统地面联试需求,避免价格昂贵的星上有效载荷在地面联试中频繁操作降低其寿命,通常使用SAR载荷数据模拟器(SAR数据源)代替星上真实有效载荷进行测试[3]。

文中的SAR数据源针对LVDS接口型数传分系统进行测试,根据功能对LVDS信号进行分类,一般包括时钟、门控和数据信号。系统通过时钟信号的上升沿触发信号改变,如果门控信号在时钟上升沿有效,则数据有效,反之数据无效[4]。理想条件下,系统要求门控和数据均在时钟上升沿跳变,信号接收与发送端均遵循此原则以保证数据的准确性。

但是,在数传分系统实际工作中,时钟、门控和数据信号存在相位偏移,主要原因包括逻辑综合约束,线缆长度不等长、寄生电容分布不均匀、高速信号振铃效应等,而此类问题只有在整星集成后才能暴露出来。为了缩短数传分系统正样机研制周期,降低研制风险,需要SAR数据源与数传分系统模拟星上实际工况联试,用于测试数传分系统数据接收功能的正确性与稳定性。因此要求SAR数据源能够模拟时钟、门控与数据信号时序不同步的情况。

1 SAR数据源系统设计原理

1.1 功能及技术指标

SAR数据源可以模拟符合卫星在轨运行时的数据及时序,基于SAR数据源的数传分系统测试原理如图1所示。

图1 SAR数据源测试原理

SAR数据源支持基于PN码自生成数据与本地加载数据输出两种输出模式,时钟频率44.44 MHz,可以设置数据出处正程和逆程。

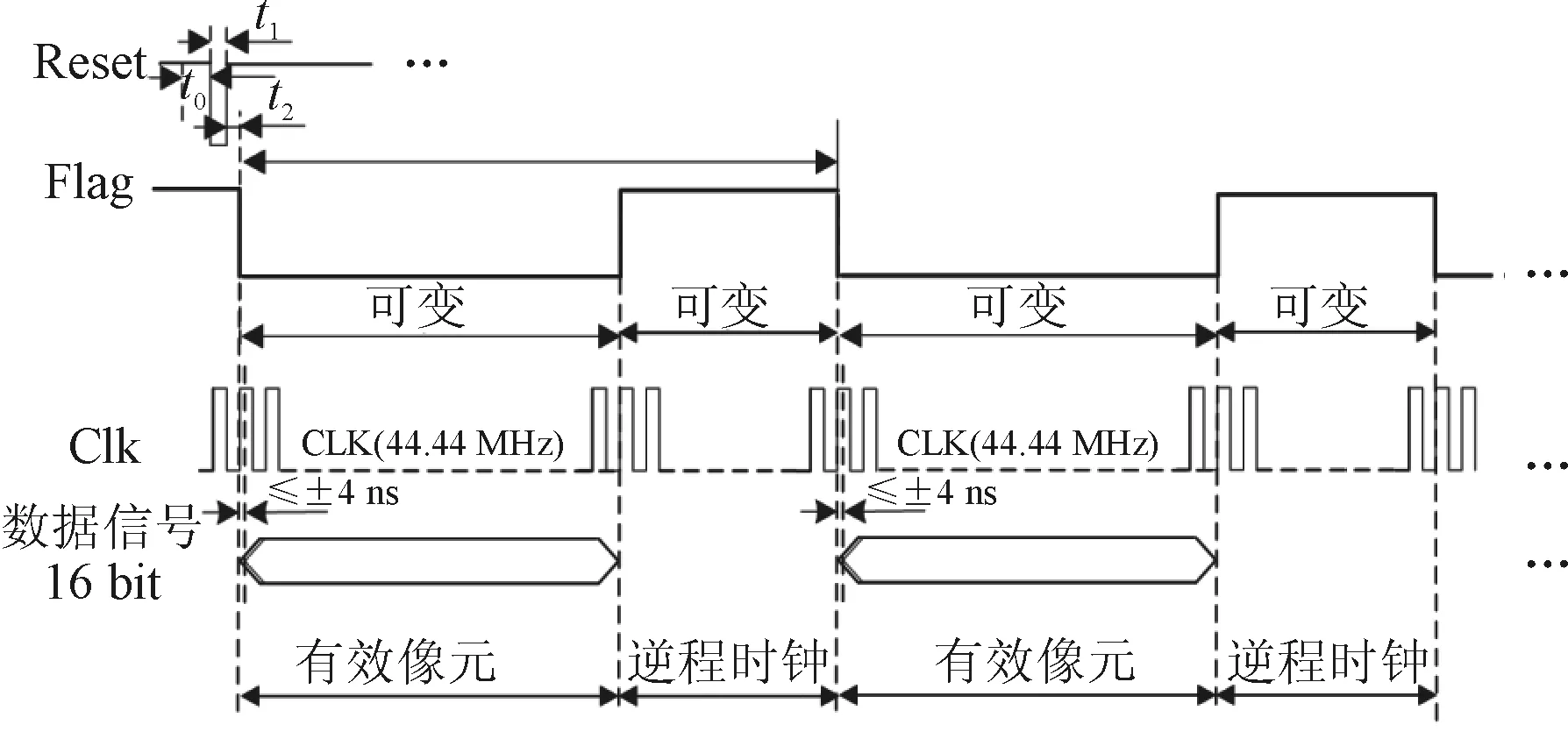

SAR数据源通道与数传分系统通信类型为LVDS接口,该通信接口包括CLK、Flag、DATA[15:0]、RESET四类信号,信号功能如下:

1) CLK,是SAR数据源与数传分系统接收控制器的同步传输时钟信号,时钟可配置,频率最高支持44.44MHz;

2) Flag,是决定数据正程与逆程的门控信号;

3) DATA[15:0],是信号数据线,支持I/Q模式配置;

4) RESET,数传分系统系统复位信号,由SAR模拟发起;

SAR模拟源与数传分系统接口时序关系如图2所示。

图2 SAR模拟源与数传分系统接口时序关系示意图

SAR数据源支持多种成像工作模式,主要包括聚束模式、标准条带模式、宽/窄幅扫描模式、超精细条带模式、波模式等。

1.2 硬件设计

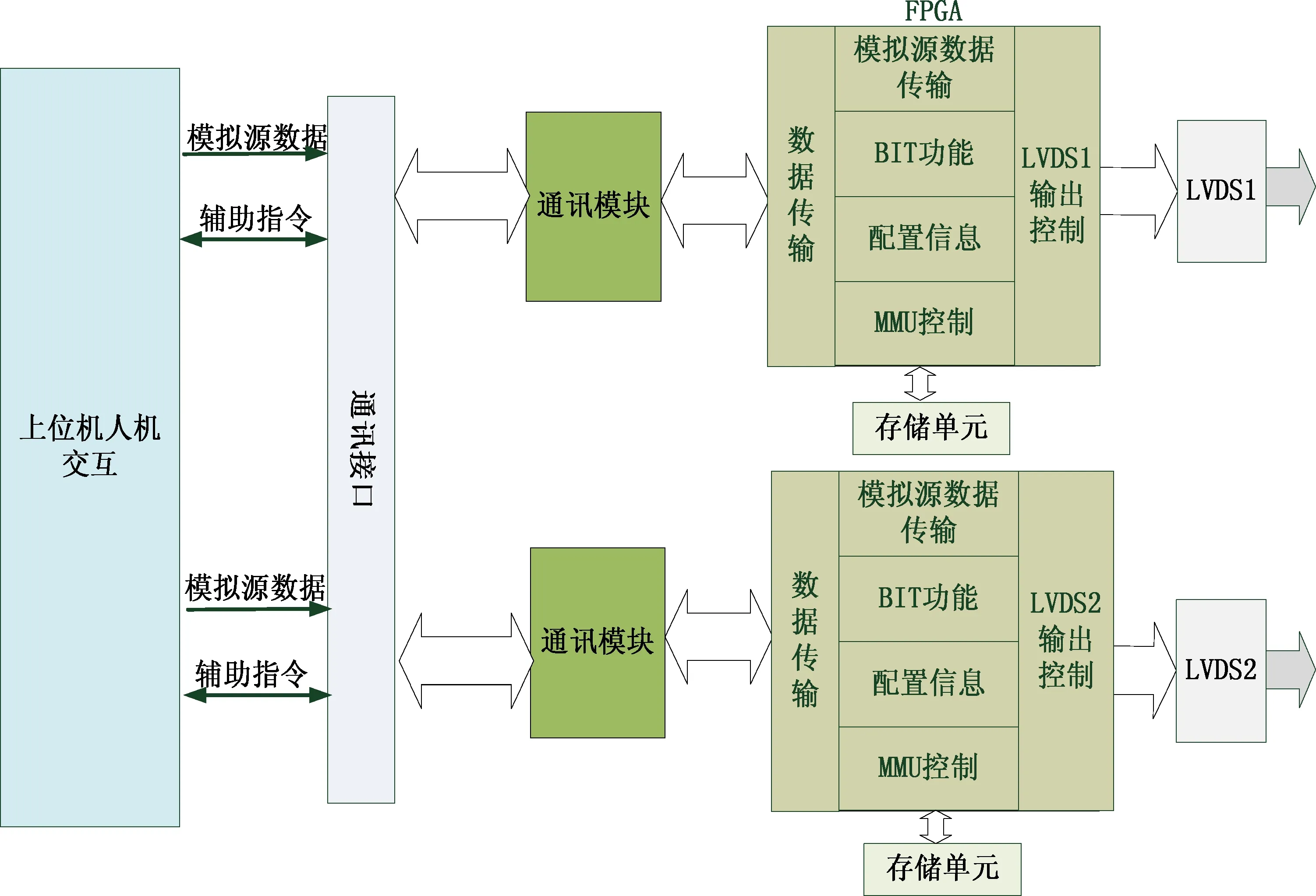

SAR数据源系统基于FPGA构建的核心嵌入式测试模块,实现了数据模拟与传输的基本功能,并支持基于该模块进行数据源时序拉偏测试。嵌入式测试模块主要包括:数据处理单元、通讯单元、输出接口单元三部分,系统硬件架构如图3所示。

图3 SAR数据源嵌入式测试模块原理

1.2.1 数据处理单元设计

数据处理单元是嵌入式测试模块的核心,该单元通过USB总线接收上位机发送的SAR载荷数据,并将数据按照上位机配置的控制参数完成数据发送,同时,可以将BIT信息反馈至上位机。数据处理单元以FPGA为基础,采用Virtex-5系列FPGA芯片XC5VLX 330T作为核心控制芯片。同时,设计DDR2内存实现数据缓冲,构成容量达1 Gbit的数据存储空间,通过FPGA的MMU控制功能,完成数据传输的缓冲功能。针对SAR载荷数据存储需求,数据处理单元采用K4T1G164QF大容量NAND FLASH完成数据存储,该芯片存储容量高达1 TB,最高访问速度可达800 Mbit/s。

1.2.2 通讯单元设计

通讯单元实现嵌入式测试模块与上位机通讯功能,上位机通过USB总线控制发送SAR数据与控制命令至嵌入式测试模块,同时嵌入式测试模块也将系统工作状态通过USB总线反馈至上位机。本系统采用CY7C68013A专用USB协议芯片实现数据传输和逻辑控制,该芯片将USB总线协议集成在专用接口芯片内部,并为用户提供简单的访问接口。采用这种方法的优势在于设计灵活,USB功能可以在任何控制器上实现,可靠性高,开发周期短,易实现,系统成本低。

1.2.3 输出接口单元设计

SAR数据源系统具备两组SAR信号输出通道,包括:CLK,DATA[15:0]、Flag、RESET;以及两组DPU信号输出通道,包括:CLK,DATA、Flag,因此根据需求共需要44路LVDS输出接口。LVDS接口芯片选用SN65LVDS31[5],该芯片具备4路LVDS接口,符合ANSITIA/EIA-644标准,且输出典型延时小于500 ps,满足本系统设计需求。

1.3 SAR数据源BIT设计

SAR数据源在每次测试之前,系统应首先进行自检。自检功能包括:FPGA健康监测,存储器BIT,输出接口BIT等。

FPGA健康监测采用心跳字的方式定时反馈FPGA工作状态。当FPGA处于正常工作状态时,以固定时间间隔,按照依次递增的规律,向主控平台发送心跳字。主控软件通过判断心跳字是否符合要求,判断FPGA的工作状态,如有异常,则设备自动报警,显示故障信息。

存储器BIT是指在系统开始工作前,按照固定规律,对存储器每一个地址进行规律数据写入。然后将数据读出。如果数据正常,则系统存储器状态符合使用要求,否则设备自动报警,显示故障信息。

输出接口BIT是针对LVDS输出接口的发送功能检测。自检时,对外输出LVDS接口与相应的BIT接口(LVDS接收电路)构成回路。发送自检命令后,通过对外输出接口发送一组固定的监测数据流,相应的BIT接口将收到的数据反馈回上位机。如果收发数据满足合格判据,则工作正常。同时,在正常工作时,FPGA对所输出数据进行监控,并将监控数据状态周期反馈至上位机,如果发送数据与所设置数据异常,则自动报警,显示故障信息。

2 钟-码拉偏设计

为了满足时间偏移测试需求,提出调用Xilinx原语IODELAY和IDELAYCTRL方式实现产生纳秒级偏移的设计方案,其中IODELAY是输入/输出延迟单元,IODELAY可以连接到ILOGIC/ISERDES或OLOGIC/OSERDES模块,也可同时连接到这两个模块。

IODELAY是具有64个tap的环绕延迟单元,具有标定的tap分辨率,64个tap的环绕延迟单元产生的延时为参考时钟(Frequency used for IDELAYCTRL)的一个周期。

钟-码拉偏功能通过基于时钟偏移的延迟单元设计、正/负向延时输出设计与正/负方向延时切换设计同时作用完成[6-7]。

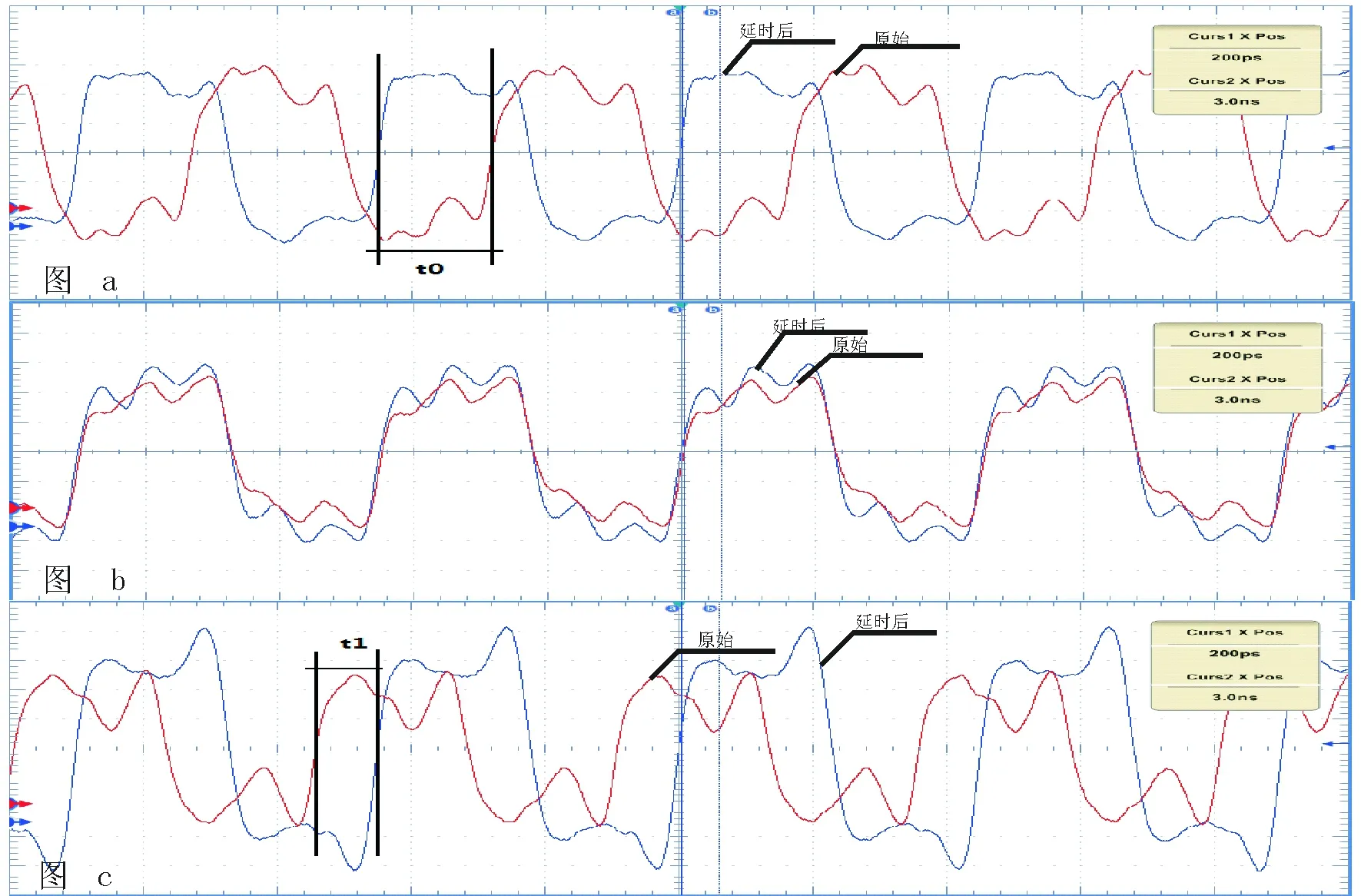

SAR数据源输出时钟实测结果如图4所示,蓝线为时钟信号偏移输出结果,红线为原始时钟信号,延时值设定为0 ns。图4(a)为原始时钟和偏移时钟对比结果(t0=8 ns),图4(b)为原始时钟和偏移时钟对比,延时值设定为-8 ns(校正0点);图4(c)为原始时钟和偏移时钟对比(t1=4 ns),延时值设定为12 ns。

图4 时序拉偏测试结果

3 SAR数据源软件设计

SAR数据源中数据处理单元软件采用Verilog HDL编程语言设计实现,本设计的编程环境是Xilinx公司推出的ISE 14.4。

图5 嵌入式控制器功能示意图

图5中,主控软件通过通讯接口将SAR数据、DPU数据、辅助指令等控制信息输入嵌入式控制模块。FPGA内部需要完成数据传输控制,MMU控制,控制LVDS接口进行SAR数据传输等工作。同时,FPGA需要完成BIT功能,将系统工作状态实时反馈给主控软件。

3.1 数据传输控制

FPGA与CY7C68013A完成数据交互,首先判断OUT FIFO空标志是否表示为空,如果不为空,则有数据到来,读取OUT FIFO中数据。FPGA对读取的数据进行解析,如果解析结果表示需要上传数据,则准备好数据,判断IN FIFO是否为满,不为满,表示可以写入数据,将准备好的数据写入到IN FIFO中。其中,OUT FIFO与IN FIFO是完成上位机与FPGA通信的数据缓冲区。

3.2 MMU控制

图6为MMU控制的程序状态机流程图。该流程图表示FPGA控制缓冲单元完成数据缓冲的整个控制流程。

图6 MMU控制的程序状态机流程图

图6中共有8个状态:IDLE,WR_S,Wr_EN,WrEnd,RD_S,Rd_EN,Get_Data,RdEnd,功能分别为:

1)IDLE:一个初始状态,复位后进入此状态;

2)WR_S:写操作开始状态,当写操作标志置位时进入此状态。将CS拉低,地址写到地址线上;

3)Wr_EN:把WE信号拉低,将数据写到数据线上;

4)WrEnd:Wr_EN持续至少12 ns后进入此状态,将CS信号拉高,将WE信号拉高,跳回IDLE状态;

5)RD_S:读操作开始状态,当读操作标志置位时进入此状态。将CS拉低,地址写到地址线上;

6)Rd_EN:将OE信号拉低;

7)GetData:从数据线上读取数据;

8)Rd_End:将CS信号拉高,将OE信号拉高,跳回IDLE状态。

3.3 嵌入式软件仿真及验证

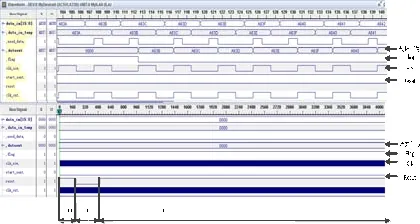

数传分系统测试中,对SAR数据源数据输出时序和DPU数据源数据输出时序有严格要求,该时序的实现主要由嵌入式控制器完成。本设计对嵌入式控制器板卡软件输出时序进行仿真验证和实验测试。图7为仿真波形,图8为系统联试实际测试结果。

图7 仿真波形

对数据处理单元软件仿真采用ISIM软件,图8中:Clk、Flag、Rest、数据输出分别指输出时钟:44.44 MHz(DPU为50 MHz)、门控信号:低有效、复位信号:低有效(DPU没有该位)、输出数据(SAR数据为16 bit;DPU数据为1 bit);时钟占空比为50%;门控信号、输出数据在输出时钟的上升沿跳变;复位信号中t0>12 500 μs,t1=2 500 μs,t2=215 000 μs。满足设计要求中:t0>400 ns,t1>500 ns,t2>300 ns的需求。

图8 嵌入式控制器输出波形

图8为采用软件ChipScope对嵌入式控制器输出波形实时采集结果,其中:Clk、Flag、Reset、数据输出分别指输出时钟(44.44MHz)、门控信号(低有效)、复位信号(低有效)、输出数据;时钟占空比为50%;门控信号、输出数据在输出时钟的上升沿跳变;复位信号中t0=1 000 μs,t1=2 500 μs,t2>15 000 μs。满足系统测试判据:t0>400 ns,t1>500 ns,t2>300 ns的指标需求。

3.4 人机交互软件设计

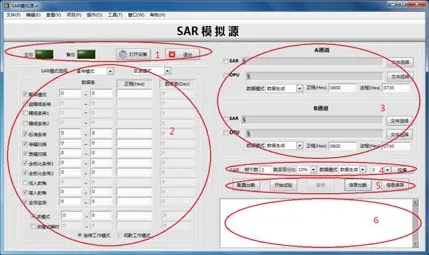

人机交互软件主要完成配置星上LVDS接口输出的数据格式,对各通道参数进行设置,选择发送模式进行数据发送,其主要功能包括:加载指定测试文件、SAR/DPU模式选择、设置工作模式参数(直传/记录/变速/恒速)、正/逆程设置、文件输出/PN码输出、SAR模式拉偏与配置信息加载、保存等功能。人机交互界面如图9所示,图中各标号区域功能如下:

图9 SAR数据源人机交互界面

1)设备操作区:打开、关闭设备,退出软件;

2)SAR模式设置区:设置SAR模式输出模式,有直传模式、记录模式可选,变速模式、恒速模式可选,可配置数据率及正程长度;

3)通道设置区:在此区域内可以对实验通道及DPU模式各参数进行设置;

4)SAR基本设置区:

在此区域内设置SAR通道实验基本参数;

5)操作区:在此区域内可完成配置加载,开始/停止试验,信息加载,信息保存等操作;

6)日志显示区:此区域内显示操作日志。

4 结束语

针对实际应用中星上载荷与数传分系统间高速数据交换的时序测试需求,依据测试信号类型进行时序控制分析,提出基于FPGA的SAR数据源设计方法,并采用IODELAY原语设计受控延时单元用于数传分系统数据传输时序测试,降低了数传分系统测试复杂度,并提高了SAR数据源系统的可扩展性。结果表明,基于校正方法降低SAR数据源内传输延时误差,满足了针对用户指标要求的星载数传分系统的钟-码拉偏测试需求,钟码拉偏调整范围达到-8 ns至8 ns,步进1 ns,CLK时钟频率最高可以达到120 MHz。