功耗分析下的密码芯片设计规范研究

邬可可 周莹 孔令晶

摘 要:密码芯片中有复杂的加解密算法和密钥保护机制,然而在计算过程中密码芯片的功率泄露却与所操作的密钥相关。攻击者利用统计学进行功率泄露分析,则可逐步解析出密码芯片所操作的密钥,从而破解整个系统。为了解决这个问题,许多抵御功耗分析攻击的安全算法与安全实现技术相继提出,但是很少有針对这一套安全防护技术设计规范的研究。文章给出了密码芯片安全算法的一套设计规范,分别基于算法设计维度规范和硬件设计维度的设计规范,来改变功率消耗的特征。这种设计规范除了能为密码芯片企业提供芯片设计的效率和安全性技术支撑外,还能指导和规范其在产品投放市场前得到系统的测试、评估和设计,免除了一旦出现安全问题后给用户和厂商带来巨额损失。

关键词:密码芯片;密码算法;功耗分析;设计规范

中图分类号:TP309 . 7 文献标识码:A

Abstract: There are complex encryption and decryption algorithms and key protection mechanisms in cryptographic chips. However, the power leakage of cryptographic chips in the calculation process is related to the key operation. The attacker uses statistics to analyze the power leak, and they can gradually resolve the key operated by the cryptographic chip, until they can crack the whole system. To solve this problem, many security algorithms and security implementation techniques against power analysis attacks have been proposed, but there is no research on the design specifications of this set of security protection technologies. This paper presents a set of design specifications for cryptographic chip security algorithms. Based on the design specifications of time dimension and amplitude dimension, the characteristics of power consumption are changed. In addition to providing technical support for the efficiency and security of chip design for cryptographic chip enterprises, this design specification can also guide and standardize the systematic testing, evaluation and design of cryptographic chip enterprises before their products are put into the market, and avoid huge losses of users and manufacturers once security problems arise.

Key words: cryptographic chips; cryptographic algorithms; power analysis; design specifications

1 引言

密码芯片大量地存在于电子产品中,比如银行卡、可信计算模块、USB Key、RFID等。一般来说,是通过增加密钥的长度来增加密码算法的安全性,而功耗分析攻击(Power Analysis)[1,2]不因密钥长度的增加而越难破解。

功耗分析是根据密码芯片的功率消耗与所执行的密码算法程序之间产生关联的中间值。因此,密码算法设计的目标,就是切断被处理的数据值与功率消耗之间的关联。国内外针对密码芯片的防御功耗分析攻击的研究[3-10],也是2019年信息安全领域的热点。研究成果大致分为算法设计维度和硬件设计维度来防御功耗分析攻击。从硬件层面防御的手段是割断密码芯片处理的中间值与功率的相关性。

Tiri和Verbauwhede提出动态差分型逻辑[6]。英国剑桥大学的Moore等人提出异步双线逻辑(Asynchronous Dual-rail)[7],这样的电路其电流特性与输入无关。算法维度防御的手段是消除密码算法与密码芯片处理的中间值之间的关联,主要是掩码技术。Mehdi-laurent Akkar和Christophe Giraud提出了掩码技术[8],该方法是将中间数据与一个随机数进行异或。李子臣和孙亚飞等人提出了基于同态特性侧信道攻击防御技术的研究[9,10]。而更高阶的功耗分析攻击出现之后,更多元化的防御技术相继提出[11~17]。

尽管国内外对功耗分析攻击防御技术的研究越来越深入,但是整体来说,在系统地研究功耗分析防御方法和进一步形成设计规范方面,还缺乏细致有深度的研究。本文将从算法设计维度和硬件设计维度,给出防御功耗分析攻击的密码芯片安全算法的一套设计规范,从而为密码芯片的功耗分析领域做好体系结构级别的安全防护。

2 背景

2.1 功耗分析

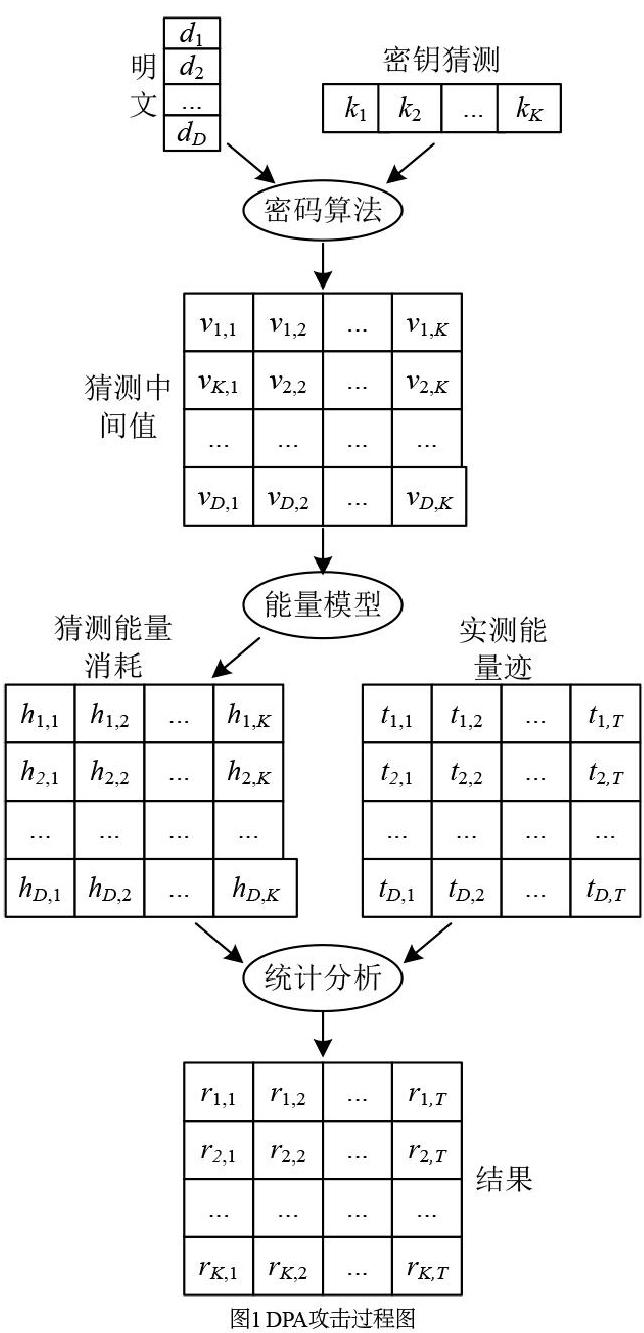

在1999年Kocher等人又提出了差分功耗分析(Differential Power Analysis, DPA)方法[4],同时把功耗分析分为简单功耗分析(SPA)和差分功耗分析(DPA)两种方式。SPA是通过对测量得到的一条或幾条侧信道曲线进行仔细观察来破解密钥。而另一种更强的DPA则采用统计的方法来执行程序多次来破解密钥,如图1所示阐述了DPA攻击的过程。

2.2 掩码和隐藏技术

隐藏技术[18]的目标即是切断处理的数据值与密码芯片功率消耗之间的联系。所以,隐藏技术使攻击者难以从功耗曲线中获得可利用的信息。

实质上,可以通过两种途径实现这一目标。第一种方法是“掩码”,使芯片对于所有操作和操作数均具有同样的功率消耗,即芯片在各个时钟周期的功率消耗相等。这种方法仅仅在算法设计维度上改变了功率消耗的特征。第二种方法是“隐藏”,使用特殊的硬件方式设计密码芯片,使其功率的消耗呈现随机化,这意味着芯片在各个时钟周期的功率消耗是随机分布的。可见,第二种方法在硬件设计维度改变了功率消耗的特征,如图2所示。

针对掩码技术,本文将从算法设计规范的维度上改变功率消耗的特征。针对隐藏技术,本文将从硬件设计规范的维度改变功率消耗的特征,从而实现体系结构级别的安全防护。

3 算法设计规范

DPA攻击需要将采集到的功率曲线进行精确地对齐才能实施有效的攻击。这意味着需要将每一个操作的功率消耗定位在各条功率曲线的相同位置。因此,算法执行的随机性越强,对设备的攻击就越困难。本文提出在随机化密码算法执行序列中插入伪操作或乱序操作。

3.1 随机插入伪操作

随机插入伪操作的基本思想是将伪操作随机地插入在密码算法执行的整个过程,并根据每一次生成的随机数,来确定在不同位置插入伪操作的数量。

在此方法的实现中,每一个操作的执行时间均取决于在该操作之前插入的伪操作的数量。在算法执行中,该数量将随机发生变化,变化越大,能力消耗的随机性就越强。同样,插入的伪操作越多,这种实现数据的吞吐量就越低。所以,必须对每一种实现都要打出一定的折扣。

3.2 乱序操作

一些密码算法的某些特定操作执行顺序是可以随意改变的,乱序操作就是在这类密码算法中,通过随机性地改变这些特定操作的执行顺序来实现的。

通过乱序操作来实现功率消耗随机化的方式与随机插入伪操作类似。但是,乱序操作的优点是并不像随机插入伪操作那样会严重地影响数据的吞吐量,其缺点是它只针对非常有限的某些密码算法中的特定操作,这严格地受限于密码算法本身以及密码算法的具体实现。因此,在现实具体的密码算法设计中,经常会把乱序操作与随机插入的伪操作结合起来使用。

4 硬件设计规范

要使得密码芯片具有防御功耗分析攻击的能力,可以通过使其各个时钟周期的功率消耗相等或者呈现随机化的样式。在上一节中,讨论了对算法设计规范的维度,提出了随机插入伪操作和执行乱序操作的方法,本节将从硬件设计的维度,提出直接改变操作功率消耗特征的技术。

4.1 时钟扰乱

时钟扰乱技术是指针对密码芯片时钟频率的随机变化,来对功耗进行扰乱的方法,为了得到更明显的功耗统计特征,应该保证所有功耗曲线的任意时间点,与其上面所进行的操作保持一致。针对这个特点,时钟扰乱技术使得功耗曲线各时间点上所发生的操作,无法实现真正的对准,故而差分统计特征无法凸显出来。时钟扰技术有两种实现方式:一种是时钟频率将被每个时钟周期来改变;另一种是随机地抹去多个等长的时钟周期中的一些时钟周期。这两种方式都将借助随机数产生器。

时钟扰乱技术的优点是,既会降低密码芯片的功耗,又会带来功耗的安全性。而时钟扰乱技术的不足之处是,在各种应用实现中,时钟加扰通常会带来少量的时间损耗,从而会影响资源有限的密码芯片的运算性能。

4.2 降低信号

其实,构建一个对于所有操作和所有操作数均具有同样功率消耗的设备并不困难。但是,当着眼于该任务的更多细节时,就会发现这并非想象中的那么简单。DPA攻击基于大量的功率曲线,所以这种攻击能够利用到功率曲线中非常微小的差异。

降低信号可以通过双轨CMOS电路,采用汉明扩展编码来实现逻辑互补电路,从而实现充放电负载的等效电容总相等。所以,这种防御措施需要以牺牲一定的功耗和硬件实现为代价。提出的做法是在对安全算法电路的反标网表进行动态功耗模拟的形式,在VLSI所采用的标准单元库中,将原标准单元替换为互补电路,并进行功耗安全性评估与设计改进,从而明显地降低芯片投片后的安全风险。

在现实中,实现这些隐藏对策的途径多种多样。但是到目前为止,只有少量的文献介绍隐藏技术的具体实现,并且更少有文献介绍隐藏技术的算法与硬件设计规范。看来隐藏技术在工业界的流行程度,要远远地高于学术界。

5 结束语

本文从算法设计规范和硬件设计规范两个维度,制定了一套密码算法的安全设计规范。这种设计规范的实施,可以提高密码芯片领域的理论和工程实践水平,让更多的集成电路企业能够意识到密码芯片算法和硬件设计规范的理论基础,研发出具有真正意义上安全的密码集成电路芯片,以提升集成电路产业的整体实力,从而更好地的保证互联网的安全。

基金项目:

1.广东省自然科学基金项目(项目编号:2018A030313746 / 2018A0303130055 / 2018A030310664);

2.深圳市基础研究项目(项目编号:JCYJ20170817114239348)。

参考文献

[1] P.C. Kocher, J. Jaffe and B. Jun. Differential power analysis [J].19th Annual International Cryptology Conference-crypto99, Lncs, Springer-Verlag Berlin Heidelberg, 1999, 388-397.

[2] J.J. Quisquater and D. Samyde. Simple Electromagnetic analysis for Smart Cards: New Results [C].Rump session talk at Cyrpto 2000.

[3] T.S. Messerges. Securing the AES Finalists Against Power Analysis Attacks [J]. Proceedings of Fast Software Encryption Workshop 2000, LNCS, Springer-Verlag Berlin Heidelberg, 2001, 150-164.

[4] T.S. Messerges. Using Second-order Power Analysis to Attack DPA Resistant Software [J]. Proceedings of Cryptographic Hardware and Embedded System (CHES 2000), LNCS, Springer-Verlag Berlin Heidelberg, 2000, 238-251.

[5] S. Chari, J.R. Rao, P. Rohatgi. Template Attacks [J]. Proceedings of Cryptographic Hardware and Embedded System (Ches 2002), LNCS, Springer-Verlag Berlin Heidelberg, 2003, 13–28.

[6] K. Tiri, I. Verbauwhede. Securing Algorithms against DPA at the Logic Level: Next Generation Smart Card Technology [J]. Proceedings of Ches 2004, LNCS, Springer-Verlag, 2004, 125-136.

[7] S. Moore, R. Anderson, P. Cunningham, R. Mullins, and G. Taylor. Improving smart card security using self-timed circuits [C].Eighth IEEE International Symposium on Advanced Research in Asynchronous Circuits and Systems, 2002.

[8] M.L. Akkar and C. Giraud. An Implementation of DES and AES, Secure against Some Attacks [J]. Proceedings of Ches 2001, LNCS, Springer-verlag, 2001, 309-318.

[9] 李子臣,孫亚飞,杨亚涛,梁斓,汤永利.一种抗侧信道攻击的随机功耗方法[J].计算机应用与软件,2018,35(03):299-303.

[10] 李子臣,孙亚飞,杨亚涛,梁斓,曹广灿.一种改进的R-LWE同态掩码方案[J].计算机应用研究,2019,36(01):243-245.

[11] M.K. Lee, J.E. Song, D. Choi, D.G. Han. Countermeasures against power analysis attacks for the NTRU public Key cryptosystem [J]. IEICE Transactions on Fundamentals of Electronics, Communications and Computer Sciences, 2010.

[12] E. Prouff, T. Roche. Higher-order Glitches Free Implementation of the AES Using Secure Multi-party Computation Protocols [J]. Proceedings of Ches 2011, Lncs, Springer-Verlag, 2011.

[13] P. Weibo, P William, A. Marnane. Correlation Power Analysis Attack against Tate Pairing on FPGA [C]. ARC 2011.

[14] R. Velegalati, J.P. Kaps. Improving Security of SDDL Designs through Interleaved Placement on Xilinx FPGAs [C]. International Conference on Field Programmable Logic and Applications, 2011.

[15] C.Y. Lu, S.M. Jen, C.S. Laih. A General Framework of Side-channel Atomicity for Elliptic Curve Scalar Multiplication [J]. IEEE Transactions on Computers, 62(3), 2015, 428–438.

[16] K. Wu. Flexible Parallel Computing for Elliptic Curve Scalar Multiplication with Resistance against Simple Side-Channel Attacks [J]. Journal of Computers (Taiwan), Vol. 28, No. 6, December, 2017, 64-78.

[17] M. Tang, Z. Qiu, Z. Guo, etal. A Generic Table Recomputation-based Higher-order Masking [J]. IEEE Transactions on Computer Aided Design of Integrated Circuits and Systems, 2017.

[18] S. Mangard, E. Oswald, T. Popp. Power Analysis Attacks: Revealing the Secrets of Smart Cards[J]. Springer Science Business Media, 2007.