CMOS电路场区抗辐照加固工艺研究

马仲丽

(中国电子科技集团公司第四十七研究所,沈阳110032)

1 引言

随着CMOS电路在航空航天及特殊环境下的广泛使用,其电离辐射效应越来越引起人们关注[1]。电离辐射使CMOS电路的输出电压下降、最大输出电流降低,静态漏电流增大,引起器件性能严重下降甚至失效[2]。为提高电路的抗辐射性能,业界已在设计和工艺等多方面对电路进行加固处理[3-5]。在工艺方面,随着对CMOS电路抗辐射性能的要求越来越高,常规加固工艺有时已经不能满足要求[6],对某些工艺的进一步优化已势在必行。

根据电离辐射机理,氧化层在电离辐照过程中累积的正电荷将引起阈值电压的漂移,导致电路中漏电流增大和功能失效[7]。辐照中累积的正电荷与氧化层厚度成正比。我们在常规加固电路中虽然对场区从设计和工艺上进行了加固,提高了场区寄生晶体管的开启电压[8],但由于电路中场氧化层比栅氧化层厚度要大一个数量级以上,因此辐照引起的阈值电压漂移还会使场寄生管导通而引起漏电流增大。

常规场加固方法中,设计上采用环形栅及P+保护环等手段虽能够提高场区的抗辐射性能,但由于芯片面积及电路速度方面的原因,并不适于大规模集成电路的制造。在工艺上,经常采用的方法是降低场氧化层的厚度及改变热氧化工艺的条件,但漏电流依然很大,场区加固的效果不尽如人意[9]。

研究表明,场介质的选择对场区的抗辐射性能有很大影响[10],选择合适的场介质能够进一步提高场区加固。采用二氧化硅与氮化硅复合场介质制造工艺,提高了电路的抗电离辐射性能。

2 场区电离辐照失效机理

场区在CMOS电路中承担着器件隔离的作用,其氧化层厚度一般比栅氧化层大一个数量级以上。在辐照环境中,由于电离辐照损伤与氧化层厚度成正比,所以场区的厚氧化层在电离辐照后产生的辐照电荷比栅氧化层大很多,对隔离性能的影响非常严重。对于P沟场寄生管,阈值电压升高,隔离特性不受影响;而对于N沟场寄生管,电离辐照产生的阈值电压漂移使场阈值电压降低,因此N沟场管的隔离特性在辐照后将迅速失效。

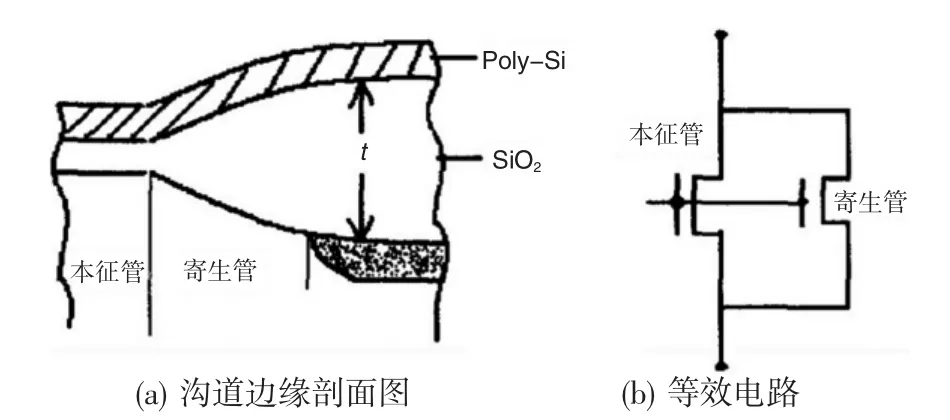

同时,场区辐照的另一重要后果是引起NMOS器件的沟道边缘寄生漏电。图1为MOS器件沟道边缘剖面图及其等效电路。可见栅氧和场氧间有迅速增厚的鸟嘴过渡区,电离辐照损伤将随着鸟嘴区氧化层的增厚迅速增加,导致该区域的硅表面比栅中部区域提前反型,该区域的反型电子为NMOS器件的源漏间增加了一条通路,造成源漏寄生漏电。因此,在N衬底与N+区之间形成的实际上是一个寄生场效应晶体管,由于场氧厚度较大,辐射损伤正电荷较多,通常其漏电流会显著变大。

图1 MOS器件沟道边缘的剖面图及其等效电路

可将寄生管看成是一个与本征MOS器件并联的器件,实际MOS器件辐照后的源漏电流可表示为:ID实际=ID本征+ID寄生。由于鸟嘴区氧化层中的辐照正空间电荷比栅氧化层中的辐照正空间电荷大得多,寄生管的阈值电压就比本征管低得多,于是在同一栅压下,寄生管与本征管的工作点也将不同。当本征管还处在亚阈值区时,寄生管的工作点已经在饱和区甚至线性区,这样电流主要从寄生管流过,导致漏电流增加。

3 试验方法、数据及讨论

为研究复合场介质的抗辐照加固性能,在常规加固工艺的基础上,进一步改变场介质条件,采用SiO2与Si3N4复合场介质替代热生长场SiO2层,并比较不同场介质工艺条件下电路在辐照前后漏电流的变化率。

试验电路选取了了两种54系列的抗辐照加固电路:电路A及电路B。为便于对比,试验样品分别采用了三种不同的场介质工艺,分别为:

工艺a:常规加固场氧化层(676.9nm);

工艺b:复合场介质SiO2(402.3nm)+Si3N4(193.6nm);

工艺c:复合场介质SiO2(516.6nm)+Si3N4(96.5nm);

其中SiO2采用 1000℃、H2/O2合成工艺,Si3N4采用380℃、PE Si3N4工艺。

除场介质工艺不同外,电路加工工艺流程中的其他条件完全相同。在加工完成后,对这两种电路进行辐照试验,辐照源采用沈阳军区军事医学研究所钴60源,剂量率为1Gy(Si)/s。记录各样品辐照后漏电流的数值,并与其辐照前漏电流数值进行对比,计算漏电流变化率。

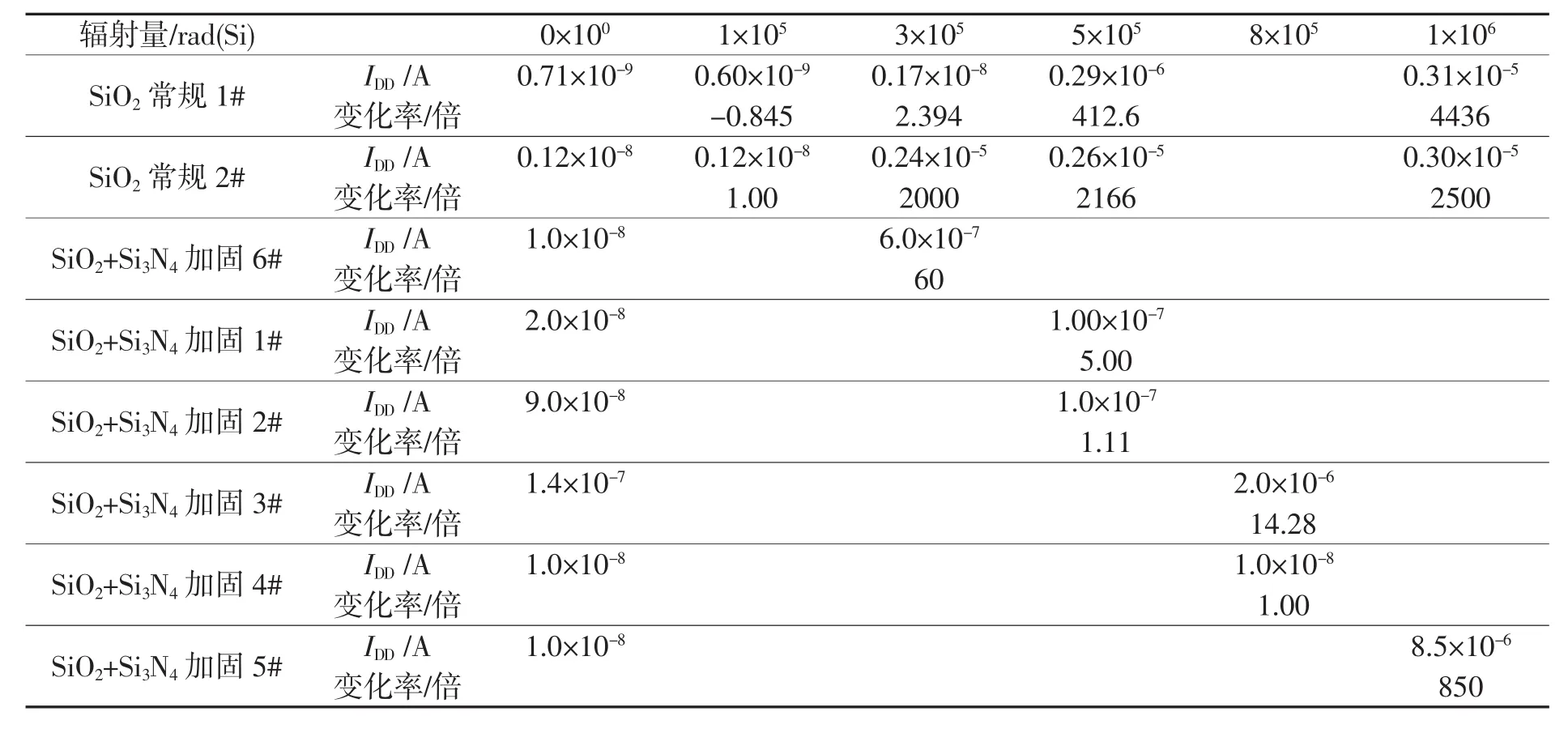

电路A各试验样品的场介质工艺条件分别为:常规1#~2#采用工艺a、加固1#采用工艺c、加固2#~6#采用工艺b。试验数据见表1。

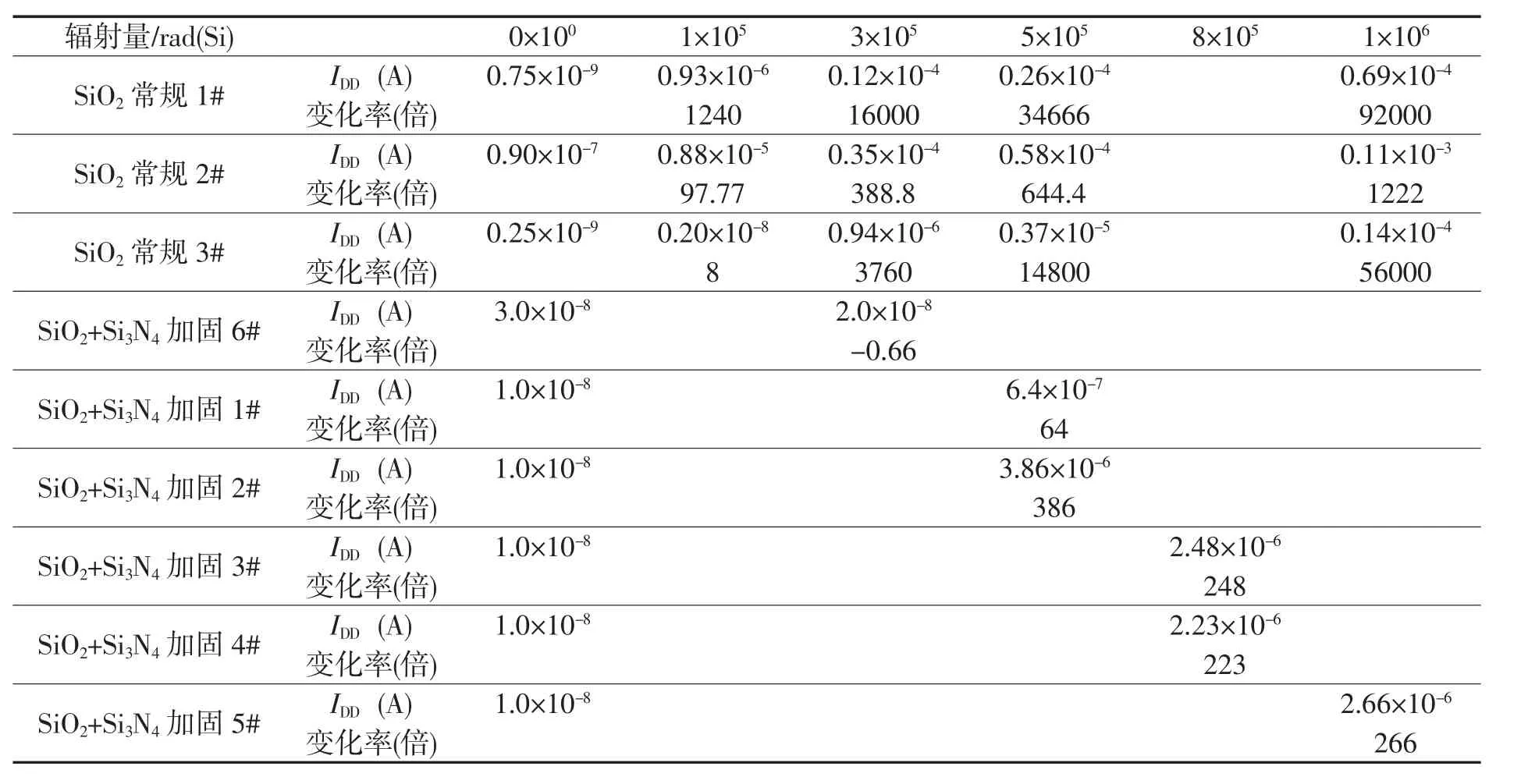

电路B各试验样品的场介质工艺条件分别为:常规1#~3#采用工艺a、加固1#~6#采用工艺b。试验数据见表2。

对比不同场介质条件下的试验数据,我们可以看到,电路A采用SiO2+Si3N4复合场介质后,辐照引起的IDD变化比单纯采用场氧化层时减小了2个数量级以上;电路B采用SiO2+Si3N4复合场介质后,辐照引起的IDD变化比原来单纯采用场氧化层时减小1~2个数量级,两种电路的抗辐照性能都得到了明显的改善。因此可以得出结论,采用二氧化硅与氮化硅复合场介质能够有效抑制辐照引起的漏电流增大,是一种有效的场区加固方法,提高了电路的抗电离辐射性能。

另外,试验中SiO2与Si3N4厚度的比例是一个需要注意的问题。本次试验也曾同时进行了SiO2(125.2nm)+Si3N4(420.4nm)条件下的试验,但在去除有源区氮化硅时,SiO2全部损耗掉,试验无法继续进行。因此,虽然SiO2层厚度的降低有助于提高电路的抗电离辐射性能,但仍要保证场氧层的厚度。另外,为避免硅片发生龟裂,PE Si3N4厚度导致的应力问题也是需要考虑的因素。遗憾的是,由于时间及条件所限,本次试验并没有将找到最佳工艺条件作为试验目标,因此没有给出工艺最优化条件。

表1 电路A不同场介质辐照后IDD数据

表2 电路B不同场介质辐照后IDD数据

4 结束语

通过对CMOS电路场区电离辐照失效机理的分析,给出了一种场区抗辐照工艺新方法。在常规加固工艺基础上,采用了SiO2与Si3N4复合场介质工艺代替传统的单一热氧化工艺,并对电路进行了辐照试验。从试验数据上看,复合场介质工艺明显降低了辐照导致的电路漏电流,是一种有效的场区抗辐照工艺方法。