基于现场可编程门阵列的差分四相相移键控调制解调算法设计

王晨 潘建国 郑振东 王芳

摘 要: 以软件无线电技术为基础,针对差分四相相移键控(DQPSK)调制解调系统设计了全新的算法,实现了现场可编程门阵列(FPGA)平台下的DQPSK全数字调制解调,并可通过软件编程进行电路升级.与传统DQPSK调制解调电路相比,不但缩减了印制电路板(PCB)的尺寸,而且可以在不改变电路的情况下升级调制解调算法,从而降低了硬件升级、算法调整的成本.以Intel的Quartus II软件作为验证平台,用Verilog HDL语言实现了各个模块功能的设计,采用ModelSim软件进行功能仿真,验证算法的正确性.系统运行频率达到132 MHz,达到了预期要求.

关键词: 差分四相相移键控(DQPSK); 调制解调; 现场可编程门阵列(FPGA)

中图分类号: TP 332.1 文献标志码: A 文章编号: 10005137(2019)04036205

Abstract: Based on software radio technology,this paper designs a new algorithm for differential quadrature reference phase shift keying (DQPSK) modulation and demodulation system,realizes DQPSK full digital modulation and demodulation on the platform of field programmable gate array (FPGA),and upgrades the circuit through software programming.Compared with traditional DQPSK modulation and demodulation circuit,it not only greatly reduces the size of printed circuit board(PCB),but also can change and upgrade the modulation and demodulation algorithm without changing the circuit,thus reducing the cost of hardware upgrade and algorithm adjustment.Intels Quartus II software is used as the verification platform,Verilog HDL language is used to realize the functional design of each module,and ModelSim software is used to carry out functional simulation to verify the correctness of the algorithm.The operating frequency of the system reaches 132 MHz,which satisfies the expected requirement.

Key words: differential quadrature reference phase shift keying (DQPSK); modulation and demodulation; field programmable gate array (FPGA)

0 引 言

数字调制解调技术在高速数据通信中起着至关重要的作用,而差分四相相移键控(DQPSK) 调制解调系统因其频带利用率高和抗干扰能力强的特点,被广泛应用于现代通信系统中.国内外学者都在深入研究全数字DQPSK调制解调系统,不断地研发出新的专用芯片[1].可是,专用芯片的设计目的基本都是针对某一特殊应用场景实现某一特定用途的,推广应用范围有限.

现场可编程门阵列(FPGA)作为一种半定制电路,克服了原有可编程器件门电路数有限的缺点,弥补了定制电路的不足.随着集成电路密度的不断提高,FPGA可以胜任几乎所有数字器件的功能設计.通过软件仿真,可以在制板之前就先验证设计的正确性.而在完成印制电路板(PCB)的设计之后,依然可以对系统进行在线修改,不必改动硬件电路.FPGA较传统电路优势明显,其现场编程能力可以用来对系统进行升级、除错,并延长产品寿命.因此,在现代通信技术中得到快速发展,并在数字通信领域得到广泛应用[2].

本文作者采用FPGA平台设计了一个DQPSK调制解调系统,利用FPGA的在线编程和动态可重构性,根据自身需求和应用场景的要求来设置硬件参数,从而使整个通信系统都具有可定制性,在设计完成后,依然能够对所有参数按需求进行在线动态修改.

1 DQPSK调制解调

1.1 DQPSK调制原理

四相移相键控(QPSK)的原理是利用4种不同的载波相位来表征4种数字信息[3-4].为了消除接收机对信号进行相干解调时产生的相位模糊[5-6],需要对四进制数据进行差分编码,构成DQPSK[7].

DQPSK调制技术利用前后码元的相对相位变化关系来表示信息[8],所得码元与载波的相位变化关系与QPSK调制类似,两种调制方式的功率谱密度相同,区别仅仅在于QPSK调制的相位是绝对相位,DQPSK调制的相位是相对相位.

1.2 DQPSK解调原理

采用相干检测法对QPSK信号进行解调,利用2个相互正交的本地参考载波对2个二相信号分别进行相干解调[9].解调之后得到的两路并行码元,经过一个并/串变换电路后,作为串行数据输出.解调完成后,将相对码再转换为绝对码,恢复出原始的基带信号,这个过程称为逆码变换.与发送端的编码器功能相反,接收端需要设计一个差分解码器.因此,DQPSK的解调可视为在QPSK解调过程之后,再加入一个逆码变换.

在误比特率相同的情况下,相比QPSK解调,DQPSK解调需要增加约2 dB信号功率,解调性能略差,但是DQPSK解调不需要本地参考载波,不存在相位模糊的情况,较易实现,因此广泛应用于信噪比较高的场合.

2 基于FPGA的DQPSK调制解调算法设计

2.1 设计思路

首先设计各个子功能模块,如串/并(并/串)转换模块、差分编解码模块、低通滤波器模块、數字振荡器(NCO)模块、乘法器模块、鉴相器模块等,根据模块的具体功能选择采用硬件描述语言Verilog HDL进行编写或者直接进行知识产权(IP)核调用.再根据电路需求将各个子模块进行功能整合,分别完成码型变换、QPSK调制、极性Costas环、位同步环等功能设计.最终通过顶层控制模块将其整合为DQPSK调制和解调两大功能,完成整个算法设计.

2.2 DQPSK调制的FPGA设计

DQPSK调制器的内核是2个乘法器.差分编码器输出的两路数据与NCO产生的载波相乘.两路载波的相位是正交的,分别称为同相I支路和正交Q支路.调制后的两路信号再进行叠加,就可以得到DQPSK调制信号.

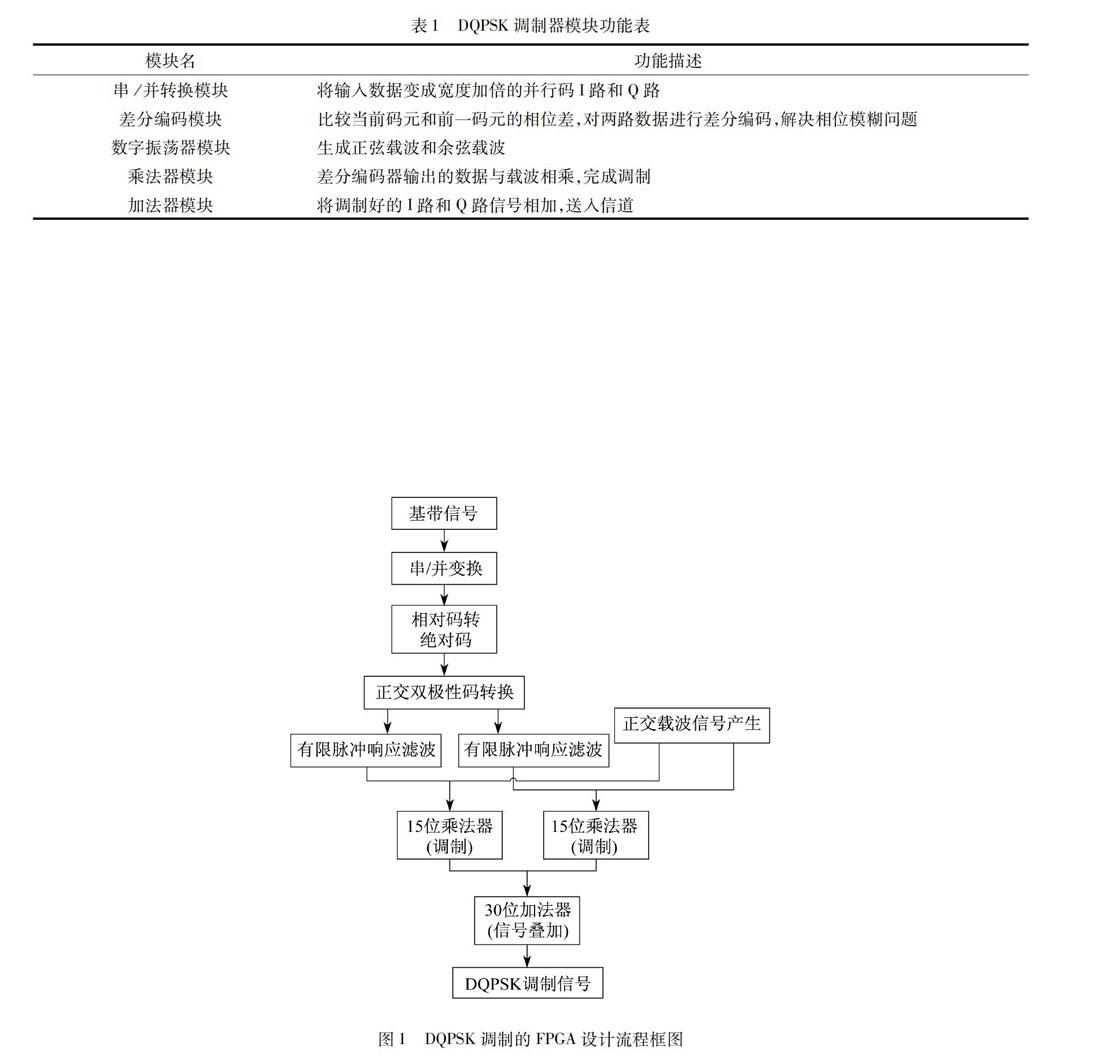

DQPSK调制器的模块和功能如表1所示.

由于要对基带信号进行成型滤波,采用直接调相法产生DQPSK信号.DQPSK调制算法的设计参数为:基带成型滤波器滚降系数α=0.8;符号速率R=1 Mbit·s-1(此处指四进制数据,每个符号代表两位二进制数据);输入数据速率(采样速率和FPGA系统时钟频率)fs=8R=8 Mbit·s-1;载波信号频率fc=2 MHz;输出数据位宽B=16.

DQPSK调制的FPGA设计流程框图如图1所示.图1中的输入信号为待调制的基带信号,采用小端模式的串行二进制数据,包括调制电路所需的时钟信号及全局reset信号作为输入数据;输出即为并行的DQPSK调制信号dout,可直接用于后级的信号发送单元.

采用Verilog HDL设计码型变换模块,完成输入单比特数据的串/并转换、差分编码、双极性码变换这几项功能模块的编写设计,可调用系统已有的IP核实现其他模块,如数字振荡器、成型滤波器、乘法器等,这样不仅能够减少工作量,提高效率,还可以保证设计的性能.

2.3 DQPSK解调的FPGA设计

从接收端来看,由于接收到的信号一般为高频信号,需要先对信号进行下变频处理.为了能够恢复出原始信号的特征,还需要进行位定时同步和载波同步.经过同步的信号再通过抽样判决、差分解码和并/串转换等步骤还原出原始信号.

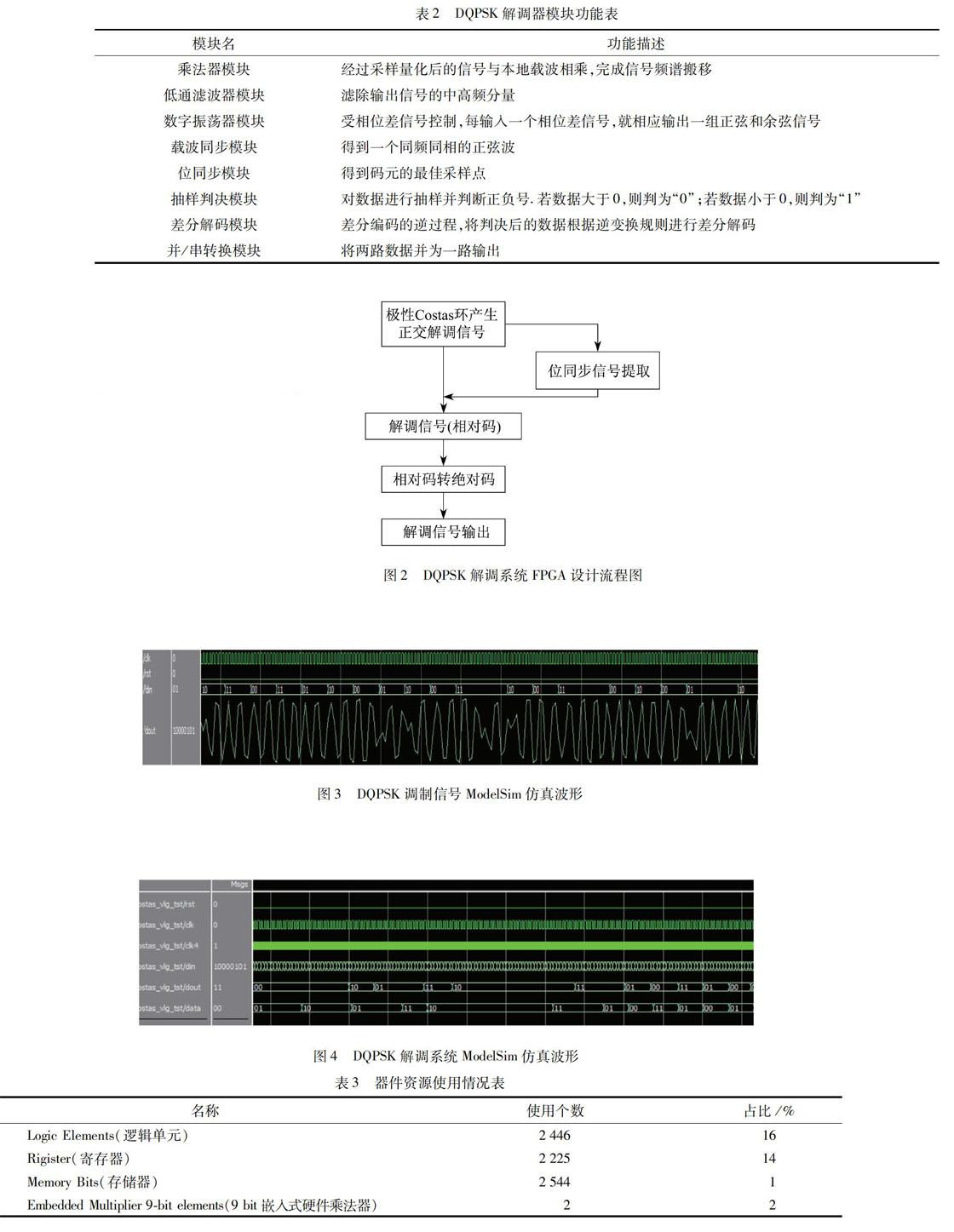

DQPSK解调器主要模块构成和功能如表2所示.

要组成一个完整的DQPSK解调系统,需要极性Costas环完成相干载波的提取,并产生正交、同相支路的基带波形[10-11],需要进行位同步,需要进行差分解码.在对各个子模块进行设计的基础上,解调系统只需给出一个顶层文件,将各个模块通过组件以实例化的形式连接起来,并增加一些逻辑电路处理.解调系统的FPGA设计流程如图2所示.

3 仿真与结果分析

本设计采用ModelSim仿真软件,该软件提供了友好的仿真环境,集成了性能分析、波形比较、代码覆盖、数据流、信号检测(signal spy)、虚拟对象(virtual object)、Memory窗口、Assertion窗口、源码窗口显示信号值、信号条件断点等众多调试功能.

对调制系统进行仿真测试,FPGA平台下的DQPSK调制信号dout输出如图3所示.由图3可见相邻码元的相位变化.

DQPSK解调在FPGA平台下的ModelSim仿真波形图如图4所示.从图4可以看出,在载波同步环和位同步环都趋于稳定后,DQPSK解调后的输出与输入相比,较为一致,仅存在一些信号处理过程中产生的延时差异.

完成综合实现后,工作过程区中自动显示整个设计所占用的器件资源情况.本设计选用的目标器件是Altera公司的Cyclone IV系列器件EP4CE6E22C8.器件资源使用情况如表3所示.

4 结束语

本文设计了一个基于FPGA的数字调制解调算法,首先对数字调制解调系统中的DQPSK调制解调原理进行了理论分析,在算法设计中,分别完成了差分编解码器、DQPSK调制、极性Costas环和位同步环的构建,并通过顶层文件将各子模块功能整合为基于FPGA的DQPSK的调制解调算法.本设计仅通过软件升级就达到了整体电路升级的效果,具有一定的参考价值.

参考文献:

[1] 郭天赐.数字调制与解调技术的研究 [J].河南科技,2016(5):41-42.

GUO T C.Research on digital modulation and demodulation technology [J].Journal of Henan Science and Technology,2016(5):41-42.

[2] 段程鹏.测控通信中QPSK调制解调技术的设计与实现 [D].西安:西安电子科技大学,2014.

DUAN C P.Design andimplementation of QPSK demodulation in measurement and control communication [D].Xian:Xidian University,2014.

[3] 楼才义,徐建良,杨小牛.软件无线电原理与应用 [M].2版.北京:电子工业出版社,2014.

[4] WILSON S G.Digital Modulation and Coding [M].New York:Publishing House of Electronics Industry,1998.

[5] 沈连丰,叶芝慧.信息论与编码 [M].北京:科学出版社,2004.

[6] 梅平.QPSK调制解调器的研究与设计 [D].成都:电子科技大学,2008.

[7] 樊昌信,曹金娜.通信原理 [M].7版.北京:国防工业出版社,2015.

[8] 陈铖.高速数字调制解调器的设计与实现 [D].南京:南京理工大学,2010.

[9] 王兴亮.数字通信原理与技术 [M].西安:西安电子科技大学出版社,2003.

[10] SHAMLA B,DEVI G K G.Design and implementation of Costas loop for BPSK demodulator [C]//2012 Annual IEEE India Conference.Kochi:IEEE,2012:785-789.

[11] 钟钧波,章坚武,包建荣.QPSK调制解调系统设计及FPGA实现 [J].杭州电子科技大学学报,2014(2):60-64.

ZHONG J B,ZHANG J W,BAO J R.Design and FPGA implementation of QPSK modem system [J].Journal of Hangzhou Dianzi University,2014(2):60-64.

(责任编辑:包震宇)