一种多重触发式炮口冲击波存储测试系统设计

范少波,王代华,赵志国,郭 晋

(1.中北大学 仪器科学与动态测试教育部重点实验室, 太原 030051; 2.中北大学 电子测试技术国家重点实验室, 太原 030051;3.晋西工业集团有限责任公司防务装备研究院, 太原 030051)

炮口冲击波是各炮口气流现象中危害最大的一种[1-2],了解炮口冲击波,尤其是火炮连发射击时产生的炮口冲击波的发生规律,成为了火炮研制中的重要一环[3]。为全面评估炮口冲击波对周遭设备与操作人员的危害,国内外相关领域的专家已经做了大量研究与试验。现有炮口冲击波测试方法大体上可分为以下两类:引线测试法与存储测试法[4-5]。存储测试法较引线测试法来说,操作更加简洁,数据捕获率也更高[6],但现有的存储测试系统受限于其触发及存储特性,大多只能进行单次触发、单次测试[7]。面向多次重复试验时,需频繁地对测试系统进行读数和上下电操作,时间周期长,效率不高[8]。加之现有的炮口冲击波试验多有连发测试需求,射击过程强度大、效率高[9],单次触发的测试系统难以满足当下的测试需求。针对上述问题,本文设计了一种基于多重触发技术的炮口冲击波存储测试系统,通过系统内置实时时钟,将每次的触发时间与冲击波信号对应,通过合理的FLASH存储区域规划及地址分配,实现了负延时数据长度与正向数据长度可编程,使存储式炮口冲击波测试系统得以满足火炮的连发测试需求。

1 系统总体方案

本方案在以往冲击波测试要求基础上,针对炮口冲击波连发测试需求,测试系统设计增加多重触发功能。系统的数据长度、可触发次数、负延时长度、滤波器带宽、增益倍数以及触发电平等参数可由上位机进行编程设置。系统响应时间≤1 μs,采样精度≥16 bit。系统触发之后的数据存储到FLASH存储器中,通过上位机读取系统状态可获取当前系统的各项参数以及当前触发次数。

多次触发炮口冲击波测试系统原理如图1所示,系统由传感器、数据记录仪以及主控制台组成。传感器在感受到压力信号之后,将压力信号转换为电压信号传输给数据记录仪,数据记录仪将电压信号进行信号调理、模数转换,最终存储到FLASH存储器中。与此同时,FPGA从实时时钟获取到冲击波信号触发时间,与冲击波信号一并存入FLASH中,用于甄别触发次数与触发时刻是否一致。最后,存入FLASH中的数据由USB接口或ZigBee无线通信模块读取到上位机中。

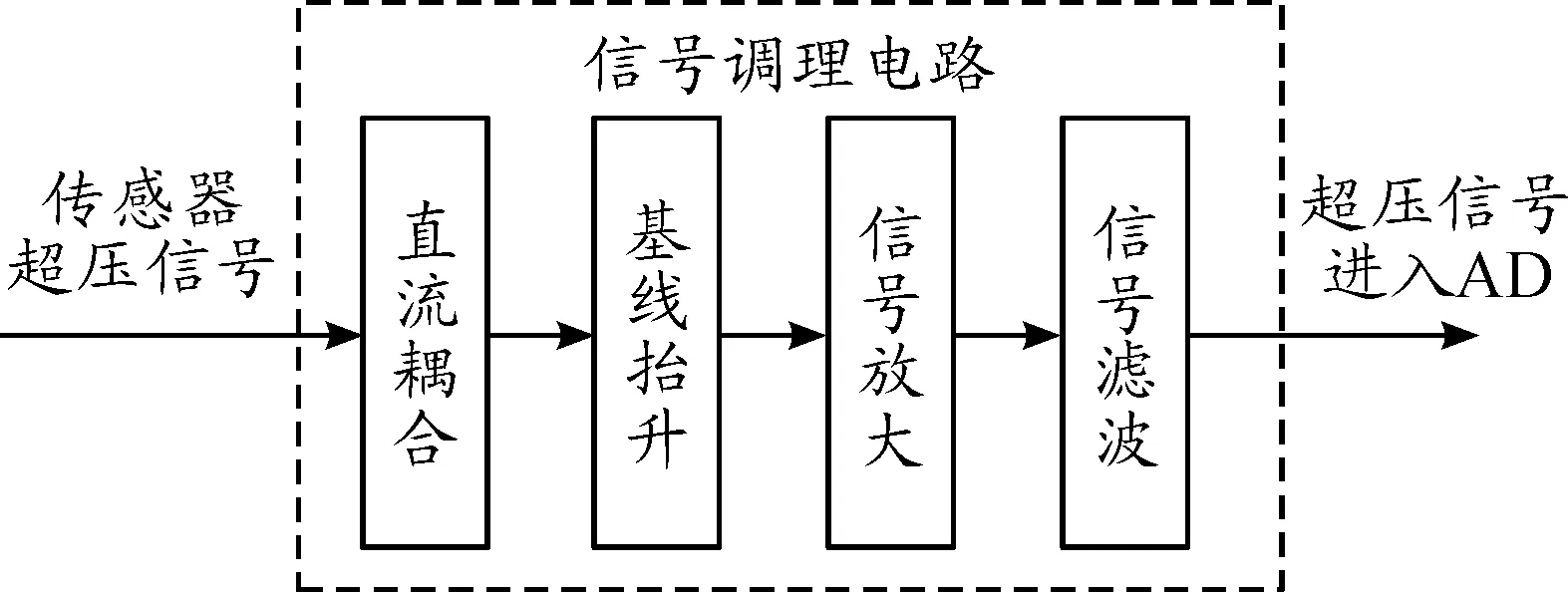

信号调理电路用于将传感器传输过来的冲击波信号进行直流偏置消除、信号放大、基线抬升以及噪声滤除。其原理如图2所示。现有的冲击波测试系统中消除ICP传感器直流偏置通常使用的是电容交流耦合的方法,但此方法势必会影响冲击波信号的低频特性[10]。本设计采用直流耦合方式,利用数控电位器与仪表放大器配合消除传感器输出的直流偏置电压,可保证系统的低频特性[11]。之后冲击波信号经加法器抬升基线,后经过程控放大器与程控滤波器送入模数转换器。

图1 系统原理框图

图2 信号调理框图

采集存储电路负责将信号调理电路输出的冲击波信号进行模数转换,并根据系统判读的当前触发次数将冲击波信号以及从实时时钟读取的时间信息一并存入FLASH存储器。其原理如图3所示。

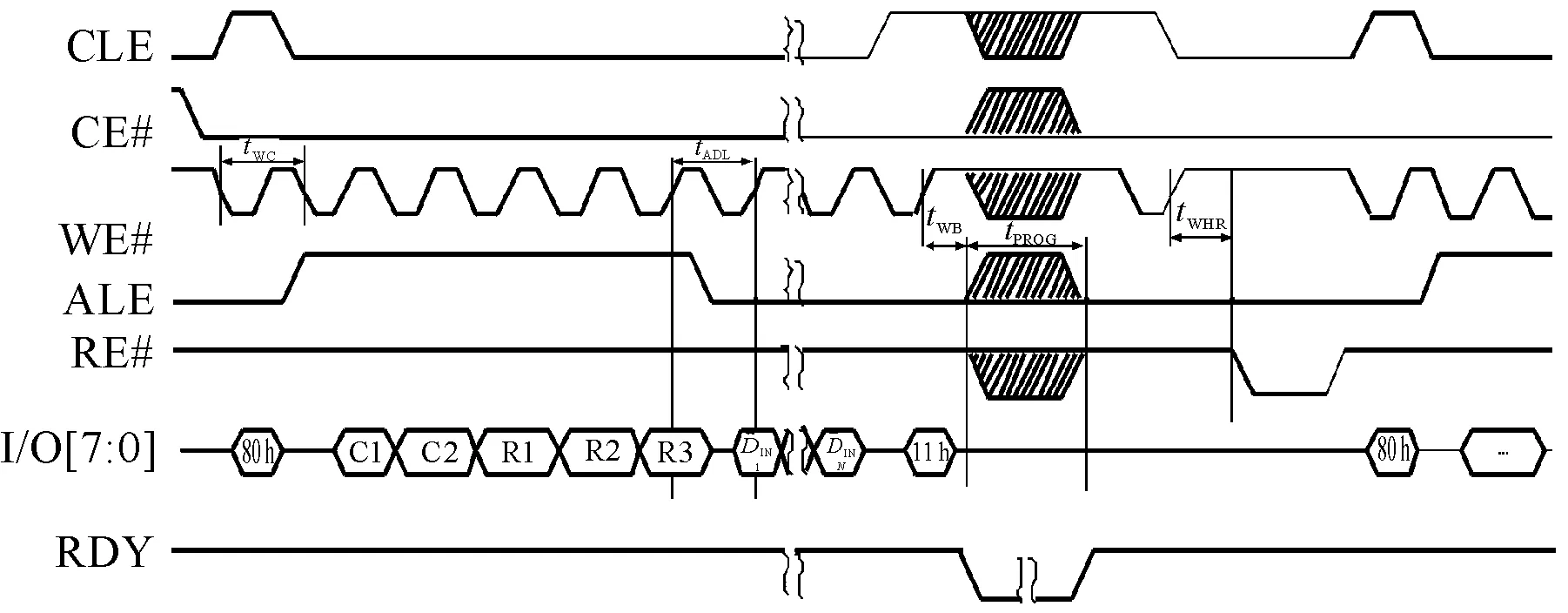

图4 AD并行接口时序

FLASH存储器选用Micron公司的NAND型FLASH。冲击波信号经模数转换之后进入FPGA,由FPGA通过FIFO缓冲后根据触发次数按预先设定的存储地址存入FLASH存储器中,与此同时FPGA读取到实时时钟内的时间信息,同冲击波数据一并存入FLASH。在需要读取相应触发次数的冲击波数据时,通过上位机发送读数指令,把对应存储区域的数据和时间信息一并读出。本设计中FLASH数据写入采用双plane页编程操作,其时序如图5所示。

图5 FLASH双plane页编程时序

FLASH存储器由FPGA进行控制,在工作过程中通过合理的状态划分以及状态跳转条件选取使得FLASH的多重触发和多段存储可以有条不紊的进行,图6为FPGA控制状态机示意图。

2 多重触发关键技术

2.1 存储区划分

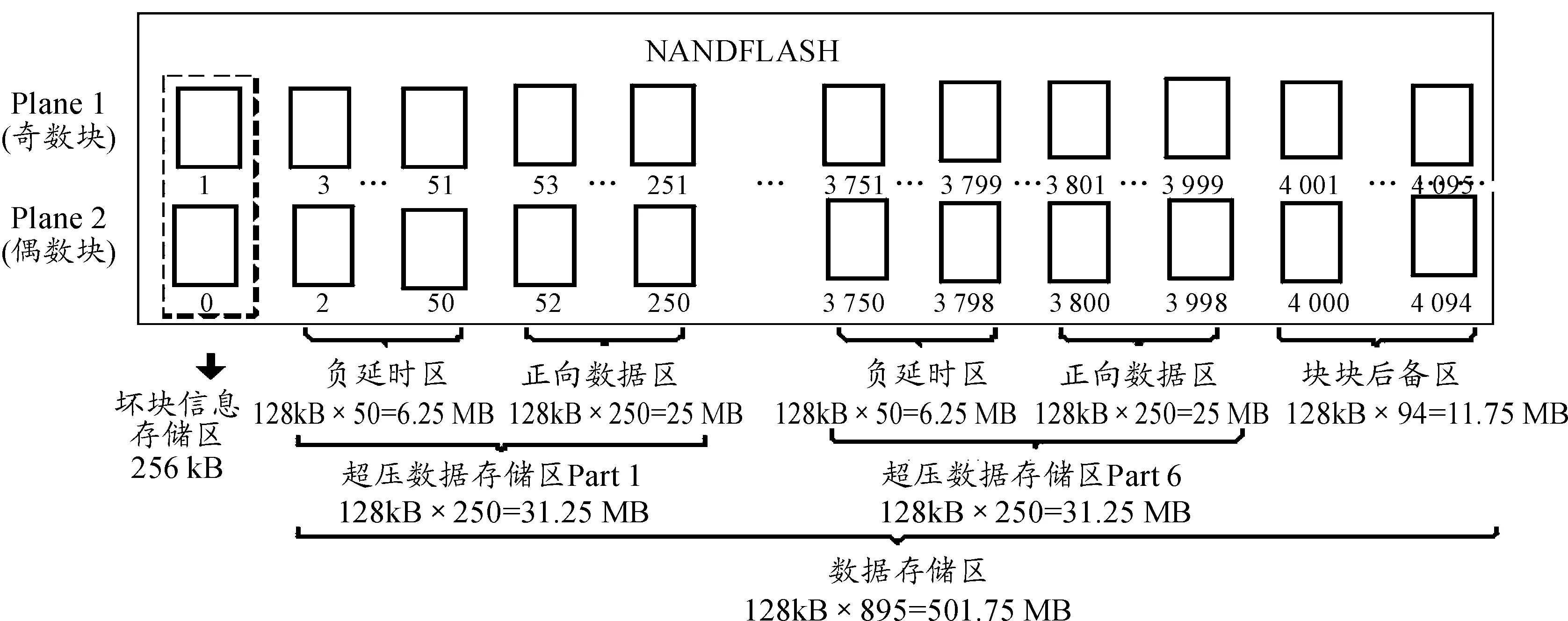

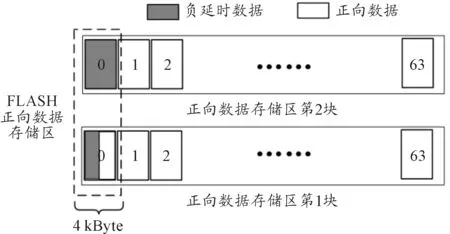

综合考虑存储容量与存储器结构,最终所选用的FLASH芯片为Micron公司的4GbNAND型FLASH,其存储容量512 MByte,整片FLASH共分2个planes,每个plane拥有2 048个blocks,每个block拥有64个pages,每个page可存储2 kByte数据。为提高FLASH的读写速率,采用两个plane同时读、写、擦除的方式对FLASH进行操作,因此在存储区域设计时需将“双块页”作为读、写操作的最小单元,将“双块”作为擦除操作的最小单元。为了实现多次触发,记录多次冲击波数据,首先需要对FLASH存储器进行合理的分区,在系统触发之后按照触发次数将冲击波数据存入对应的存储区域,FLASH存储分区示意图如图4所示。由于生产工艺的限制,FLASH出厂后本身会不可避免的带有坏块,但其坏块总量最多不会超过80块,为方便存储区域管理以及保证逻辑地址的连续性,除去需要使用的存储区域之外,在FLASH中提前预留了坏块后备区作为存储区域出现坏块后的备选块[12]。剩下的区域中前两块作为坏块信息存储区,其余部分分为n个冲击波数据存储区域,每个区域又分为负延时存储区与正向数据存储区域。系统可根据不同的n值来分配更改存储区域,实现系统触发次数可编程。但在更改系统可触发次数的同时,系统数据长度的上限也随之改变,在参数设置时需加以注意。图7以n=16为例对FLASH存储区进行划分,其中每个冲击波数据存储区域为31.25 MB,每个区域又分为6.25 MB的负延时存储区与25 MB的正向数据存储区。

图6 FPGA控制状态机

图7 FLASH存储分区

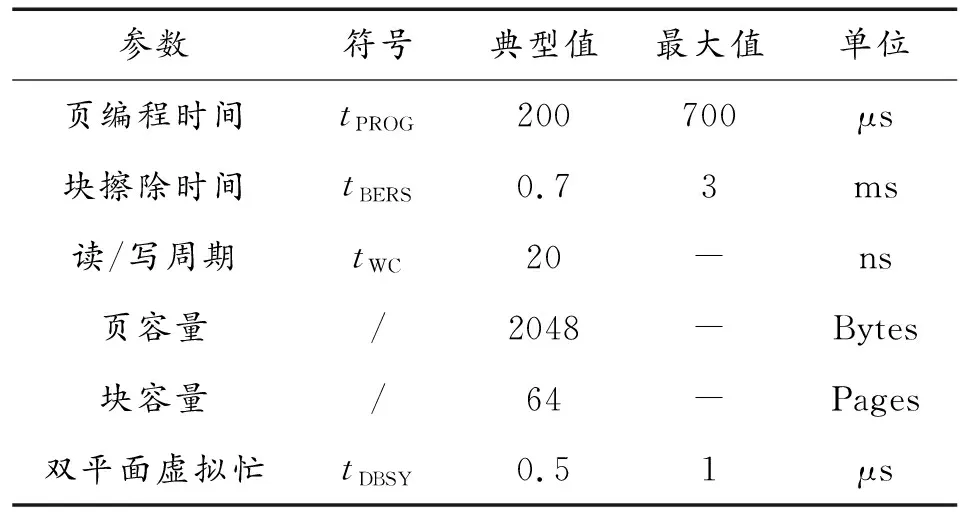

2.2 负延时读/写设计

负延时数据,即在触发信号来临之前系统尚处于未触发状态时所记录的信号数据,一般为系统基线。正向数据,即系统触发之后记录的包括完整冲击波信号在内的全部数据。与正向数据不同,负延时数据在写入FLASH时需采取边擦除、边写入的循环存储策略。而FLASH存储器受限于其特殊的存储结构,只能按页写入、按块擦除,这就对处于负延时存储阶段的数据写入速率有着严格的要求,必须保证该阶段的数据写入速率大于或等于AD的采样速率,才可以确保存入FLASH中的数据是完整、可靠的。决定负延时数据写入速率的因素主要包括FLASH存储器的页编程、块擦除时间以及系统的工作时钟。本文所选用FLASH存储器的典型参数如表1所示,其中系统工作时钟为40 MHz。

表1 FLASH存储芯片典型参数

传统的FLASH存储器数据写入方法为单个plane写入,并且在负延时阶段需擦除完成一块之后才开始按页写入数据。按此方式计算,负延时数据的最低写入速率vS:

按此方案,系统的AD采样速率最高仅为1.3MSPS。在本次设计中,采用两个plane同时写入、同时擦除的方式,即在负延时存储阶段,同时对FLASH存储器中的2块进行擦除,当负延时数据存储区域中有2块空白块之后,同时对2块中的2页进行写入。按两个plane同时写入、擦除进行计算,负延时数据的最低写入速率vD:

即系统的最高AD采样速率为2.47 MSPS,而在本文的设计中系统AD采样速率为2MSPS,双plane同时存储的方式使得本次设计的负延时数据存储方案写入速率满足设计需求。

由于负延时数据存储需要边写入、边擦除,而且需要在FIFO中存够完整的两页数据才可以进入页编程,因此在触发的同时,若系统正处于页编程时刻、块擦除时刻以及数据写入时刻等情况下,可能会有一部分负延时数据存入正向数据存储区,需将这部分负延时数据与正向数据准确区分才可以保证系统测试数据的正确性。为此,设计了如下的负延时数据读取方案。

在触发时刻,系统正进行页编程时,FIFO内数据可能为0~2.73 kByte,且此时的数据全部为负延时数据。在完成页编程并且FIFO中存满4 kByte,即完整的一页数据之后,数据将写入FLASH正向数据存储区的首两页,此时可能有一部分负延时数据一并存入该区域。为了甄别负延时数据与正向数据,在接收到触发信号时刻,需要记录触发信号来临时的当前数据在FIFO中的所处字节数m,m就是写入FLASH正向数据存储区的负延时数据的字节数,在读数时只需将正向数据存储区中第一个双页的前m字节读出,并与负延时数据存储区的负延时数据结合即得到正确的负延时数据。该情况下正向数据存储区数据示意图如图8。

图8 触发时刻系统处于页编程时正向数据存储区示意

在触发时刻,系统处于块擦除时刻时,需等待擦除完成后再将数据写入正向数据存储区,此时FIFO中的数据为11.72 kByte。但在触发时刻FIFO中的数据量为0~11.72 kByte,该时刻之前的数据均为负延时数据,之后的数据为正向数据,并同时一并存入系统的正向数据存储区。由于在等待擦除完成之后FIFO中的数据量为11.72 kByte,远大于4 kByte,因此无需等待直接从FIFO中将数据取出并写入FLASH正向数据存储区。待数据全部写入之后,正向数据存储区中可能有一部分负延时数据。因此,需要记录触发时刻数据在FIFO中所处的字节数m,并由此计算出存入正向数据存储区的负延时数据量,其计算公式为

m÷4 096=x…y

其中,x为负延时数据在正向数据记录区所占的完整双页组数x,余数y等于剩余的字节数,在下一个双页中读取y字节的数据即可得到写入正向数据存储区的全部负延时数据。该情况下正向数据存储区内数据示意图如图9。

图9 触发时刻系统处于块擦除时正向数据存储区示意图

在触发时刻,系统处于数据写入阶段时,数据读取情况与页编程时刻相同,读取数据后,只需在FPGA微控制器的负延时数据写入模块预设多个负延时长度参数,并由上位机发送指令对其进行选择、修改,即可实现负延时数据的长度可编程。

2.3 存储可靠性

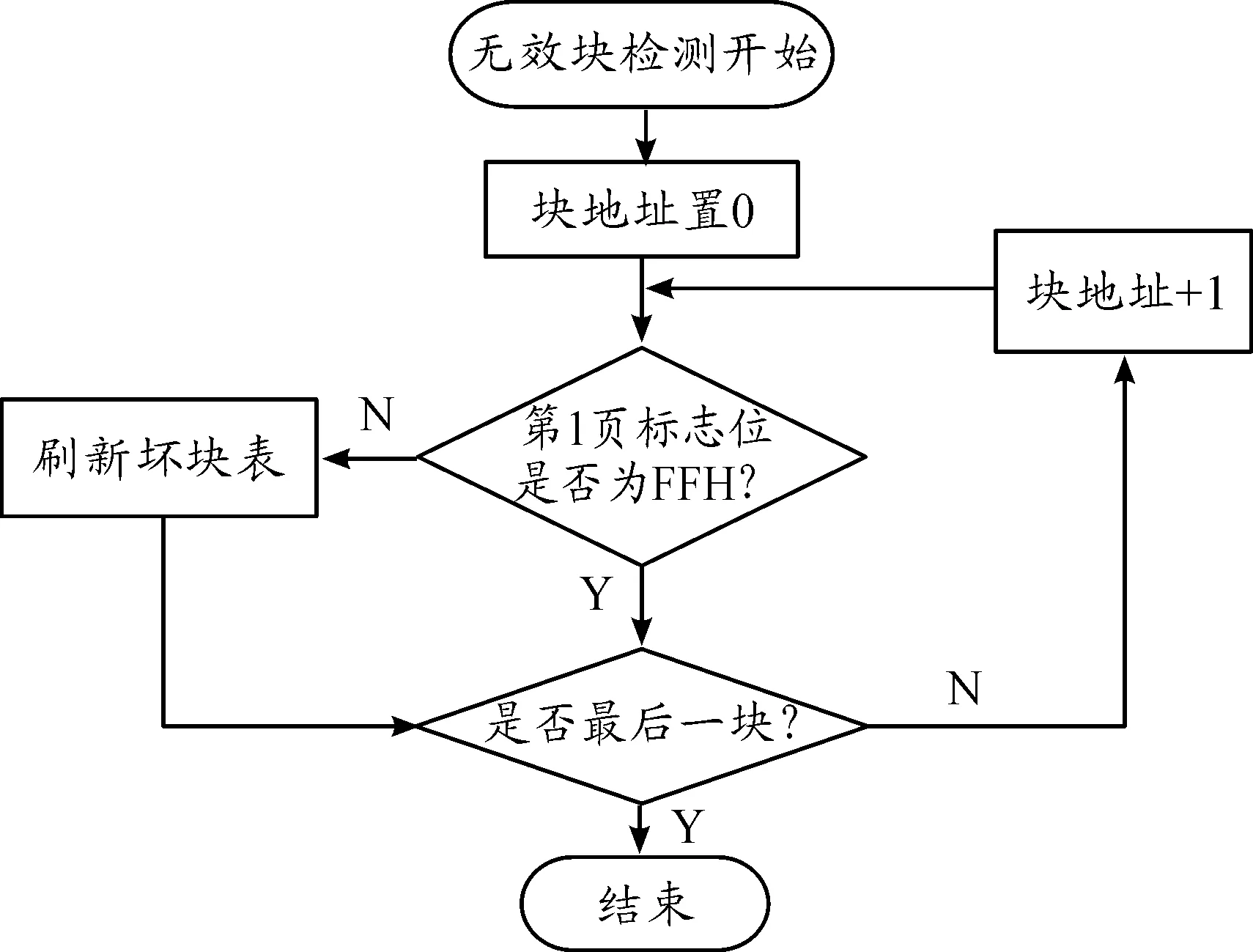

FLASH存储器受限于其生产工艺,在出厂及使用过程中都会产生无效块。为保证写入FLASH存储器中的数据准确、可靠,首先要保证的就是数据写入的均是FLASH中的有效块。为此,本设计采用块保留区替换法,在常见的无效块管理方法,即建立坏块表的基础上,将所有块分为数据块与保留块。数据块用于正常存储数据,保留块则作为数据块产生无效块之后的备份。在系统进行无效块检测时发现数据块产生坏块后,就将该无效块的地址映射到保留块中的有效块中。此方法既保证了写入FLASH存储器中的数据均写入有效块中,不会出现因写入无效块而导致的数据缺失现象,同时也保证了数据块在逻辑地址上的连续性,使得地址管理不会因FLASH划分存储区域之后出现坏块而变得过于复杂。图10为无效块检测流程框图。

图10 无效块检测流程框图

在保证数据均写入有效块之后,通过ECC校验来保证存储数据的准确性。在数据写入时对每256字节输入数据中的每个字节的某些位做异或运算得出6位列校验码,在每256字节输入数据中的各个字节之间做异或运算得出16位行校验码。在读出数据时再用相同的方式算出相应的ECC校验码,与原ECC校验码进行异或运算,若结果为0则表示读数过程中不存在错误,若结果不为0,则可根据具体的ECC校验值确定出相应的出错位并进行纠正。

3 试验结果与分析

基于上述多重触发方案的存储式炮口冲击波测试系统已经研制完成并投入使用,其实物如图11所示。其中图11(a)为系统正常使用时加盖防护壳的状态,图11(b)为系统充电及设置参数时拧下防护壳的状态。其操作面板从最下方开始按逆时针方向依次为状态指示灯、电源指示灯、开关、充电口、USB数据接口。系统内筒使用硅橡胶和聚氨酯进行灌封,使得系统抗冲击、耐高温能力大大加强,并且FLASH等重要芯片器件不易损坏、脱落。在使用时,系统通过面板四周的螺栓孔固定在预先制作的传感器支架上,保证传感器敏感面与炮口之间的距离和方向符合试验需求。

图11 多重触发炮口冲击波测试系统实物

研制完成的测试系统已经过多次实弹试验,在完成试验测试任务的同时也验证了系统的可靠性。图12为某次炮口冲击波实弹试验中某测点经连续3次触发后上位机软件读取的系统状态,软件显示系统已触发并且已经记录了3次冲击波数据以及对应的触发时间。

图12 上位机读取系统状态

图13为3次冲击波波形,从结果可以看出:在系统如实地记录了触发时间以及触发次数的基础上,3次触发的冲击波信号完整,且3次冲击波信号的超压峰值、正压作用时间以及冲量结果相近,试验结果符合预期(表2)。

表2 测试统计结果

图13 连续3次冲击波波形

4 结论

本文针对当前炮口冲击波连发测试的需求,通过对FLASH存储器进行区域划分,对负延时数据的存储采用循环擦除、写入的方案,对负延时数据及正向数据的读取方案进行合理的规划和设计,实现了存储式炮口冲击波测试系统的多重触发技术,弥补了现有存储式炮口冲击波测试系统在火炮连发测试方面的不足。经验证,本文设计的多重触发式炮口冲击波存储测试系统具有稳定性高、适用性强等特点,具有良好的应用前景。