多协议仲裁加解密读写CPU内存的IP核设计

罗 平,王瑞雪,覃海洋

(重庆大学城市科技学院 电气信息学院,重庆 402167)

0 引 言

芯片IP核内部可能有多个访存通路,同步高效地控制多个协议完成对内存的安全读写变得愈加重要。嵌入式CPU大都采用简单优先级反转仲裁或固定优先级仲裁算法来完成对多协议访存请求仲裁,即按固定的规律来对内存访问请求进行仲裁[1],这种方法很容易导致紧急的访存请求被阻塞或者某一个协议请求一直无法得到及时响应,这极大降低了CPU的访存效率。虽然一些仲裁器采用了动态优先级调整算法,即根据主设备访问不同从设备,调整自身的优先级,以提高总线的传输效率,但其本质上还是一种固定优先级[2]。同时,虽然大多数CPU有采用内存保护功能来防止非法用户读写内存数据,但是数据依然有被读出的可能性,传统的保护方法着重于防止数据被读出,但是一旦数据被非法获得,数据内容将是明文呈现给非法用户[3]。

基于这类实际问题,本文设计并实现了一种能够饱和仲裁控制多协议对CPU内存单元进行高效伪随机加解密读写的数字电路。

1 系统整体框架

整个设计主要包含同步逻辑,仲裁逻辑,加密逻辑,自定义访存逻辑,图1是系统整体框架。

如图1所示,访存协议0和访存协议1均对内存有读写需求,访存协议0来自于时钟域0,访存协议1和内存都处于时钟域1。同步握手协议模块用于在两个协议同时发起请求时,将访存协议0的请求同步到时钟域1来;饱和仲裁模块可对访存协议0和访存协议1的访存请求进行饱和仲裁,根据仲裁结果对某个协议进行访问授权;LFSR(linear feedback shifter register)伪随机加密发生器[4]、POLY和地址提取模块完成对访存读写数据进行加解密操作;自定义访存协议模块实现对内存的直接读写访存;所模块功能均在状态机的控制下实现。

图1 系统整体框架

2 功能实现

2.1 跨时钟域握手协议

因为在本次设计中,协议0和协议1分别属于两个时钟域,所以访存请求也来自于不同的时钟域,为了消除可能出现的竞争冒险现象,需要对其进行同步,同时为了正确的传输控制请求信号,采用握手协议。跨时钟域握手协议如图2所示。

图2 跨时钟域握手协议

协议0处在时钟域0,协议1与内存控制逻辑均处在时钟域1。因此,为了保证协议0访存请求的正确性,先要将在时钟域0的协议0同步到时钟域1,采用两级寄存器打拍进行,具体的做法是用另一边的时钟去捕捉对面时钟域的请求信号,通过使用两级寄存器来减小亚稳态发生的几率,以实现将两个请求信号同步到一个时钟域进行处理。当时钟域1捕捉到协议0的请求req后,将响应信号ack传回时钟域0,此时也采用两级寄存器打拍进行同步,当时钟0域捕捉到响应信号后,方可释放请求信号,这样既可以抑制亚稳态的传输,又可以正确地传输控制信号。

2.2 饱和仲裁算法

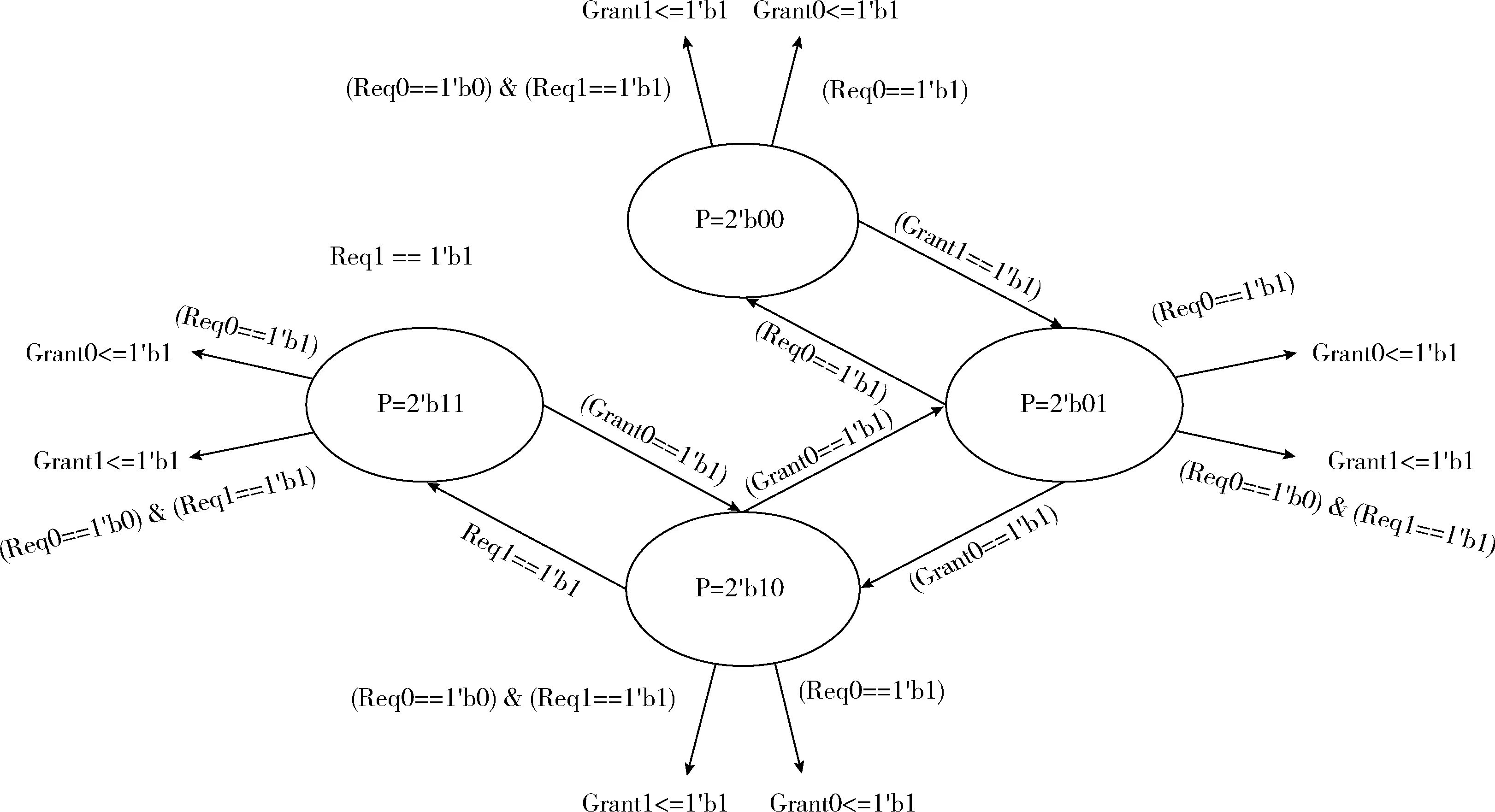

对于CPU访存过程,一个优秀的仲裁算法,当具有一定的预测能力,如此才能更加精准高效给出总线控制权。当协议0和协议1同时请求内存访问时,因为内存访问操作都具有连续性,若采用传统的仲裁算法,会导致协议0和协议1的访存操作在中途被对方频繁打断,相互阻塞,会严重地降低CPU的执行效率[5]。所以基于此现象,提出了饱和仲裁算法进行优先级仲裁。饱和仲裁器包含一个饱和计数器,其为一种有4个状态的2位饱和计数器,可分为协议0弱执行(P=2′b01)、协议0强执行(P=2′b00)、协议1弱执行(P=2′b10)、协议1强执行(P=2′b11)这4种状态,当一个访存请求被执行,对应的状态机被修改。请求不执行,则向“弱执行”方向降低状态值;如果请求被执行,则向“强执行”方向提高状态值。这种方法的特点是,某一个访存请求必须连续两次不被执行,才能从强状态翻转,从而改变执行状态。饱和仲裁算法如图3所示。

图3 饱和仲裁算法

若上电复位处于协议0弱执行状态(P=2′b01),此时,只要协议0请求(Req0=1′b1)到来,则必选择执行协议0请求,且由协议0弱执行状态跳转为协议0强执行状态(P=2′b00)。处于协议0强执行状态时,只要协议0请求到来,则必选择执行协议0请求,并维持执行状态机不变;若此时只有协议1请求((Req0=1′b0)&(Req1=1′b1))到来,则选择执行协议1请求,且状态由0强执行状态跳转为0弱执行状态,可以此类推其它剩余状态。通过简单推算,以传统的轮询算法作比较,假定A和B协议每次连续访存操作次数相等,那么采用饱和此仲裁算法,CPU的访存效率为传统轮询算法的两倍;以固定优先级算法作比较,假定A的优先级高于B的优先级,且A是B协议每次连续访存操作次数的两倍,在最佳情况下,采用此饱和仲裁算法,CPU的访存效率为固定优先级算法的3倍。由此可见,由于CPU访存具有连续性,此饱和仲裁算法正是利用这一特点进行预测仲裁,这是它的核心所在[6]。

2.3 以地址为种子的伪随机加解密算法

主流的加密算法(如RSA,MD5,DES等),安全性能较高,但是对于通用型数字SOC芯片而言,若集成此类IP,会加大芯片成本和复杂度[7]。因此,为了保护内存中的数据和代码,可采用伪随机加密算法对其进行加密。因为CPU访存与地址强相关,所以利用地址作为种子的伪随机加解密算法为较好的选择。如图4所示。

图4 加解密框架

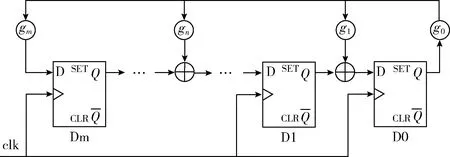

先对地址进行锁存和不规则的变换处理,然后使用LFSR伪随机序列产生器产生伪随机数,LFSR即是线性反馈移位寄存器,由移位寄存器和组合逻辑反馈组成,给定前一状态的输出,将该输出的线性函数再用作输入的移位寄存器。在数字电路实现中,一个n阶的LFSR由n个D触发器和若干个异或门组成,为便于设计,此设计中采用EE型LFSR,其多项式如式(1)所示

G(x)=gmxm+gm-1xm-1+…g1x+g0

(1)

与公式所对应的数字电路如图5所示。

图5 LFSR多项式电路

其中gm为反馈系数,取值只能为0或者1,取为0时表明不存在该反馈电路,取为1时表明存在该反馈电路,g0恒为1。由此可知,LFSR需要多个时钟周期的移位才能产生伪随机序列,若按此进行设计,会极大降低CPU的访存效率。因此,在此设计中,为了保证访存效率,可将Dm~D0设定为固定值,而将变换后的地址代替其直接作为输入,一个周期后从Qm~Q0得到输出,而地址会时刻变化且内部进行变换,这样的话,既保证了数据的随机性,又保证了数据在一个时钟周期内加解密完成,然后用产生的伪随机序列与可配置的二项式POLY相加,将得到的结果与读写数据进行异或操作,从而实现对内存单元内数据的加密写入和解密读出,其中POLY为一个可配置寄存器值,这样的话,用户可根据需求,随时微调加密算法,极大地保护内存数据的安全[8]。例如,若数据和访存地址均为32位,初始Dm~D0设为32′h87654321,访存地址变换后为32′h75318642,那么与之所对应的伪随机数列输出为32′hf254c563,POLY设为32′h92413,非加密数据为32′h80,那么加密后的数据应为32′hf25de9f6。由此可见,将访存地址和伪随机数列强相关起来,且修改LFSR的用法,可以实现在一个时钟周期内完成对内存数据的高效加解密。

2.4 自定义内存访问协议

图6为自定义内存访问协议,其特性包括:写为单周期,读为双周期;无需等待周期或回应信号;支持字节写入;控制信号简单。

图6 自定义寄存器配置协议

clk为自定义协议时钟,上升沿有效。sel为读写使能信号,当其为高时,内存处于可读写状态。addr为访问地址,决定读写内存的位置。wr为读写选择信号,当其为高时,为写操作;为低时,为读操作。be为写数据byte enable信号,可以控制其完成对字的部分写入。wdata为写数据,仅当wr为高时有效。rdata为读数据,当wr为低时,读数据在下一个周期输出有效,这是因为内存需要一个时钟周期来锁存读地址和准备数据,然后在下一个时钟周期才能输出数据[9]。

3 功能性仿真

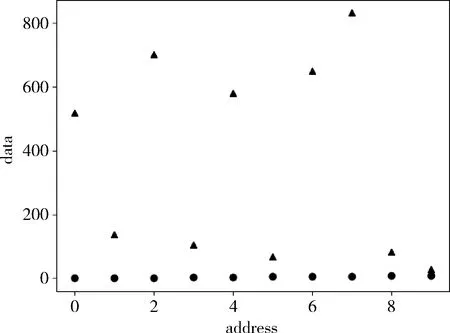

为了测试加密算法效果,对加密算法搭建相应的python模型进行仿真,如图7所示。其中,圆点代表原始打算写入数据,其值为步长为1的等差序列数据,三角形代表加密后的数据。横坐标为要访问的地址,纵坐标为数据值。由图可见,以地址为种子的伪随机加解密算法能够高效安全地完成对原始数据的随机加密。

图7 加密算法仿真

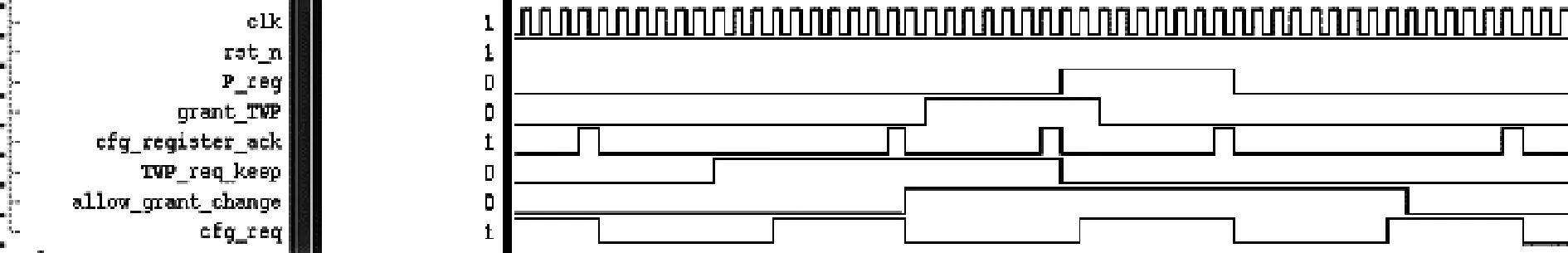

完成RTL代码设计后,编写了Testbench、Testpattern和Tracer,并对设计进行功能性仿真。仿真过程中需要产生FSDB波形文件,然后导入波形观测软件[10]。仲裁逻辑电路,需要观察两种访存请求发生时,是否能正确完成仲裁,部分仿真波形如图8所示。

图8 仲裁器仿真波形

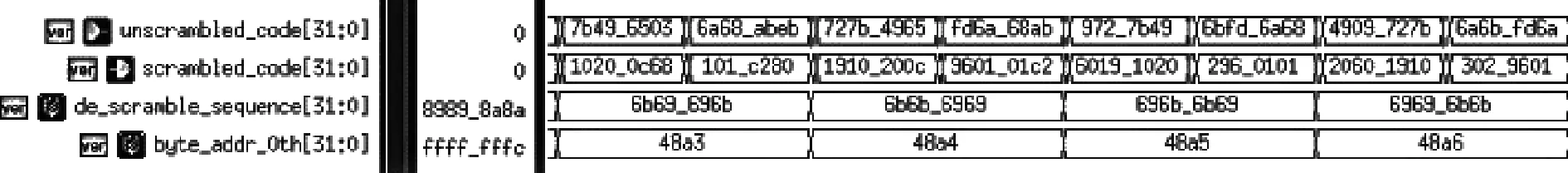

其中,clk和rst_n分别为系统时钟和系统复位信号;P_reg 为权重寄存器;grant_TWP表示当前仲裁结果;twp_req_keep 和cfg_req分别为协议0请求和协议1请求信号,可见其在饱和仲裁算法的控制下,高效实现了两种协议的仲裁响应。加密逻辑电路,需要观测原始数据是否被正确加密,部分仿真波形如图9所示。

图9 加密器仿真波形

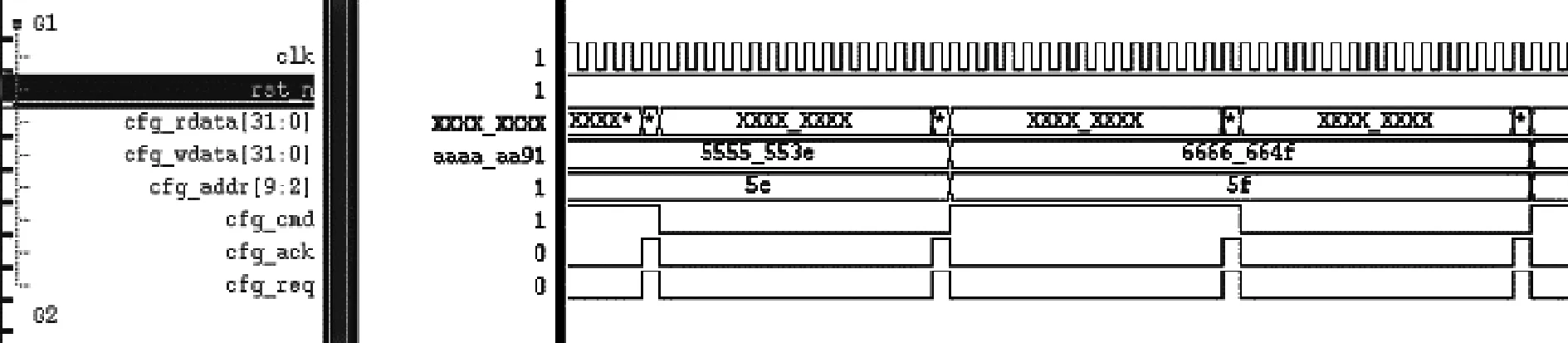

图10 自定义协议仿真波形

其中,cfg_addr为读写地址;cfg_rdata、cfg_wdata为读写数据;cfg_cmd为读写请求,可见在用户自定义协议规范下能够精准完成内存的读写。

4 结束语

本文设计并实现了一种能够仲裁控制多协议对CPU内存单元进行高效加解密读写的数字IP,提出了饱和仲裁算法和以地址为种子的伪随机加密算法,设计了自定义的访存协议。区别于传统访存电路设计,该设计能够更加高效安全地实现多协议内存访问,且设计在55 nm SOC芯片项目中得到验证,在CPU主频200 MHz情况下,多协议访存正常。依照文中设计思路,可在此基础上扩展更多的访存协议,以实现多协议对内存的高效安全访问,或将设计应用于其它读写控制,如Flash访问控制。同时,可以根据不同的访存场景,修改饱和计数器的宽度,实现不同协议间优先级的弹性选择。