一种射频数字一体化宽带收发模块设计

范欢欢, 伍小保, 孙维佳

(中国电子科技集团公司第三十八研究所, 安徽合肥 230088)

0 引言

有源相控阵雷达由于其可针对多目标、机动性强、反应时间短、功率效率高等优点[1],逐步被广泛应用于有人机、无人机等机载平台。在传统设计中,雷达收发系统的射频收发和数字收发作为独立模块分开设计。该设计结构功能划分明确清晰,但是增加了系统体积,同时模块间的线缆互联也十分繁琐,不利于安装和维修,同时互联环节增多还影响宽带收发性能指标。另外,由于雷达探测的精度要求越来越高,对信号带宽和质量的要求也越来越高。

本文设计了一种射频数字一体化高集成宽带收发模块,射频收发部分采用裸芯片微系统集成方式,减小设计体积和功耗,使其能够与数字收发电路集成在一个ASAAC模块内,从而大大提高了空间利用率。通过选用高性能的数字收发芯片,实现2 GHz以上瞬时带宽宽带激励信号产生和宽带信号采集、8~12 GHz窄带激励信号产生。

1 硬件实现

为实现带宽2 GHz的宽带接收,若采用数字解调,要求中频不能太高,否则当前ADC水平模拟带宽限制将无法直接进行中频采样;若采用宽带模拟一次混频,要求中频不能太低,否则射频镜像与射频信号太近无法滤波。因此宽带接收无法采用中频采样数字解调方式进行接收。本设计采用模拟直接解调后基带数字化方式实现。

根据目前商用DAC的发展水平,ADI公司推出商用货架16位12.0 GSPS转换速率的DAC芯片AD916x系列(时钟6.0 GHz,2倍内插模式),支持的最大接口数据率6 GSPS,混频模式下可直接输出1.5~7.5 GHz频段射频信号,满足直接输出1.8 GHz带宽射频任意波形信号的能力[2]。为实现2 GHz或更宽带宽的波形信号,宽带信号产生基于“直接数字宽带中频产生+模拟倍频到射频”方式实现。

窄带激励考虑多种形式信号的产生,采用“直接数字高中频产生+模拟混频到射频”体制实现。

1.1 电路结构

射频数字一体化高集成宽带收发模块主要由射频收发和数字收发两部分组成,为标准6U ASAAC结构形式,其基本组成框图如图1所示。

图1 一体化高集成度宽带收发模块基本组成框图

其中,射频部分包括解调模块和激励模块。解调模块将雷达天线接收到的射频信号进行模拟正交解调,得到基带IQ信号;激励模块将数字模拟转换器(DAC)输出的中高频信号经过倍频或混频得到射频激励信号,通过雷达天线发射。

数字部分主要由运算放大器、模拟数字转换器(ADC)、DAC、现场可编程门阵列(FPGA)等组成。FPGA产生的数字波形经过DAC转换成模拟信号后送给激励模块;运算放大器作为ADC的接口电路,将解调模块的输出信号进行调理后送入ADC进行采样,采集的数据送入FPGA进行处理。

此外,模块还包含时钟、电源、射频互连接口、高速串行通信以及低频控制接口。电源采用数字、模拟分区设计,以减少干扰,优化性能。射频接口采用稳相电缆通过LRM连接器与其他功能模块互连。高速串行接口可用于接收配置参数、发送采集数据。低频控制接口用于接收导前等系统时序控制信号。

1.2 射频收发设计

考虑射频数字一体化高集成度实现,激励模块和解调模块基于射频微系统集成思路进行设计,采用裸芯片微系统集成方式降低体积和重量。以一体化收发板作为载板,将两个射频模块进行机械固定,通过连接器为其供电和控制。

与教师相比,同伴榜样的“闪光点”起着更加具体化、实际化的示范作用,更贴近学生。为把榜样的引领落到实处,学校应每学期都评选“三好学生”“优秀学生干部”“文明之星”“礼仪小标兵”等榜样;班级也可利用“每周一星”的评选,发现好人好事并给予表扬、鼓励,把他们的先进事迹进行宣传,印在学生脑海中,让榜样在学校管理工作中不断发挥积极的作用。

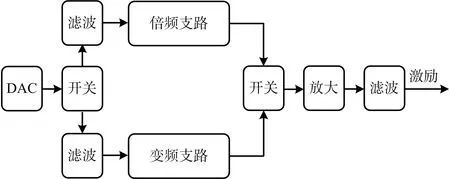

宽窄带模拟激励模块链路如图2所示。DAC输出的中高频信号经过开关分别送入倍频支路和变频支路。倍频支路将信号进行二倍频并滤波放大,产生瞬时带宽2 GHz的宽带激励信号。变频支路将信号与本振混频,滤波放大得到8~12 GHz的射频信号窄带激励信号。宽窄带激励信号由开关控制切换、分时输出。

图2 宽窄带模拟激励模块链路

图1中的解调模块将宽带回波射频信号经过放大、滤波、混频,正交解调为基带I/Q信号,送入ADC进行数字采样。

1.3 数字收发设计

1.3.1 硬件设计

波形产生采用FPGA+DAC的方法,波形参数可灵活配置,产生形式灵活可变[3]。根据性能需求,FPGA选择Xilinx公司的XC7VX690T;DAC选用ADI公司的16位12 GSPS芯片AD9164BBPZ。在FPGA中产生基带I/Q数字波形,并在DAC里进行内插和混频,得到中高频波形信号。

接收采集采用运算放大器+ADC的直流耦合电路。运算放大器作为ADC的输入接口电路,实现宽带回波的单端至差分转换。ADC选用ADI公司12位2.5 GSPS芯片AD9625BBPZ-2.5[4];运算放大器选用ADI公司的双通道芯片ADL5567,该芯片的-3 dB带宽为4.3 GHz,在所需频率范围内保证良好的平坦度。

1.3.2 硬件设计仿真

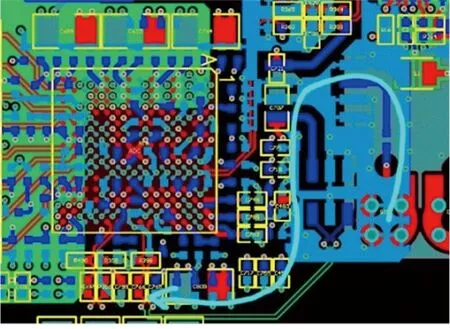

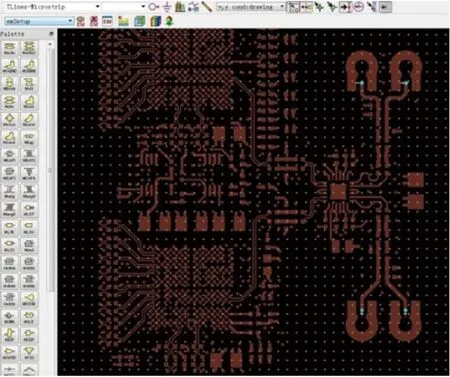

鉴于ADC采样率较高,基带I/Q通道的幅度和正交度对系统结果影响很大,需要在硬件设计中尽可能保证两路采集通道的一致性。为此,我们分别对时钟路径和信号路径进行了PCB仿真。

仿真软件采用Agilent ADS2011。图3为两片ADC时钟信号输入路径仿真结果。由结果可以看到两路时钟信号幅度相位一致性很高。两路2.4 GHz采样时钟在PCB走线上只差22 ps。

(a) 时钟信号路径PCB建模图

(a) PCB建模模型图

2 FPGA逻辑实现

宽带数字收发FPGA主要实现数字波形产生、宽带基带I/Q信号采集及后处理、缓存、打包和传输。

2.1 接收采集处理

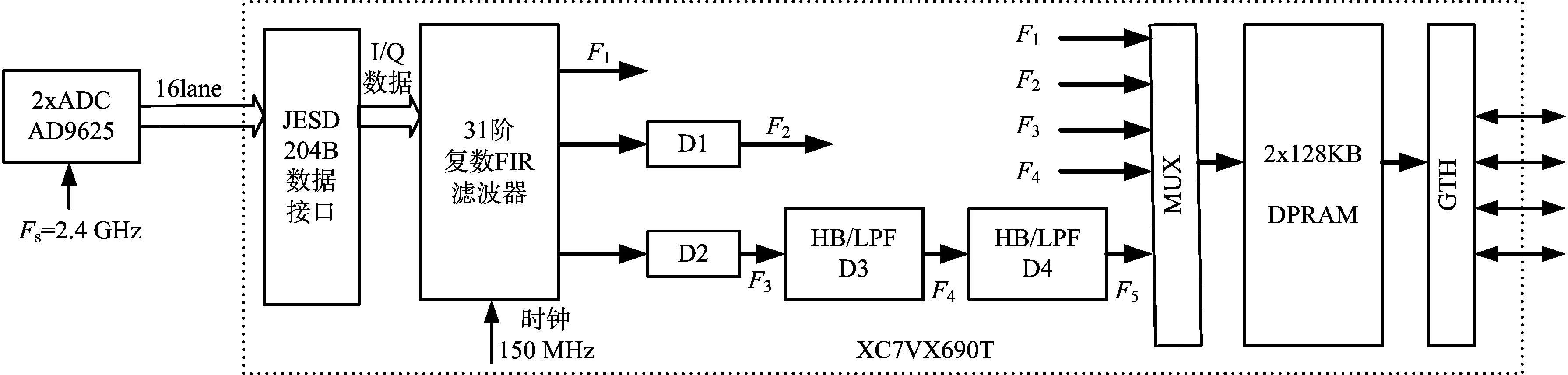

接收采集处理流程框图如图5所示。上电工作后,FPGA对两片ADC配置,并按照JESD204B协议建立链路、将数据进行串并转换和重新组合,得到I/Q采样数据。

图5 一体化宽带数字收发接收采集处理流程框图

I/Q数据送入复数FIR滤波器进行滤波。为了改善宽带信号的性能指标、减少FPGA资源的占用并降低功耗,该滤波器分时复用,分别对模拟正交解调后采集的宽带信号的幅相正交度、带内幅相起伏和非线性进行补偿[5-7]。另外,该滤波器通过改变滤波器系数以匹配不同带宽信号的抽取前滤波器,实现抽取前带外噪声和干扰的抑制,以改善输出SNR。滤波后的数据经过不同抽取比得到三种速率(F1,F2,F3)的采样数据,分别对应三种不同带宽的信号。较窄带宽的信号可采用滤波器级联的方式实现更优的滤波效果。F3数据率的数据经过两级半带低通滤波器和抽取后得到两种较低速率(F4,F5)的数据。

经过滤波抽取后得到的五种带宽信号的采样数据,经过一个多选一选择器输出当前工作带宽下的采样数据,并将其缓存在RAM中。最后,根据系统工作时序将系统参数与采样数据按照一定格式进行打包,通过高速接口送入雷达后端处理单元。

2.2 发射波形产生

本文中波形产生采用FPGA+DAC的方案,直接输出中高频信号。其处理流程框图如图6所示。上电工作后,由FPGA配置DAC芯片并与之建立JESD204B链路。FPGA中采用8倍并行直接数字频率合成(DDS)方式实现基带I/Q波形信号,并采用数字预失真补偿整个链路的非线性[8],以提高激励信号的质量。波形产生的带宽、脉宽等参数可根据每个脉冲灵活配置。通过JESD204B数据接口模块将波形并行数据按照格式需求排列,并进行并串转换,通过JESD204B链送给DAC。

图6 一体化宽带数字收发数字波形产生流程框图

基带I/Q信号在DAC内进行内插、滤波和混频,经过数字模拟转换电路,最终输出模拟的中高频波形信号。

3 测试结果

图7为一体化高集成度宽带收发模块的实物图。最后,对该模块的功能和性能各进行了测试,其测试结果如下。

图7 一体化高集成度宽带收发模块实物图

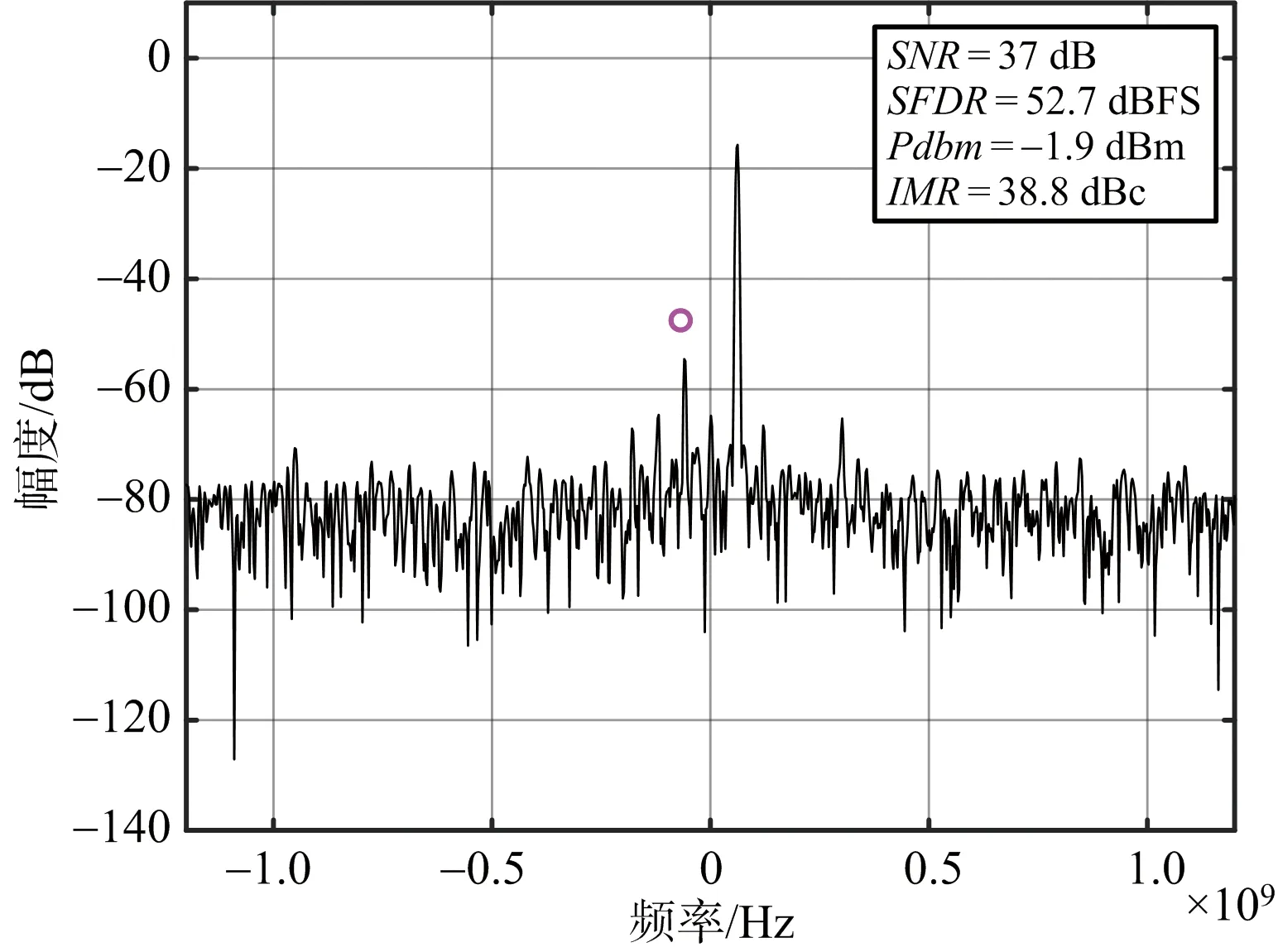

图8为接收系统测试结果。用信号源输入一路偏离中心频点60 MHz的射频信号,ADC采集解调模块输出的基带信号,最终数据由Matlab分析得出,在输入信号功率为-1.9 dBm的条件下,信噪比为37 dB,无杂散动态范围为52.7 dBFS,镜像抑制为38.8 dBc。由测试结果可以看出,采集部分数模电路干扰抑制设计满足需求。

图8 接收系统测试结果

图9为2 GHz带宽激励信号的测试结果。其中,图9(a)、(b)分别为用频谱仪测量得到的激励信号的频谱和脉内信噪比。由结果可以看出,激励信号的带外杂散好于55 dB,脉内信噪比好于60 dB,数模混合电路设计干扰抑制满足需求。为了分析激励信号脉冲压缩后的性能指标,将激励信号经过外加衰减器回环到模块的接收端进行采集并分析。图9(c)为用Matlab分析得到的射频收发闭环信号的幅相非线性,由图可见幅度误差小于1.5 dB,相位误差小于6°,非线性指标满足要求。图9(d)为脉冲压缩分析结果,可以看到主副瓣比大于40。

(a) 激励信号频谱

4 结束语

本文介绍了一种高集成度宽带收发模块的设计方法,详细描述了射频、数字部分的硬件设计和部分电路仿真,并阐述了FPGA软件设计思路,最后给出了测试结果。该设计实现了2 GHz瞬时带宽的激励信号产生和2 GHz瞬时带宽宽带接收,能满足目前大多数宽带雷达系统的需求,并且该模块已应用到相关机载课题和型号项目中。