薄硅膜SOI 器件辐射效应研究

贺 琪,顾 祥,纪旭明,李金航,赵晓松

(中国电子科技集团公司第五十八研究所,江苏无锡214035)

1 引 言

绝缘层上硅(Semiconductor on Insulator, SOI)技术的发展一直以抗辐射加固的军事和空间应用为背景,其主要原因是SOI 技术能够实现器件的全介质隔离,消除体硅CMOS 电路的寄生NPNP 通道,具有良好的抗闩锁效应和抗瞬时辐射效应的能力[1-3]。但由于其较薄的硅膜厚度以及掩埋氧化层(Buried Oxide, BOX)的存在,导致SOI 器件的总剂量辐射效应加剧,器件性能退化严重,进而导致集成电路系统性能的退化[4-5]。SOI 器件的抗辐射性能主要由栅氧化层、场氧化层、埋氧化层以及SOI 硅膜厚度等因素决定,器件对这些影响因素的辐射敏感性可以通过测量电路和器件的电特性来研究。在此主要研究SOI 材料硅膜厚度对晶体管前栅阈值、背栅阈值以及辐射前后漏电流的影响规律。在所选用的工艺条件下,确定SOI 材料硅膜的厚度、NMOS 管初始背栅阈值电压及单元控制电路的抗总剂量辐射能力。

2 实验步骤

在研究中选用的SIMOX SOI 衬底材料顶层硅厚度中心值为205 nm,掩埋氧化层厚度中心值为375nm。在测试芯片中加入了用于单元控制电路开发的SOI CMOS 晶体管测试评估结构。0.8 μm SOI CMOS 工艺具有N+掺杂多晶硅栅,栅氧化层厚度为17.5nm,被场氧化物和掩埋氧化物隔离。NMOSFET和PMOSFET 均采用轻掺杂漏(Lightly Doped Drain,LDD 和Halo 注入技术。典型的MOS 晶体管结构如图1 所示。

图1 典型SOI MOS 晶体管结构剖面图

SOI 材料的初始硅膜厚度由材料供应商提供,通常不同批次圆片厚度范围在190nm~210nm 之间波动。挑选 190 nm、195 nm、200 nm、205 nm、210 nm硅膜厚度的材料片共5 档,进行同批次流片。出片后得到SOI MOS 管和单元控制电路样品。用S4200参数分析仪测量晶体管的初始电特性,主要测量器件前栅和背栅的开启电压,同时用J750 测试仪测量单元控制电路的静态电流。

表1 列出了SOI 材料片的硅膜厚度、晶体管前背栅极的阈值电压和电路静态电流。前栅极和背栅极的阈值电压根据硅膜厚度而变化的趋势可由图2呈现。可见,晶体管前栅极和背栅极的阈值电压随着硅膜厚度的增加而增加,电路的静态电流基本在700~800μA 的水平,无明显差异。

表1 不同硅膜厚度下晶体管Vth 和静态电流

图2 硅膜厚度-阈值电压趋势图

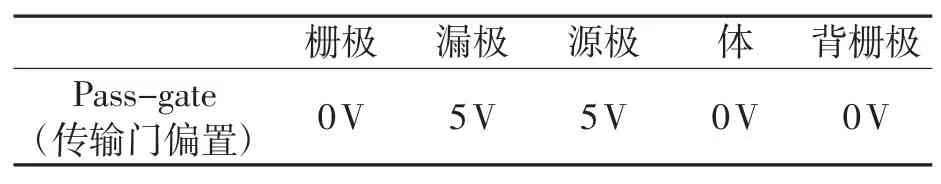

随后将器件和电路样品放置在60Co 辐射环境下,同时对器件施加最恶劣偏置。NMOS 器件通常在传输门偏置下最为恶劣[6-7],具体偏置条件如表2 所示。累积150krad(Si)的总剂量辐射后再次测量器件和电路的特性,NMOS 和PMOS 晶体管的前栅极阈值电压漂移量均小于300mV。由于NMOSFET 辐射引起的背栅开启电压变小、漏电增大,而PMOSFET刚好相反,在辐射后器件背栅开启电压变大、漏电降低,因此应重点研究NMOSFET 器件辐射后的器件前栅和背栅特性的变化对电路静态电流的影响。

表2 晶体管的辐照偏置条件参数

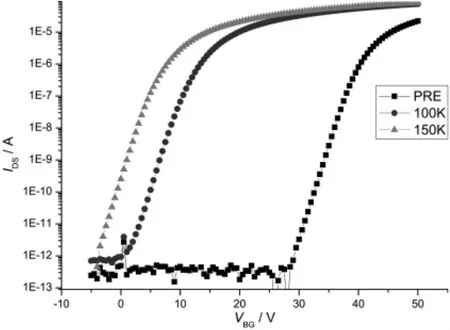

图3、图4 给出了使用不同硅膜SOI 材料的10 μm/0.8μm(W/L)NMOS 晶体管在最劣偏置下的辐射效应。辐射引起的晶体管背栅极阈值电压漂移量均为约18V。图5 给出了典型的VBG-ID曲线。但对于初始阈值电压不同的样品,150krad(Si)辐照后,NMOS晶体管背栅极的阈值电压各有不同,分别为1V、2V、4V、6V、10V。当NMOS 晶体管背栅极阈值电压小于5V 时,电路静态电流将陡增并超出规范值。

图3 不同硅膜厚度下背栅极Vth 漂移

图4 不同硅膜厚度下前栅极Vth 漂移

图5 不同辐射剂量下典型背栅极VBG-ID 曲线

图6 显示了不同硅膜SOI 电路静态电流的辐射响应。由图可知,硅膜厚度为190~200nm 时,辐射后电路静态电流明显增大并且超规范;当硅膜厚度为205~210nm 时,辐射后电路静态电流保持恒定不变。因此,电路的静态电流随辐射剂量的增加而漏电增大,随SOI 材料硅膜厚度的增加而漏电降低。

图6 不同硅膜厚度下静态电流的辐射响应

3 仿真实验及结果讨论

针对上述试验数据和结果,采用工艺仿真软件Sentaurus TCAD(2013)进行工艺和器件模拟。首先将仿真环境校准到实际工艺,对电子和空穴两种载流子同时进行计算处理,这样可以获得更佳精准的仿真结果。

图7 给出了375nm BOX 上硅膜厚度为205nm的典型0.8μm NMOSFET 器件结构的载流子掺杂分布图。图8 显示了不同硅膜厚度条件下的净电荷浓度分布曲线[8-9]。由此我们可以看到载流子浓度随着硅膜深度的扩展逐渐升高,在Si/BOX 界面处浓度陡降,这是因为埋氧化层在工艺热过程中发生了严重的吸硼效应。对于在不同硅膜厚度的SOI 材料上制作的器件,硅膜厚度越厚器件的背界面处的载流子浓度越浓,这是因为在相同注入条件及热过程工艺后,粒子在硅中的射程是一样的,当粒子到达Si/BOX 界面后会直接进入埋氧。粒子在较厚硅膜中的运行路程长,杂质在Si 界面处的浓度高。

图7 典型NMOSFET 结构净掺杂浓度模拟结果

图8 不同硅膜厚度下硼浓度分布曲线

MOS 管阈值电压表示式如下式所示:

其中,NA为衬底掺杂浓度,阈值电压随着该浓度的增加而增大,因此,当硅膜厚度较厚时,前栅和背栅器件的初始阈值电压较高。

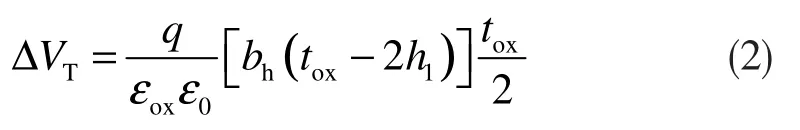

在辐射环境下,SiO2/Si 界面处会发生正电荷的堆积,从而引起器件阈值电压的漂移,最终影响器件的性能。因辐射引入的俘获空穴而引起的阈值电压变化的过程可以由下式描述:

式中,bh是氧化物中产生的空穴被俘获后形成固定正电荷那部分的体密度;参数h1是从Si/SiO2 界面指向氧化物的距离,在此距离内被俘获的空穴可以与从衬底向栅隧穿的电子复合。只有当氧化物厚度小于2×h1(即6nm)时,才观察不到有显著净的空穴俘获。在本工艺中,前栅栅氧厚度为17.5nm,背栅埋氧厚度为375 nm,因此,器件在总剂量辐照后前栅栅氧和埋氧都会有较明显的空穴产生,前栅器件阈值电压漂移量在0.3V 左右,背栅器件阈值电压漂移量在18 V 左右,当背栅开启电压漂移到7 V 以内时,背栅器件就会出现明显的漏电,最终导致电路漏电,只有当硅膜厚度大于205 nm,背栅器件的初始背栅开启电压大于25V 时,才能保证器件及电路有100krad(Si)的抗总剂量能力。

4 结束语

针对SOI 硅膜厚度的辐射响应所做的实验表明,必须控制硅膜厚度才能在SOI CMOS 器件和电路上获得令人满意的抗总剂量能力。通过TCAD 仿真工具对器件掺杂浓度分布进行分析,结合器件辐射效应原理,都印证了这一结论。另外,对吴建伟的技术讨论与支持致以衷心感谢。