军用印制板标准在理解和实施中的问题探讨

张永华 张 涛 刘立国

(无锡江南计算技术研究所军用印制板质量检测中心,江苏 无锡 214083)

0 前言

紧随印制电路板(PCB)产品高密度、高集成度和高可靠性的快速发展,新修订的军用印制板标准一方面新增了铜盖覆镀层、盲埋孔树脂塞孔、微导通孔等成熟工艺的性能要求,另一方面扩展细化了连接盘缺陷、导体最终镀层或涂层、阻焊膜、镀覆孔孔壁缺陷等要求,并对应IPC标准中的3A级产品,增加了宇航用印制板的性能要求。无论新增要求的提出,或是原定要求的修改,均是基于印制板连通性、非连通性(绝缘性)和长期使用的可靠性的考虑。

为积极推动军用印制板标准在工艺鉴定和产品质量管控中的基础作用,本文将基于标准最新规定,通过典型案例分析的方式,探讨标准中各项性能要求提出的出发点,以及在理解和实施过程中可能遇到的一些问题,希望可以减少因标准理解不当而造成的损失。

1 外观和尺寸检验

印制电路板的外观,包括标识、绝缘基材、表面涂镀层、导电图形等,是印制电路板加工质量最直观的反映,也是产品实现顺利交付的重要基础,其检验方法是使用3倍线性放大镜(仲裁检验应在至少30X的放大镜下进行)在合适的光照条件下进行目检。而印制板尺寸,包括外形、板厚、孔位精度、外层环宽、导体宽度和间距等,表征了印制板加工与布设总图和相关规范的符合性,是保证后续电装和安装质量的重要前提,应采用精度不低于0.01 mm的量具进行测量。

1.1 露织物、显布纹和露纤维

如果层压过程中流胶过多或受到化学侵蚀,印制板表面会出现明显的纤维纹理。若未断裂的织物纤维完全暴露在空气中,为露织物,而当其表面仍有树脂覆盖时,则为显布纹(见图1)。

图1 (A)露织物(B)显布纹

由于缺少了树脂的保护,裸露的玻纤更易吸附水分和化学残留物,引起印制板绝缘性能的劣化,因此露织物的印制板不可接收。显布纹的印制板可以接收,但粗糙的表面往往给人一种质量不高的观感,且很难仅通过目检与露织物的印制板区分开。

由于基材受到机械应力冲击、划伤或化学侵蚀,而出现的增强纤维裸露的现象,称为露纤维。与露织物相比,露纤维通常只会在局部位置出现;因此,只要增强材料未出现明显的切断或变形,并且未使导电图形之间的间距低于布设总图规定的最小值,可以接收。

1.2 白斑和微裂纹

白斑和微裂纹都是发生在基材内部玻璃纤维与树脂分离的现象,并表现为基材下的白色斑点或十字纹,其中白斑呈分散状(见图2),微裂纹呈阵列状(见图3)。

图2 白斑

白斑的产生多源于印制板已受潮,并在受到热应力冲击时,急剧的膨胀破坏了玻纤与树脂结合的化学键,最终导致经纬玻纤在交织处出现局部分离现象;白斑常发生在大面积铜箔边缘。由于白斑存在于基材内部,并不会吸收离子污染物,也没有证据能够证明白斑会成为CAF(导电阳极丝)的生长通道,因此只要白斑的尺寸不大于0.80 mm且未跨接相邻导体,是可以接收的;但白斑的存在降低了印制板的绝缘和抗电强度,尤其是高海拔、低气压环境下,绝缘性能下降更为明显,因此对于高电场(通常指1000 V)和宇航用印制板,白斑不可接收。

图3 微裂纹

微裂纹的产生通常是由于基材受到了外部强烈的机械应力冲击;微裂纹降低了基材的刚性和绝缘性,因此微裂纹区域不应超过相邻导体间距的50%,且在热应力、模拟返工或温度冲击试验后裂纹不应扩大;宇航用印制板不允许微裂纹。

1.3 粉红圈

多层板内层孔环处的黑化层(氧化铜)或棕化层(氧化亚铜)侧缘,因受镀孔工艺中强酸槽液的横向浸蚀,而变为原铜色,当这一区域超过了外层孔环的覆盖范围时,成品印制板上便可观察到沿孔环边沿分布的粉红圈。目前还没有证据证明粉红圈会影响到印制板的功能性,因此粉红圈可认为是一种制程预警,只要未跨接相邻导体,不应作为拒收的理由;但粉红圈的存在破坏了黑化层的微观结构,事实上降低了内层铜箔与树脂间的物理结合力,因此在印制板受到热应力冲击时,如果出现了分层现象则不可接收;对于高密度印制板,粉红圈的出现会增加CAF风险,因此必须进行良好的管控;粉红圈的出现,通常会伴有三角形的楔形空洞(已被电镀铜填充),如图4所示。

图4 楔形空洞

1.4 铜镀层空洞和最终涂覆层空洞

铜镀层空洞会影响镀覆孔的孔电阻和载流能力,成品印制板目检时,孔内不应有铜镀层空洞,因为目检时能够发现的镀层空洞,其尺寸通常较大,将对后续电装的成品率和电路的性能产生严重不良影响。显微剖切方法检验时,允许铜镀层厚度减少不超过规定铜镀层厚度(通常为25 μm)的20%,但应是孤立的且不大于板厚的10%,这是针对镀覆孔个别位置铜镀层厚度小于平均厚度要求,但又满足最小铜镀层厚度要求的情况;铜镀层厚度小于规定值的80%(通常为20 μm),视为镀层空洞,每块板的空洞数不多于1个,且空洞的最大尺寸未超过板厚的5%时,可以接收,这是针对铜镀层厚度小于最小铜镀层厚度要求的情况;内层导电层和镀覆孔孔壁的界面处应无镀层空洞;宇航用印制板不允许铜镀层空洞。典型铜镀层空洞缺陷如图5所示。

图5 铜镀层空洞

如果最终涂覆层空洞垂直方向的长度不大于孔长度的5%,并且横向尺寸未超过孔周长的25%时,镀覆孔内允许存在1个最终涂覆层空洞;过大的涂覆层空洞,尤其是当暴露基底镀铜层时,会极大地降低镀覆孔的可焊性;宇航用印制板不允许涂覆层空洞。

1.5 阻焊膜

阻焊膜的主要作用是防焊、绝缘和减少印制板面污染。由于起泡、脱落、褶皱、跳印(漏印)、吸管状空隙等缺陷,均会导致PCB吸潮、藏匿污染物,导致印制板导电图形间的绝缘性降低,增大电化学迁移的风险,因此均不允许。

图6 阻焊膜厚度测量图

如图6所示,为保证阻焊膜对导体起到足够的覆盖保护作用,防止假性露铜等现象,B处的阻焊膜厚度应不小于0.018 mm;A处阻焊膜厚度过厚,会导致其与邻近待焊接焊盘高度差过大,阻碍焊料与焊盘的接触,极易引起可焊性不良现象的发生,尤其是对于阻焊限定的连接盘的情形,因此基材上阻焊膜的厚度不应大于0.1 mm;C处的阻焊膜厚度应能覆盖导电图形。对于厚铜板,如铜厚大于70 μm(2 oz/ft2)以上的印制板,为保证C处阻焊膜不会出现暴露导体的情形,通常都会增大阻焊膜的印刷量,此时A处的阻焊膜厚度要求,可由供需双方共同商定。

1.6 导电图形尺寸

印制板导线的宽度和间距是衡量印制板加工质量和工艺能力的重要尺度;由于边缘粗糙、缺口或露基材的划痕使导线宽度的减小应不大于布设总图规定的最小导线宽度的20%,由于孤立的突出、残渣或对位不良使导线间距的减小应不大于20%;对于微波印制板有阻抗控制要求的导线,上述缺陷造成的尺寸减小应不大于10%。

2 显微剖切要求

显微剖切方法是评价PCB内部质量的重要手段,选取的试样应包括3个在同一直线上的镀覆孔(涵盖PCB上最小孔径的孔),并在100X的放大倍率下检验(仲裁检验放大倍率不低于200X)。需要注意的是研磨和抛光应使观察面在孔中心±10%以内,否则将导致镀层厚度测量结果误差较大;镀层分离的判定、残铜引起的介质层厚度的减小、芯吸长度的测量,都应在微蚀之前进行评定;镀层厚度(如镀金层)小于1.25 μm时,显微剖切方法的测量误差较大,应采用其它替代方法(如X-荧光镀层测厚仪)进行测量。

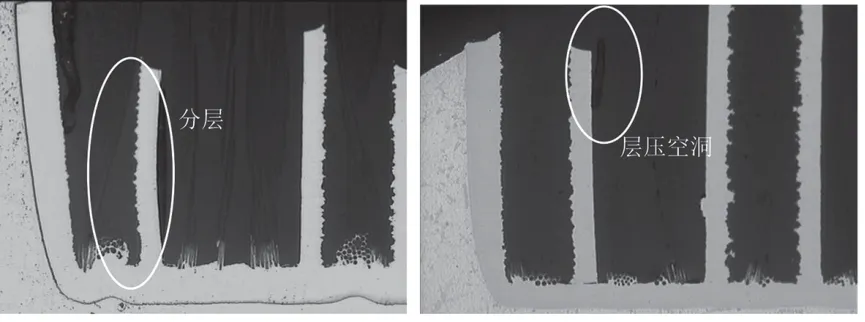

2.1 分层和层压空洞

分层和层压空洞都是在层压制程中出现的缺陷,其中分层指的是基材中的绝缘层间或绝缘层与铜箔之间分离的现象,层压空洞是指因树脂填充不充分而出现的局部区域缺胶的现象。在受到较大的机械应力或较强的热冲击时,极易出现分层的扩大甚至爆板,导致失效。因此印制板不应有任何形式的分层现象,层压空洞的出现会降低印制板的绝缘性能,其尺寸应控制在一定范围之内。

热应力、模拟返工或温度冲击试验后,A区(镀覆孔或微导通孔周围0.08 mm以内的受热区)的层压空洞不做评定,但应进行分层的评定。因此,印制板在受热后出现在内层铜箔和基材之间的分离现象,通常表现为狭长、规则的形貌(分离界面整齐),并时常伴有内层铜箔的变形,应作为分层进行判定不予接收;而出现在内层铜箔和基材之间的层压空洞,通常表现为一种不规则的形貌,其在A区的尺寸不做测量,只要其延伸部分在B区(层压评定区)的尺寸不超过0.08 mm,允许接收(见图7)。

图7 出现在内层铜箔和基材之间的分层和层压空洞

2.2 树脂凹缩和孔壁分离

层压电镀后的印制电路板,镀覆孔孔壁背后的基材若未彻底硬化,在受热后会出现局部区域继续硬化聚合,造成树脂从孔壁处退缩而出现空洞的现象,称为树脂凹缩。交收态印制板显微剖切后,树脂凹缩深度应不大于0.08 mm,且被评定镀覆孔每一边上的树脂凹缩应不大于该边基材累积厚度(被评定的介质层厚度的总和)的40%。由于孔壁铜镀层与基材结合力不足,印制板受热后造成的孔壁与基材的分离现象,会极大地降低孔壁铜镀层的机械强度,因此不可接收。

树脂凹缩通常表现为沿孔壁边缘向基材方向收缩的圆弧形,镀覆孔孔壁形貌基本保持不变;而孔壁分离现象常常伴有孔壁的变形,且分离处两侧的形貌相似对称,呈弹开状态(见图8)。

热应力、模拟返工或温度冲击试验后,树脂凹缩产生的应力只要未造成孔壁铜镀层断裂,可不进行判定。

图8 树脂凹缩和孔壁分离

2.3 层间重合度

只要印制板最小内层环宽不小于0.05 mm,即满足层间重合度的要求,过小的内层环宽甚至破孔现象,会极大地降低镀覆孔和内层导电图形之间的互连可靠性。层间重合度测试不需单独取样,但为防止因显微剖切的选取方向可能引起的误判,应对两个附连测试板(“交收态”和“热应力”)分别沿长度(X)方向和宽度(Y)方向进行显微剖切测试。

内层环宽的测量应在微蚀后进行,并选取印制板各层中的最小环宽,从内层孔环边缘测量至内层连接盘与孔壁连接处,如图9所示。

图9 内层环宽测量示意图

2.4 铜包覆镀层和铜盖覆镀层

为保证镀覆孔的高可靠性,树脂塞孔工艺变得更为普遍,并对铜包覆镀层和盖覆镀层提出了新的要求。铜包覆镀层是指由孔壁镀层延伸至表面连接盘上的铜镀层,铜盖覆镀层是指覆盖在塞孔绝缘材料和铜包覆镀层之上的表面铜镀层。

导通孔的铜包覆镀层厚度应不小于12 μm,测量的位置是表面连接盘除去基底铜和盖覆铜之后的总厚度(见图10)。

图10 铜包覆镀层厚度测量图

树脂研磨、蚀刻或整平处理,均会造成表面铜包覆镀层厚度的减少,但不应小于规定值的20%;铜包覆镀层厚度不足时,会极大地降低连接盘上铜镀层和基底铜箔之间的结合力,严重情况下,如过度研磨造成铜包覆镀层厚度为零,极易在印制板受热后,造成镀层分离现象的发生(见图11)。

图11 铜包覆镀层厚度不足引起的镀层分离

铜盖覆镀层的常见缺陷是因塞孔树脂固化不良或镀层氧化,引起的铜镀层空洞,以及因树脂研磨不净或清洁不良,引起的盖覆镀层与包覆镀层之间的分离。由于树脂塞孔不足或铲平操作不当,引起的铜盖覆镀层的凸起或凹陷,应控制在一定范围内,以降低后续焊接时,因盖覆镀层平整度问题可能引起的虚焊、桥连、焊点空洞等问题的风险(见图12)。

2.5 凹蚀

图12 铜盖覆镀层空洞

凹蚀默认指正凹蚀,理想情况下镀覆孔铜镀层和内层铜箔之间形成良好的三面连接;允许单侧凹蚀阴影(凹蚀阴影未超过180°)的存在,即凹蚀应至少对每个内层导体的上或下表面产生作用,以保证可靠的连接要求,如图13所示。凹蚀的尺寸是沿内层铜箔接触区开始,测量至孔壁镀层与内层铜箔的最深接触点,最小凹蚀深度为0.00 5 mm;过度凹蚀不仅会造成孔壁异常粗糙,并且其产生的应力可能会引起内层铜箔的断裂,因此凹蚀深度不应超过0.080 mm(宇航用为0.040 mm)或规定的最小内层环宽(两者中取较小值)。

图13 正凹蚀

当去钻污使孔壁基材去除的深度小于沉铜前内层铜箔的蚀刻量时,便产生了负凹蚀。行业内常见的观点是正凹蚀比负凹蚀更为可靠,但并不绝对,因为相比正凹蚀,负凹蚀形成的孔壁更为平滑,且不会产生应力集中点,也有观点认为对于长期使用可靠性,负凹蚀更有优势。因此当布设总图未做凹蚀要求时,允许零凹蚀或负凹蚀的存在,如图14所示。负凹蚀过度,可能会在凹蚀连接处夹杂污染物,造成镀层空洞或镀层分离的缺陷,因此其深度也应控制在一定范围内(负凹蚀深度“X”应不大于0.013 mm,负凹蚀深度“Z”应不大于0.0195 mm)。

图14 负凹蚀和零凹蚀

为避免凹蚀工艺和芯吸作用共同引起孔壁非金属材料去除过度,造成导电图形间绝缘和耐压性能的降低,增大短路风险,由凹蚀和芯吸引起的介质去除量的总和,不应超过最大凹蚀允许量与最大芯吸允许量(0.08 mm)之和,如图15所示。

图15 凹蚀和芯吸引起的介质去除深度

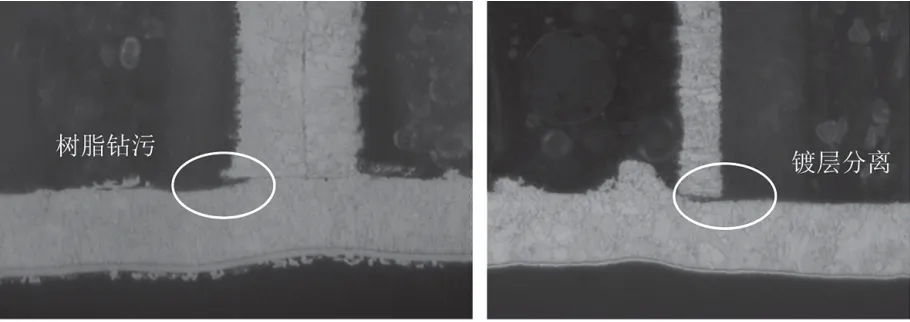

2.6 去钻污

附着在内层孔环上的树脂钻污,会破坏镀覆孔孔壁与内层导电层间的互连性,增大开路风险,因此热固性树脂基材印制板镀覆孔应清洁、无树脂钻污。去钻污和凹蚀是两个互为关联,但又相互独立的工艺;凹蚀工艺通常伴有去钻污的过程,但去钻污却不一定会产生凹蚀效应。与凹蚀工艺相似,为避免钻污去除过度造成孔壁异常粗糙,针对仅做去钻污处理未作凹蚀的印制板,去钻污使孔壁径向除去材料的深度应不大于0.025 mm。

因为材料特性原因,热塑性树脂基材印制板允许内层导体层处钻污残留不大于内层导体厚度的25%,但不允许内层导体层与孔壁镀层分离。对于上述树脂钻污和镀层分离的准确区分,可行的方法包括两种,首先是对形貌进行观察,相比树脂钻污,镀层分离的界面更为整齐对称,并且树脂钻污通常会填满分离面,而镀层分离的位置往往在微蚀后表现为空洞状态,如图16所示;更进一步的方法是借助能谱分析的方法进行确认,钻污处非金属材料成分应与基材处相同。

图16 树脂钻污和孔壁分离

当发现内层导体存在树脂钻污时,应做水平切片进行仲裁,钻污累积长度未超过孔环周长的33%(120°)可接收,如图17所示。

图17 水平切片仲裁树脂钻污(不可接收)

3 结语

所谓“基础不牢,地动山摇”,军用印制板标准是保证军用电子设备用印制板产品获得最优质量的基本保证。因此,熟练的掌握标准要求,灵活的应用标准制定更为严格、适用的产品鉴定和验收规范,也是供需双方协作共赢,实现最大经济效益的保证。