金属氧化物半导体场效应晶体管中总剂量效应导致的阈值电压漂移研究现状

刘一宁,王任泽,杨亚鹏,王 宁,冯宗洋,贾林胜,张建岗,李国强

(中国辐射防护研究院,太原 030006)

目前对硅半导体器件辐射效应的研究主要从空间应用的需求出发,相关研究对于核电厂应急响应中器件的选用有参考意义但也有不足之处。例如,由MOSFET构成的电机驱动器和运算控制器等是核电厂应急响应机器人的关键部件,应注意其总剂量(TID)效应,而空间应用关注的位移损伤效应(DD)、单粒子效应(SEE)和低剂量率损伤增强效应(ELDRS)等在应急情况下无需考虑,这也是应用于空间任务的耐辐射器件不适用于核电厂应急响应的一个重要原因。

MOSFET中的TID效应是在1964年被发现的,在接下来的五十年里,人们对它的认识也有了很大的进步,其ΔVth可以归因于MOS器件的界面电荷和氧化物陷阱电荷。并建立了一个通过可逆电子俘获进行补偿的模型[1]解释被俘获空穴的退火。除了基于硅的器件,虽然基于锗和氮化镓的具有高k介电层的器件还没有达到成熟的水平,但对其TID效应的研究正在迅速发展[2],所以也应予以关注。本文介绍了总剂量效应对不同类型MOSFET的阈值电压漂移的影响及计算机辅助设计技术(TCAD)的相关应用。

1 不同类型MOSFET中的阈值电压漂移

1.1 体CMOS工艺

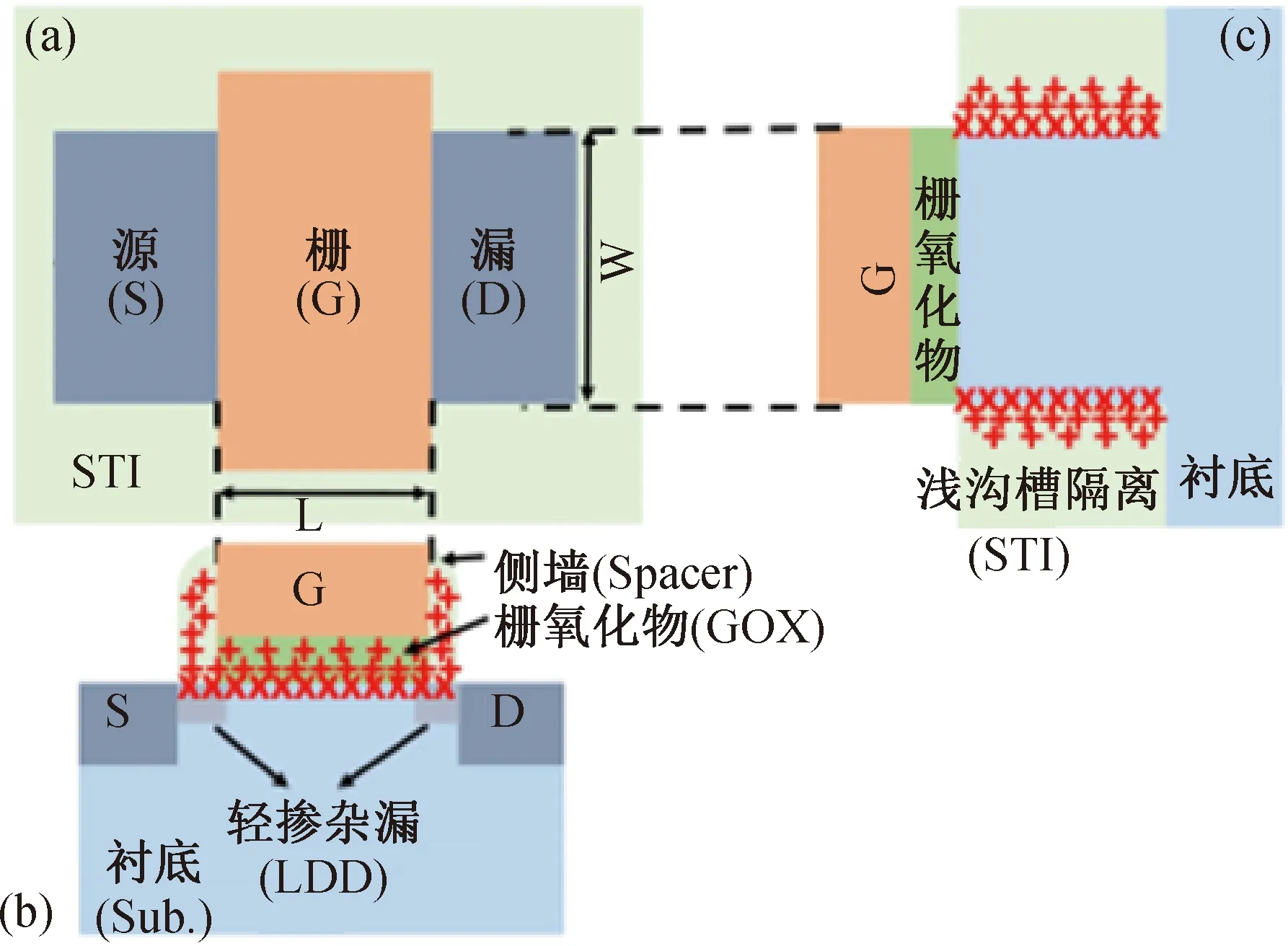

体CMOS工艺制备的MOSFET的总体结构和电荷俘获如图1[3]所示。氧化物捕获电荷Qot导致nMOSFET和pMOSFET的阈值电压降低,而界面捕获电荷Qit只导致pMOSFET的阈值电压降低并导致nMOSFET的阈值电压升高。

(a) 常用MOSFET的俯视图;(b)沿MOSFET长边的截面;(c)沿MOSFET短边的截面“+”表示氧化物捕获电荷(Qot),“×”表示界面捕获电荷(Qit)。图1 体CMOS工艺制备的MOSFET的总体结构和电荷俘获[3]Fig.1 The overall structure and charge capture of MOSFET manufactured by bulk CMOS process

图2[3]为工作在饱和模式下由28 nm体CMOS工艺制备的具有不同几何形状的MOSFET在不同TID下的ΔVth。图中所示的窄通道pMOSFET上明显的ΔVth是由于很厚的浅沟槽隔离(STI)氧化物中俘获的电荷,改变了STI边缘的电场,阻止了沟道的反转。

图3显示了商用350纳米体CMOS工艺制造[4]的不同几何尺寸的钻石形栅MOSFET的ΔVth作为TID函数。

可以发现,具有钻石栅形状的被测设备(DUT)的ΔVth与相应的传统矩形栅MOSFET相比更低(大约30%),这是由于抑制了“鸟喙区效应”[4]的寄生晶体管。且具有90°α角的栅形状效果最好。

尽管一些创新的晶体管设计,如上述钻石形状栅晶体管等可以显著减少TID导致的ΔVth,但是考虑到应急响应的成本因素,这些方法实用性较差。

如图4所示,其中栅长L=60 nm,制造工艺65 nm,偏置状态为“二极管”。辐照温度分别为25 ℃、60 ℃和100 ℃。分别注明了Qit和Qot的贡献。高温加速了质子从低掺杂漏(LDD)到栅氧化物界面的迁移[5],在该界面上质子使Si-H键去钝化。这一现象导致了界面陷阱的快速积聚,导致在24小时内产生数百毫伏的ΔVth[6]。

因此,由于辐照过程中的高温会导致ΔVth的恶化,在核电站应急响应中可能出现的高工作温度应予以考虑。

从图1到图4可以看出,更低的工艺节点也可以降低TID导致的ΔVth。而在体CMOS工艺中,在同一工艺节点下,沟道短窄的晶体管对TID的耐受力更差[7],这被称为辐射诱导的短沟道效应(RISCE)和辐射诱导的窄沟道效应(RINCE)。

图2 工作在饱和模式(|VDS|=1.1 V)下的(a)n型和(b)p型MOSFET的ΔVth作为TID的函数[3]Fig.2 TID-induced ΔVth of (a) n and (b) p types of MOSFETs in saturation mode (|VDS| = 1.1 V)

图3 不同栅尺寸的器件的ΔVth作为TID的函数[4]Fig.3 ΔVth of the devices with different gate geometry as a function of TID

图4 pMOS封闭布局晶体管的辐照中的ΔVth(上三图)和100 ℃退火过程(下三图)[5]Fig.4 ΔVth during irradiation (top three charts) and during 100 ℃ annealing (bottom three charts) for an pMOS enclosed layout transistor

1.2 绝缘体上硅(SOI)工艺

由于绝缘体上硅(SOI)技术对单粒子效应的敏感性较低,已在军事和空间电子领域应用多年[8]。使用130 nm部分耗尽(PD) SOI技术制造的T形栅nMOSFET的布局及其阈值电压变化如图5所示。

(a)顶视图;(b)左视剖面图;(c)正视剖面图;(d)阈值电压变化。图5 T形栅PDSOI nMOSFET的布局图及其阈值电压随剂量的变化[9]Fig.5 Layout and ΔVth during irradiation of T-gate PDSOI nMOSFET

对于SOI器件需要考虑浅沟槽隔离(STI)和埋氧化层(BOX)中的俘获电荷,因为在这些先进工艺节点中,这些电荷的效应已经超过前栅氧化物中俘获电荷的效应。

SOI器件前栅和后栅(埋氧化层)的TID响应不同。后栅主晶体管的阈值电压变化ΔVth,bg可表示为(1)式:

(1)

式中,Qf表示BOX中的净电荷量,Not,BOX表示BOX中的正电荷,Nit,BOX表示负电荷,CBOX表示BOX单位面积上的电容。

在PG(pass-gate)偏置状态下埋氧化层(BOX)中由辐照引起的净捕获电荷更多,而开启偏置(ON-bias)下STI中由辐照引起的捕获电荷比BOX中多[9]。

与上述典型的SOI MOSFET器件相比,具有长漂移区域的SOI横向扩散(LD) MOSFET有更大的Si/SiO2界面面积和更敏感的TID效应,并在辐照后具有更复杂的电特性变化[10]。

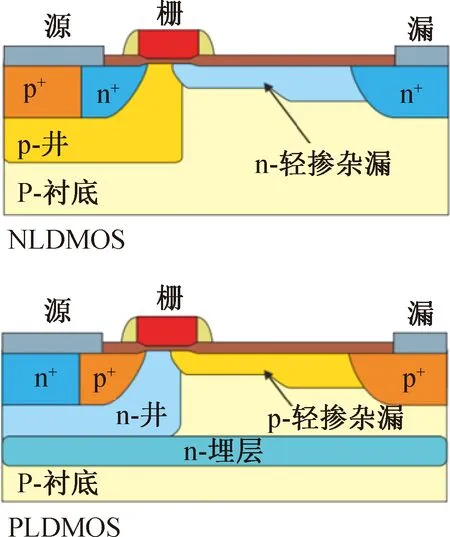

然而,一些具有高TID耐受性的LDMOS拓扑结构已经被开发出来。例如,P.Fernandez-Martinez等人描述了一种LDpMOS和一种LDnMOS,它们被设计为没有STI,但具有扩展的LDD的结构。这种结构减少了几Mrad辐照后阈值电压的降低。这种结构的布局和ΔVth曲线分别如图6和图7所示。在高达10 Mrad的照射后,它只表现出很小的ΔVth,而其饱和电流变化不大[11]。

图6 NLDMOS(上图)和PLDMOS(下图)器件的横截面原理图[11]Fig.6 Schematic cross section of the NLDMOS (top) and PLDMOS devices (bottom)

图7 |ΔVth|的测量值(实线)和模拟值(虚线)作为TID的函数[11]Fig.7 Measured (symbol) and Simulated (dashed line) |ΔVth| as a function of TID

对SOI器件的这些研究证实,是在STI和BOX等厚氧化物中捕获的电荷导致了所观测到的阈值电压降低。并且由于BOX的原因,SOI器件虽然具有更强的耐单粒子效应能力,但其耐总剂量效应的能力反而没有体CMOS器件强。

虽然在核电厂应急响应中不需要担心单粒子效应的影响,但是SOI器件的辐射效应在核与辐射应急计划和准备中是必须考虑的。这是由于超薄绝缘体上硅(UTSOI)技术目前仍是满足先进技术节点的电气性能和集成密度要求的单栅器件的唯一选择[12]。

1.3 纳米线(NW)场效应管

为克服目前10 nm以下技术节点(sub-10-nm technologies)缩放的限制,包括工艺整合、电学性能和成本效率等,一个可能的方法是结合多栅(multiple-gates)和超薄绝缘体上硅(UTSOI)结构的优点,制造一种具有多个栅并且在SOI基底上制造的纳米线(nanowire,NW)器件[12]。

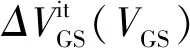

考虑到这样的的器件未来很可能应用在应急响应机器人中,研究NW MOSFET的辐照效应是很有必要的。图8描述了NWFET的结构和几何形状及阈值电压漂移随剂量的变化。

根据参考文献[12-13]的结论,窄宽度(WNW≤30 nm)和长通道(LG >=100 nm)的NWFET对TID导致的ΔVth的耐受力更高,这与体 CMOS工艺差异较大,对于体CMOS,在同一工艺节点下,沟道短窄的晶体管对TID的耐受力更差。其原因是,多栅结构一定程度上屏蔽了俘获电荷对器件电参数的影响,并减轻了辐射诱导的窄通道效应(RINCE)。

1.4 锗沟道场效应管

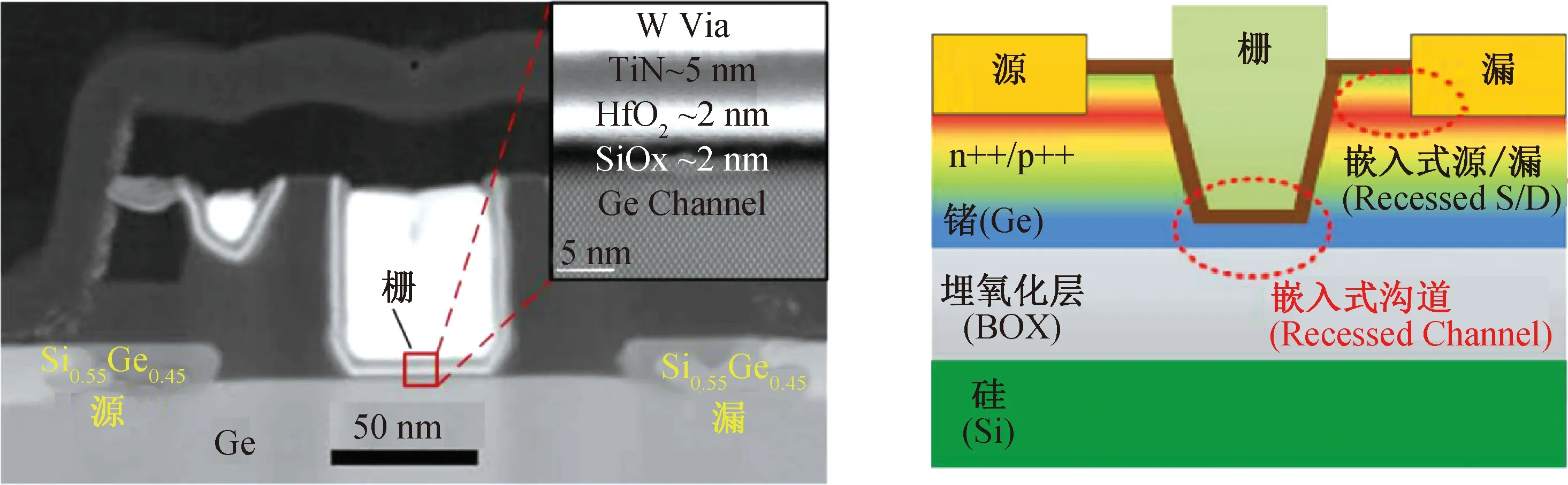

对于未来的高速应用场景,Ge通道MOSFETs是一个有前途的实现方式,因为与Si相比它们有更高的空穴迁移率,并且它们与传统的Si集成技术兼容[14]。Ge MOSFETs的一般结构如图9所示。

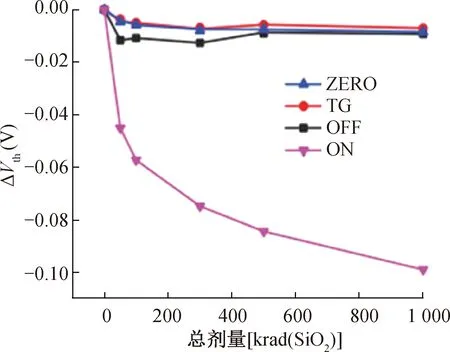

图10中显示ΔVth与受照剂量的关系。需要注意的是,只有ON-偏置才产生明显的ΔVth,而其他偏置几乎不产生ΔVth,而ON-偏置下的ΔVth源于负偏压不稳定性(NBTI)[14]。而后氧化(PO)退火过程可以显著减少与较厚的、有缺陷的GeOx界面层关联的俘获正电荷积聚[15]。

(a)原理图;(b)沿栅的横截面;(c)顶视图;(d)阈值电压漂移随剂量的变化。图8 多栅 SOI NWFET的结构及阈值电压漂移随剂量的变化[12-13]Fig.8 Description and ΔVth during irradiation of a multiple-gate SOI NWFET

图9 Ge沟道场效应管STEM截面图和采用凹槽形源/漏和沟道的GOI MOSFETs的横截面示意图[14-15]Fig.9 STEM cross section of Ge FETs and schematic diagrams of cross-sectional view of GOI MOSFETs with recessed S/D and channel[14-15]

图10 四种不同偏置条件下Ge通道器件的阈值电压随辐照剂量漂移[14]Fig.10 Threshold-voltage shifts of Ge Channel devices with irradiation dose under four different bias conditions[14]

1.5 镓沟道场效应管

氮化镓微波晶体管是一种典型的高电子迁移率晶体管(HEMTs),这种器件已经被研究了一段时间[16]。其基本的横截面原理图见图11。

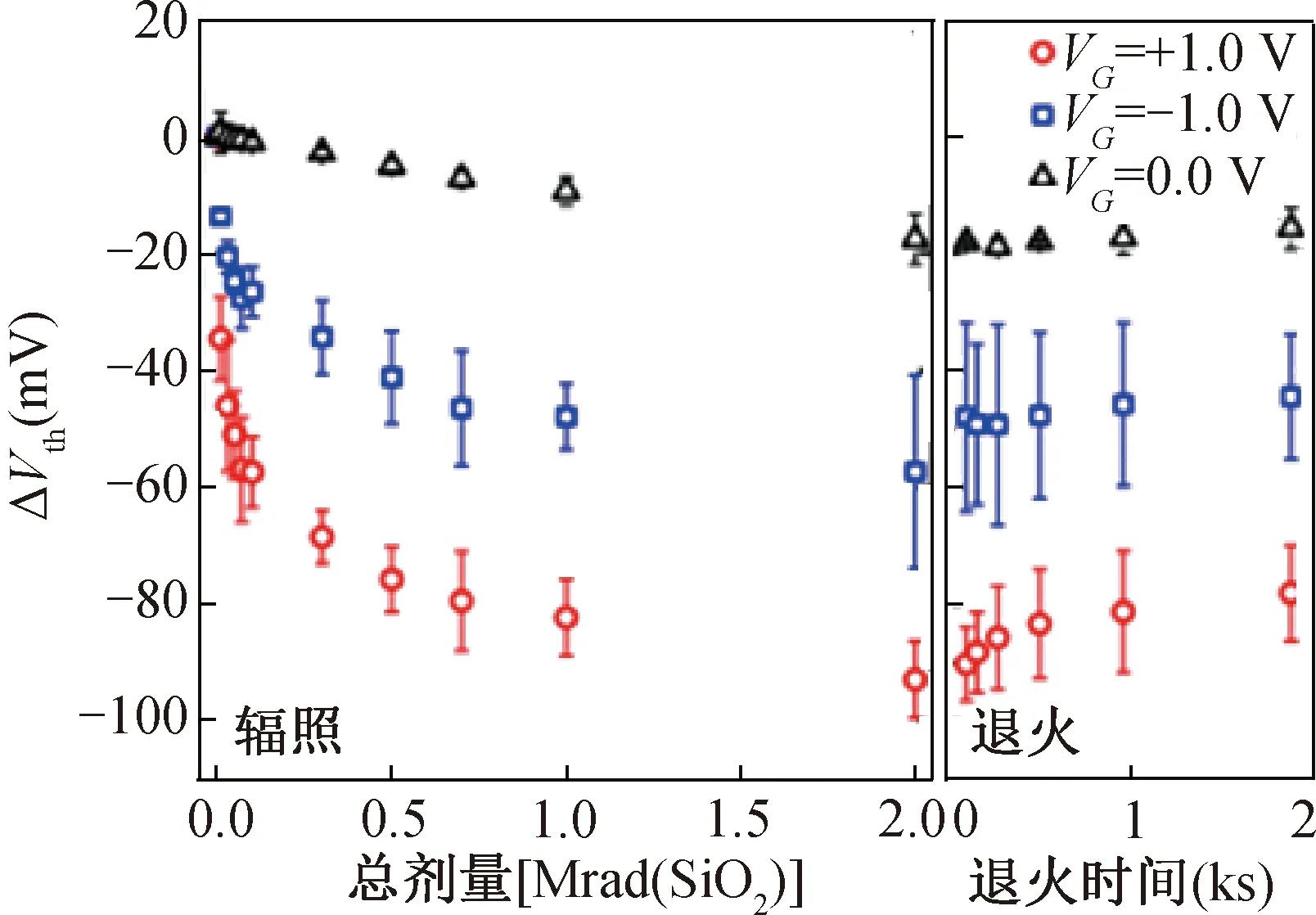

图12显示了偏压VG=+1.0 V,VG=-1.0 V,及VG=0 V偏置时,纯由TID导致的阈值电压偏移。值得注意的是,这些结果是修正了负偏压不稳定性(NBTI)的影响得到的,这种偏应力效应最近几年在部分文献中被考虑并修正,辐照过程中,正栅偏置时的这种效应比负栅偏置时更大[17]。

2 TCAD模拟

2.1 用于机理分析

由于计算机技术的发展,近些年辐照效应的计算机仿真越来越受到重视[2],借助与计算机辅助设计(TCAD) 技术的比较,可以解释某些实验结果。TCAD仿真在这一用途中被用于计算器件内的电场或俘获电荷密度[4,10,17-19]。

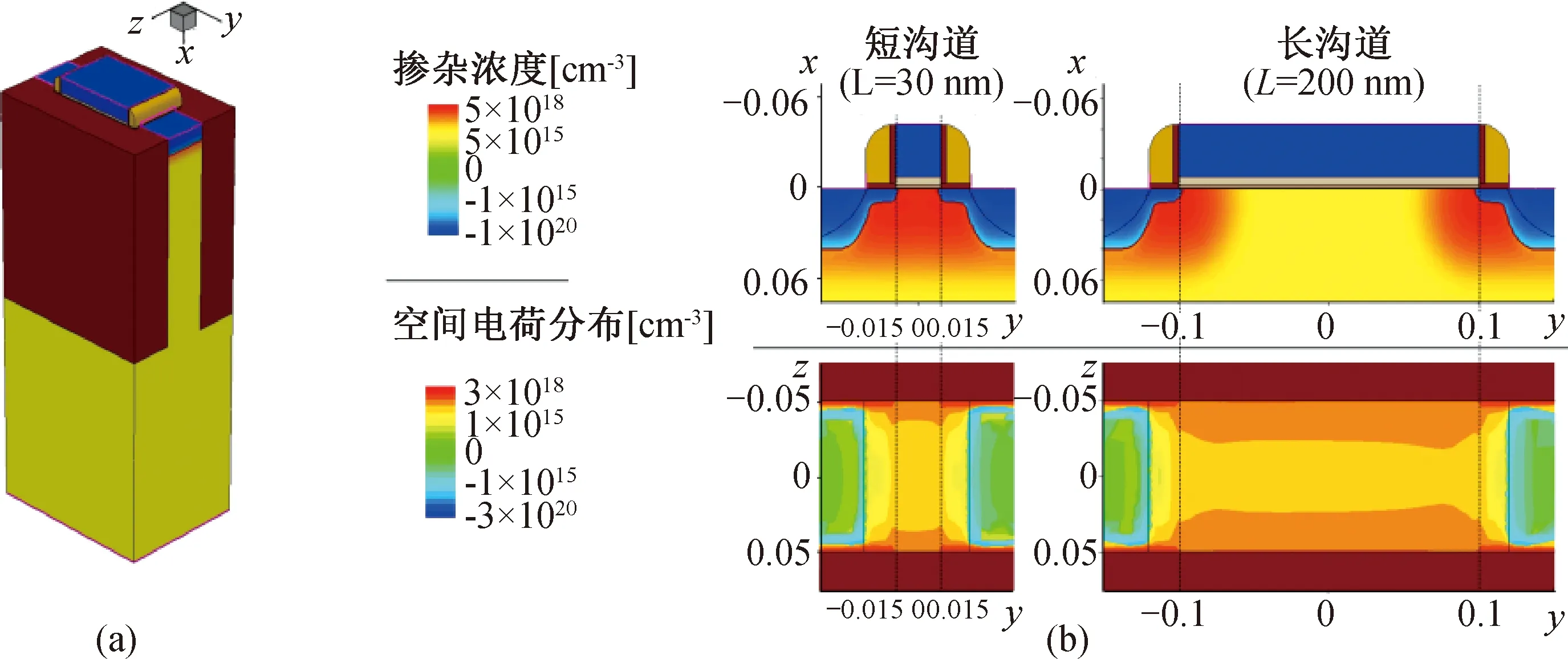

例如,通过带有晕环和STI的3-D结构来模拟28 nm pMOSFETs,图13[7]显示了它所模拟的3-D结构,以及L=200 nm的pMOSFET的z=0处的剖面图(上)和x=2 nm处的水平剖面图(下)。其中上图显示了长、短沟道pMOSFET中的掺杂浓度,下图显示了增量空间电荷密度,计算方式为辐照前后的空间电荷密度差。

图11 镓沟道晶体管基本的横截面原理图[16-17]Fig.11 The basic schematic cross section of the Ga channel FETs[16-17]

图12 偏应力修正的辐照中ΔVth作为辐照剂量和退火时间的函数[17]Fig.12 ΔVth as a function of irradiation dose and annealing time for bias-stress-adjusted irradiation[17]

这一方法可以解释更低的工艺节点如何缓解TID效应的对沟道长度的依赖(RISCE)。在28 nm制程的短沟道电晶体中,以红色为标识的晕轮几乎相互重叠,它们减少了由于沿沟道的STI中的固定电荷而引起的载流子浓度的降低,减轻了辐射诱导的短通道效应(RISCE)。

在TCAD模拟中,辐照后的器件通常通过在其STI中加入均匀体积密度的正电荷来模拟,或者沿着STI的侧壁添加一些正电荷。

2.2 用于模型验证

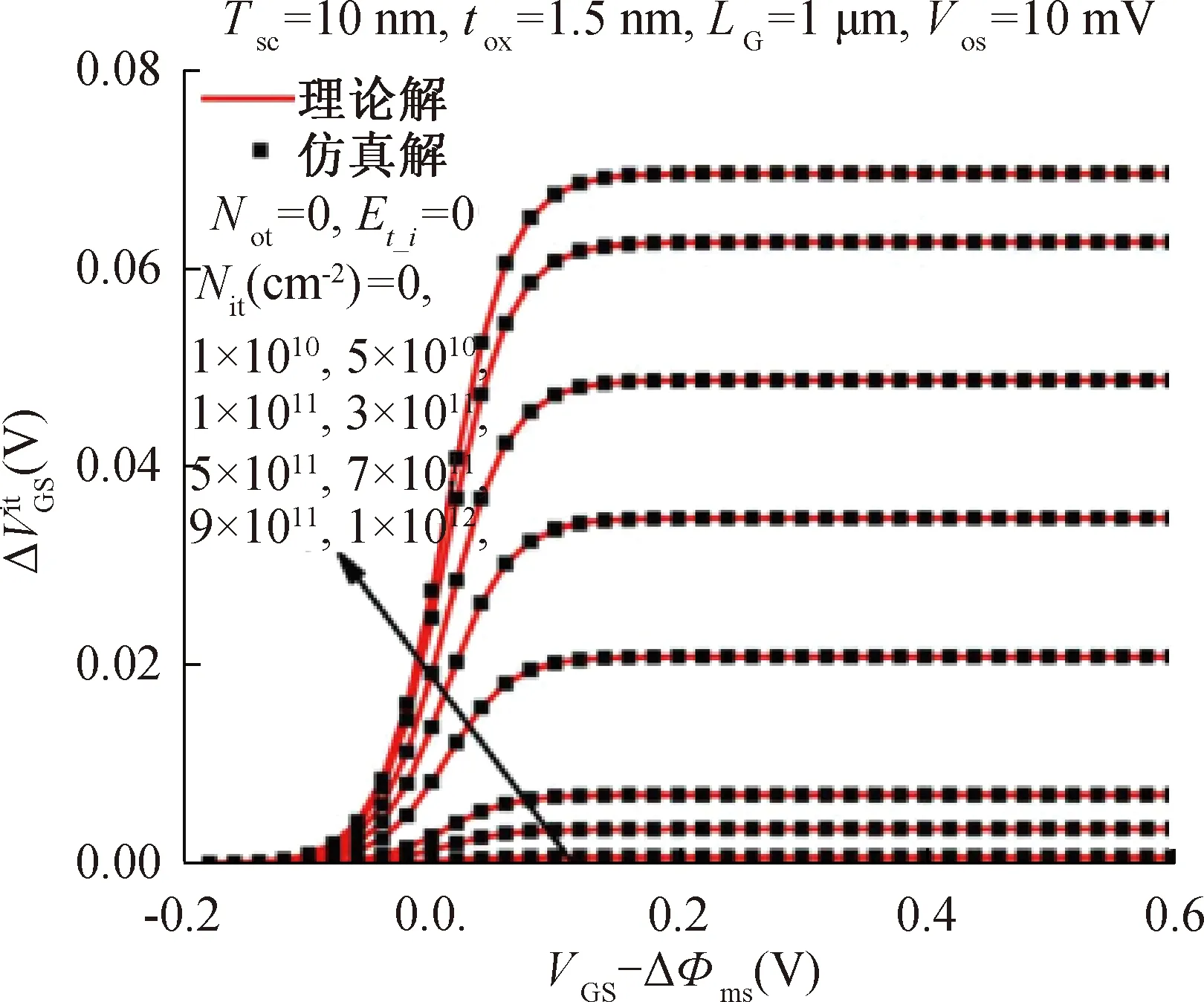

TCAD仿真还用于验证某些MOSFET 辐射损伤的数学模型[20]。比如从基本物理和基本模型的观点出发,在紧凑模型中使用基于电荷的显式表达式对双栅(DG) MOSFET进行建模,并通过与TCAD数值模拟的广泛对比来确认其方法的可靠性。

图14给出了阈下区域阈值电压漂移作为有效栅电势的函数的完整解析解和显式解,该电势在线性运算中对应相同的移动电荷密度。界面电荷诱导的阈值电压漂移分析模型如下:

(a)具有STI和晕轮的3-D结构;(b) z=0处的剖面图(上)和x=2 nm处的水平剖面图(下)。图13 28 nm pMOSFET的三维TCAD模拟 [7]Fig.13 A 3-D TCAD simulations of the 28 nm pMOSFETs

图14 界面电荷诱导的阈值电压漂移关于VGS-ΔΦms的函数[20]Fig.14 Shift in the VGS due to the interface charged traps with respect to VGS-ΔΦms

(2)

(3)

(4)

式中,Et_i为陷阱能量与本质费米能阶的差值,k为玻尔兹曼常数,T为绝对温度,VGS表示栅极电压,ΔΦms表示栅极与本征硅功函数的差,Vch表示沿沟道的准费米电位变化,UT表示热电压。

3 小结

我们比较了不同几何形状和不同缩放技术的MOSFET中TID对阈值电压漂移(ΔVth)的影响,认为采用先进工艺节点的体CMOS技术制作的芯片可能是核电厂应急机器人的最佳选择。注意到了栅宽和栅长对器件耐辐射能力的影响在体CMOS器件和NW MOSFET器件之间、高的和低的工艺节点之间的不同,并从RINCE和RISCE两方面解释了这种区别的原因。发现近年来前沿的一些研究在考虑辐射效应时,修正了负偏压不稳定性的影响,但是并非所有的研究者都考虑了这一效应。介绍了具有新布局几何形状的MOSFET中TID对ΔVth的影响,以及锗沟道和氮化镓沟道MOSFET等新器件中TID对ΔVth的影响。此外,还介绍了TCAD仿真技术用于器件辐射效应机理研究和建模验证的情况。这些研究可为开发核与辐射应急响应与准备的机器人提供基础。