超高带宽液晶显示逻辑驱动控制系统设计与实现

文 博, 魏 伟, 贾庆生, 张楷龙

(南京熊猫电子制造有限公司,江苏 南京 210046)

显示技术发展至今,从早期的CRT(Cathode Ray Tube)显示技术发展到今天的液晶LCD显示技术,直至当下的新型显示技术,包括OLED(Organic Light-Emitting Diode)、Micro-LED、量子点QLED(Quantum Dot Light Emitting Diodes)显示技术和激光显示技术,体现了消费者对追求极致显示的需求[1-2]。目前基于金属氧化物技术由于自身的高电子迁移率、高开口率、低功耗和低成本的特点,广泛应用于超高清超高刷新率领域[3]。本文主要针对目前主流的超高带宽8K×4K金属氧化物面板显示技术的驱动方案进行研究,着重解决了超高带宽的数据量传输以及数据和信号同步方式的问题,从而完成了系统方案设计,实现面板的驱动和显示。目前显示技术不断突破原有的显示标准,从FHD(Full High Definition)、UHD(Ultra High Definition)到今天的8K×4K显示,目前本领域的驱动方案都是以单芯片的方案实现面板逻辑驱动器设计,对于超高分辨率和刷新率的面板来说,成本十分高昂,并且驱动方案复杂[4]。本文研究了超高带宽的液晶面板的驱动方式,通过采用分区独立控制的思路,实现分区数据和信号的同步,并通过配合各外围电路模块的设计从而实现8K×4K面板驱动的功能。该技术方案可以降低现有技术方案的成本,复杂程度较低,同时也为以后的更高带宽的液晶显示技术驱动方案提供了一个具有参考价值的控制驱动思路和操作方式。

1 面板驱动方案

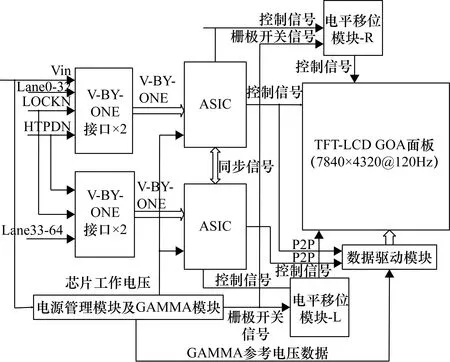

本文的总体功能方案设计采用100 in GOA液晶面板作为驱动控制对象,开展功能模块设计和开发工作,完成面板的显示和控制功能。如图1所示,功能模块设计包括高速信号输入输出接口模块、核心时序逻辑控制模块、可编程电源管理模块、GOA面板特有的信号电平移位模块和可编程灰阶伽马电压模块。高速信号输入输出接口模块接收外部的高速串行信号,通过核心时序逻辑控制模块的处理和转换,成为面板接收端的控制和数据信号,通过输出端口发送到液晶面板。核心时序逻辑控制模块针对输入高速信号进行解串和编码工作,完成数据格式的转换和面板端控制信号的输出。可编程电源管理模块将输入的电压进行转换,产生核心逻辑控制模块的核心工作电压和I/O接口电平以及GOA面板工作的控制电平。信号电平移位模块用于接收核心逻辑控制模块产生的时钟信号和控制信号,产生多路相位不同的面板驱动时钟,用以实现面板内部像素单元栅极开关电平的时序控制。可编程灰阶伽马电压模块接收电源管理模块产生的灰阶参考输入电压,并将输入参考电压转换成多路伽马参考电压作为面板的像素灰阶的参考电压,并且配合逻辑控制模块的控制信号通过面板源极驱动部分的DA(数模)转换成液晶面板的像素灰阶电压,实现面板的显示和控制。

图1 面板驱动方案总体框架示意图

(1) 液晶面板逻辑控制系统的总体方案。

本文设计的系统方案实现了100 in 8K@120 Hz超高分辨率液晶面板的驱动控制,由于尺寸较大,带宽较高,目前行业内没有单芯片的解决方案,主要是由于大尺寸超高带宽的传输对单芯片的工作频率要求较高,相对于双芯片的解决方案传输同样的数据带宽,单芯片的频率需要提高一倍,也就是说,在相同的工作频率下,双芯片的解决方案可以提高一倍的数据量。同时,即使存在这样的高规格单芯片,成本也远高于双芯片的方案。本文通过技术论证和方案的设计研讨,确立了双通道进行分区独立控制的设计思路,最终在数据信号和控制信号的同步下,完成了整个系统的功能设计。如图2所示,本系统主要通过输入接口模块接收高速的V-BY-ONE信号输入到液晶主逻辑时序控制模块完成数据信号的处理、转换和控制信号的产生,并将控制信号输出到电平移位模块实现了对GOA面板内部栅极驱动部分的控制,通过电源管理模块和可编程伽马电压模块提供的系统工作电压和像素的灰阶参考电压输出到面板,实现面板显示和控制。

(2) 核心时序逻辑控制模块设计。

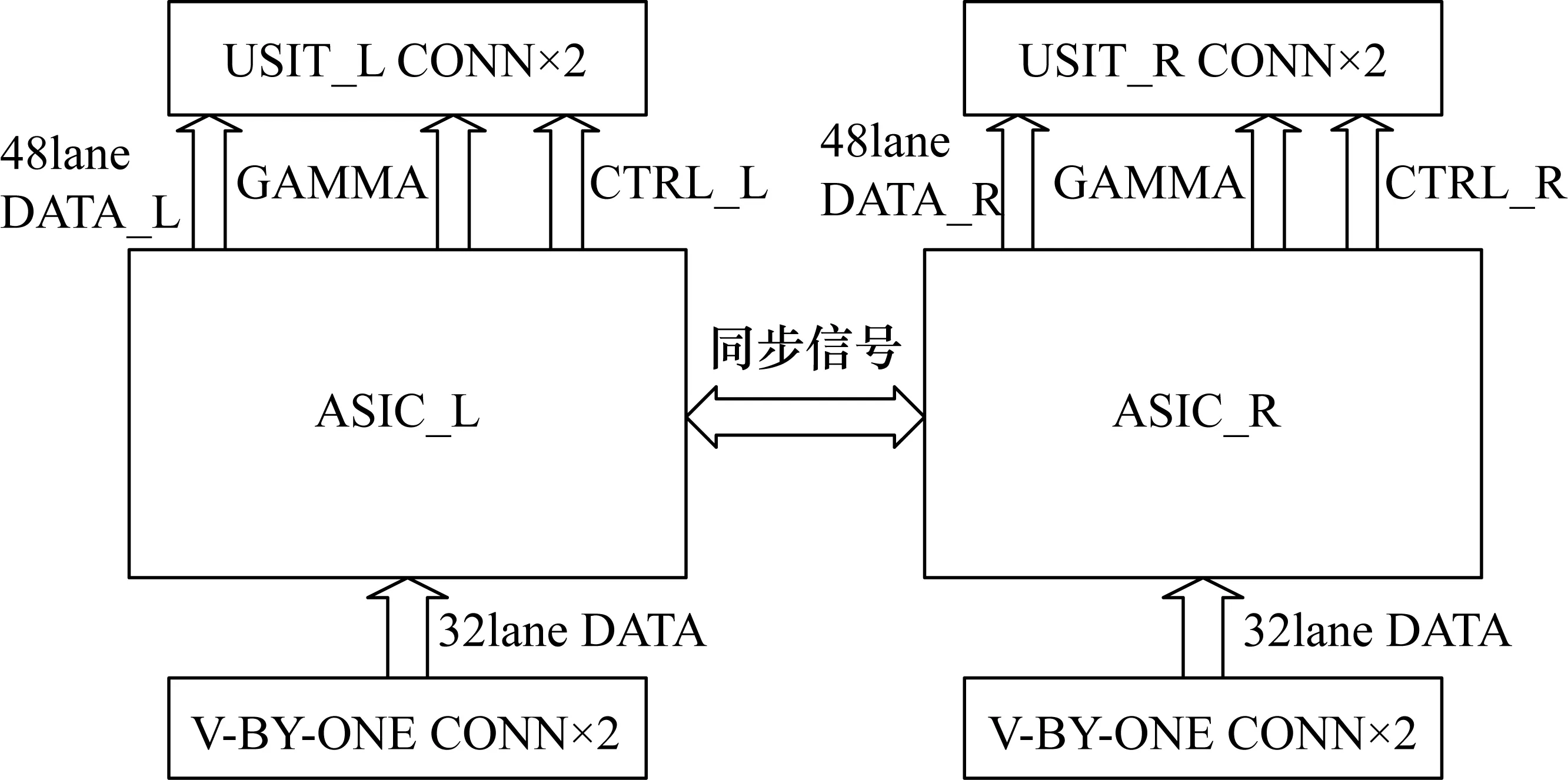

本文的核心时序逻辑控制模块采用8K时序控制器专用的TCON IC芯片作为主控芯片,基于该芯片完成核心时序逻辑控制模块的设计和开发工作,该芯片接口资源丰富,内置8051中央处理器,功能强大,性能可靠,适合超高带宽数据处理和传输。输入最大支持32 lane V-BY-ONE高速数据信号,数据速率达3.4(Gbit/s)/lane;输出最大支持P2P格式的48对USI-T协议的面板数据驱动信号,数据速率达3.1(Gbit/s)/lane;单芯片支持最高为8K(7680像素×4320像素)@60 Hz数据带宽。背光调节方面,支持48×48的区域动态背光调节功能,配合区域背光模组实现分区调光的功能。同时,支持双芯片数据同步级联功能实现更高带宽的数据传输。本文采用双芯片的解决方案,实现了8K@120 Hz的面板驱动显示功能。时序逻辑控制模块框图如图3所示,具体内容包括:核心控制器外围的最小系统设计(晶振、复位和存储模块设计)、双芯片信号同步方案以及控制信号设计。本文研究和实现100 in的驱动方案,由于面板尺寸较大,数据带宽容量较大,因此采用了区域分屏双边驱动的方式,主芯片负责驱动面板的左半部分,辅芯片负责驱动面板的右半部分。为了实现整个屏幕画面的显示,需要控制双芯片数据信号和时序信号同步的工作,本系统选用的专用IC芯片具有双芯片级联的同步功能控制引脚,将该功能引脚的数据信号和时钟控制信号级联,并通过阻抗匹配,在同步算法的控制下,最终完成信号的同步,实现了面板左右部分显示画面的整体融合。控制信号模块的设计主要是产生信号电平移位模块所需的控制信号(STV、CPV、LC和CLR等信号)和面板源极驱动模块的控制信号(TP、POL等信号),通过电平移位模块产生移位控制信号输出到GOA面板实现时序控制。本系统的时序逻辑控制模块完成了输入到输出信号的数据转换,并产生控制信号到电平移位模块,在电平移位控制信号输出控制信号和源极驱动控制信号作用下实现数据的传输和显示功能。如图4所示,主要针对时序逻辑模块控制部分的电路进行了方案的设计。

图2 驱动控制系统总体方案系统框图

(3) 高速信号输入输出接口模设计。

本系统为了实现8K@120 Hz GOA面板的显示,每秒钟需驱动7840×4320×3×120个像素点,传统的LVDS(Low-Voltage Differential Signaling)低压差分信号无法传输如此庞大的数据量的信号[5],因此,本系统的接口设计考虑可以传输更高数据速率和带宽的V-BY-ONE接口,该信号接口无专用的时钟通道,Source端的时钟和数据通过编码成特定格式(时钟嵌入在数据之中)的信号在接口数据通道上进行传输,sink端通过CDR(Clock Data Recovery)时钟和数据恢复功能完成数据的解码,并且只需要8 lane(传统的lvds信号需要48对差分线)即可实现4K的数据传输,从而实现较少的数据线完成了高带宽的数据传输,并且抗干扰能力极强[6]。针对本系统的超高带宽数据传输,输入信号共采用了4通道V-BY-ONE接口,每通道接口传输16 lane数据,共64 lane数据传输到时序逻辑控制模块的V-BY-ONE控制器。时序逻辑驱动器通过时钟和数据恢复将接收到的高速串行信号解码成低速的并行信号,并将解码后的信号通过主控IC进行图像算法的处理和数据格式的转换输出面板需要的96对USI-T协议格式的信号和控制信号,实现面板的驱动和显示。

图3 时序逻辑控制模块框图

(4) GOA信号电平移位模块。

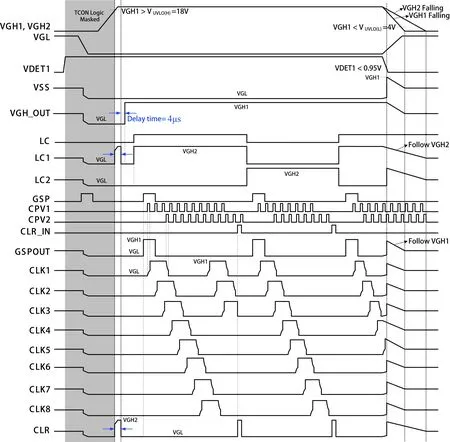

本系统针对目前主流的GOA面板进行驱动控制系统的设计工作,由于GOA面板上无外部的栅极驱动IC,可实现窄边框甚至无边框的显示效果,并且可以降低系统总体成本,已广泛应用于液晶显示的终端设备[7-8]。如图5所示,本文选用的超大尺寸GOA面板内部集成了栅极驱动IC,通过设计信号电平移位模块,实现对GOA面板内部栅极驱动的开关和信号的控制。该模块设计时考虑接收时序逻辑的时序驱动信号(STC、CPV、CLR、LC、CK等信号)和电源管理模块输出的像素开关电平信号(VGH和VGL信号),从而输出电平移位后的控制信号和开关信号。GOA面板集成栅极驱动部分,配合源极驱动模块的像素数据写入,完成图像的显示。针对这一功能需求,本设计选用的是立琦科技的集成型电平移位(Level Shifter)芯片RT8946,该芯片为宽电源范围供电,可在-18~40 V电压下工作,该模块接收时序信号和像素开关电平信号,输出8路不同相位的栅极电平移位控制信号(CK1,CK2,…,CK8)并配合像素开关电平信号,实现每8行为一循环周期的栅极扫描驱动方式。在本设计中,场频为120 Hz,共有4320行,故每一个行的扫描时间为1.93 μs,每个循环扫描的周期为15.4 μs,每个移位控制信号的相位相差为45°。图5为电平移位芯片输入控制信号和信号电平与输出的CK信号之间的需要满足的时序关系。

图4 时序逻辑控制模块部分电路设计方案

(5) 可编程电源管理模块设计。

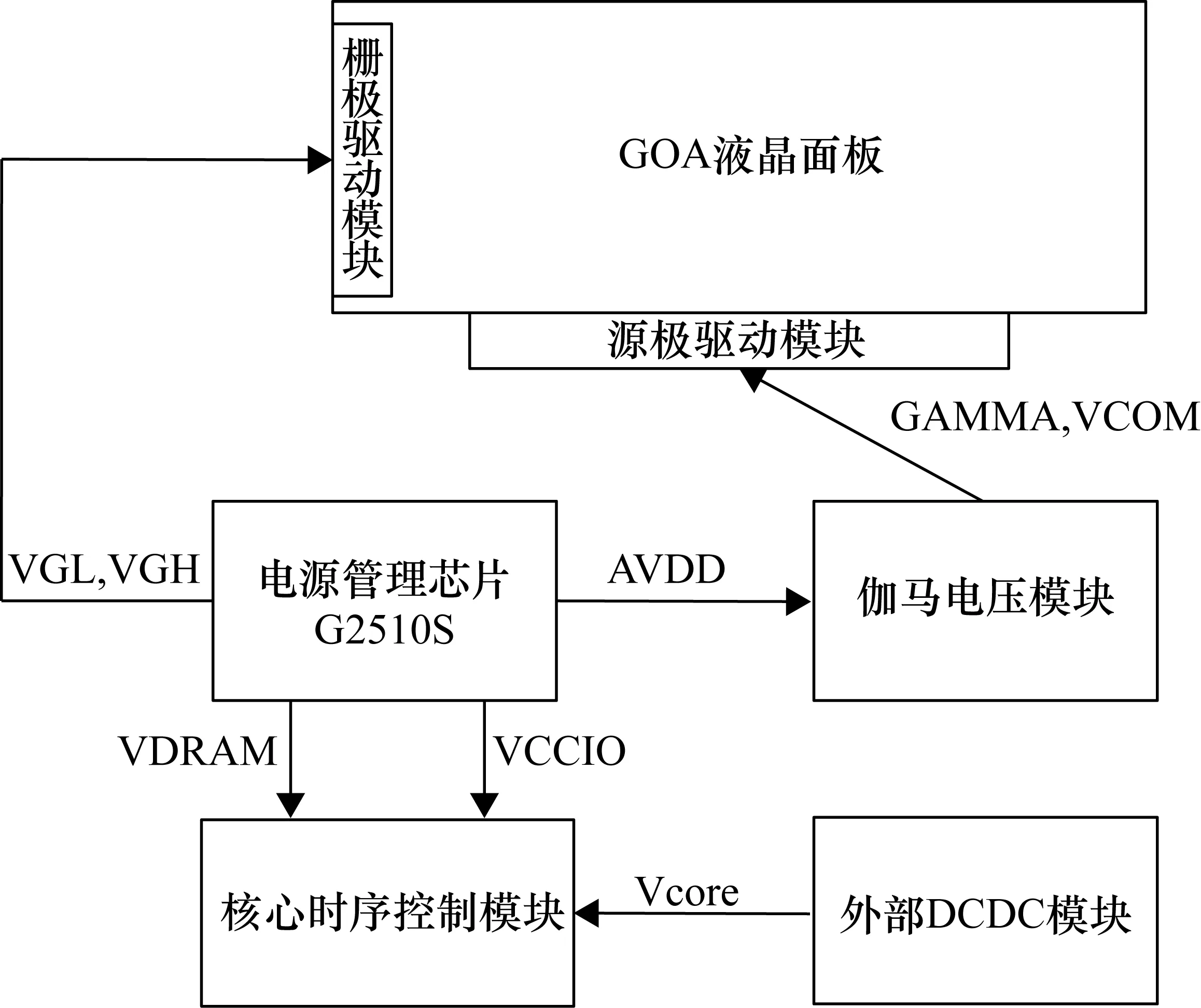

本系统的电源模块的设计在充分考虑了主控制器IC所需的核供电电压和普通I/O口的电压之外,还需要提供给各功能模块工作电压以及面板像素单元所需的开启和关闭电压。针对本文具体的设计而言,整个逻辑控制系统所需的电压包括主控制芯片IC的普通I/O口电压VCCIO(3.3 V)、内核供电电压Vcore(1.2 V)、IC内部的DRAM(Dynamic Random Access Memory)接口电压VDR(1.5 V)、可编程灰阶电压模块的工作电压AVDD(15.6 V)、GOA面板内部像素单元的开启电压VGH(25 V)和关闭电压VGL(-6.1 V)。针对这一需求,选用了致新科技的PMU电源管理芯片G2510S并配合DC-DC BUCK降压芯片来完成系统所需的多路电源管理管理模块的设计和开发工作。本系统的电源模块依然采用双芯片的独立控制方案分别为双主控制芯片进行独立的供电工作,图6和图7为单通道电源管理方案。

图5 控制信号输入输出时序逻辑示意图

(6) 可编程灰阶电压模块设计。

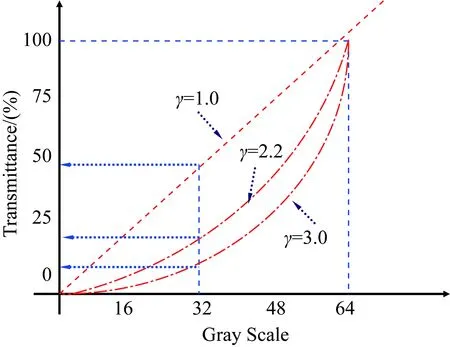

自然界的灰阶是连续的,但是在显示器重现图像的时候,却无法做到完全连续,只能从最亮和最暗的范围内增加区分的层级,也就是减少亮暗区分的级距来增加灰阶的数目[9]。区分灰阶的数目为2n。经过试验,人眼感觉与亮度之间的关系式为

y=AxΓ

(1)

式中,A为常数;上述表达式标明的关系曲线即为Γ曲线;人脑的Γ介于2.2和2.5之间,由式(1)可得:

图6 单路电源管理模块框图

x=(y/A)1/Γ

(2)

式中0.4≤1/Γ≤0.45,式(2)表明的意义是要让大脑感觉x线性增加,必须使亮度y按照1/Γ次方变化[10]。由于影像信号要表达的是人脑的感觉,需要依据亮度与大脑感觉的Γ曲线进行校正,使大脑感觉与影像信号成正比[11]。因此,人脑感觉与显示器的亮度有关。因此,在TFT-LCD中,将电压-透过率曲线作为GAMMA校正的参考。为了满足显示产品的规范,通常选择γ=2.2[12-13]。灰阶电压与透过率的对应的GAMMA曲线如图8所示。

图8 灰阶电压与透过率的对应的GAMMA曲线

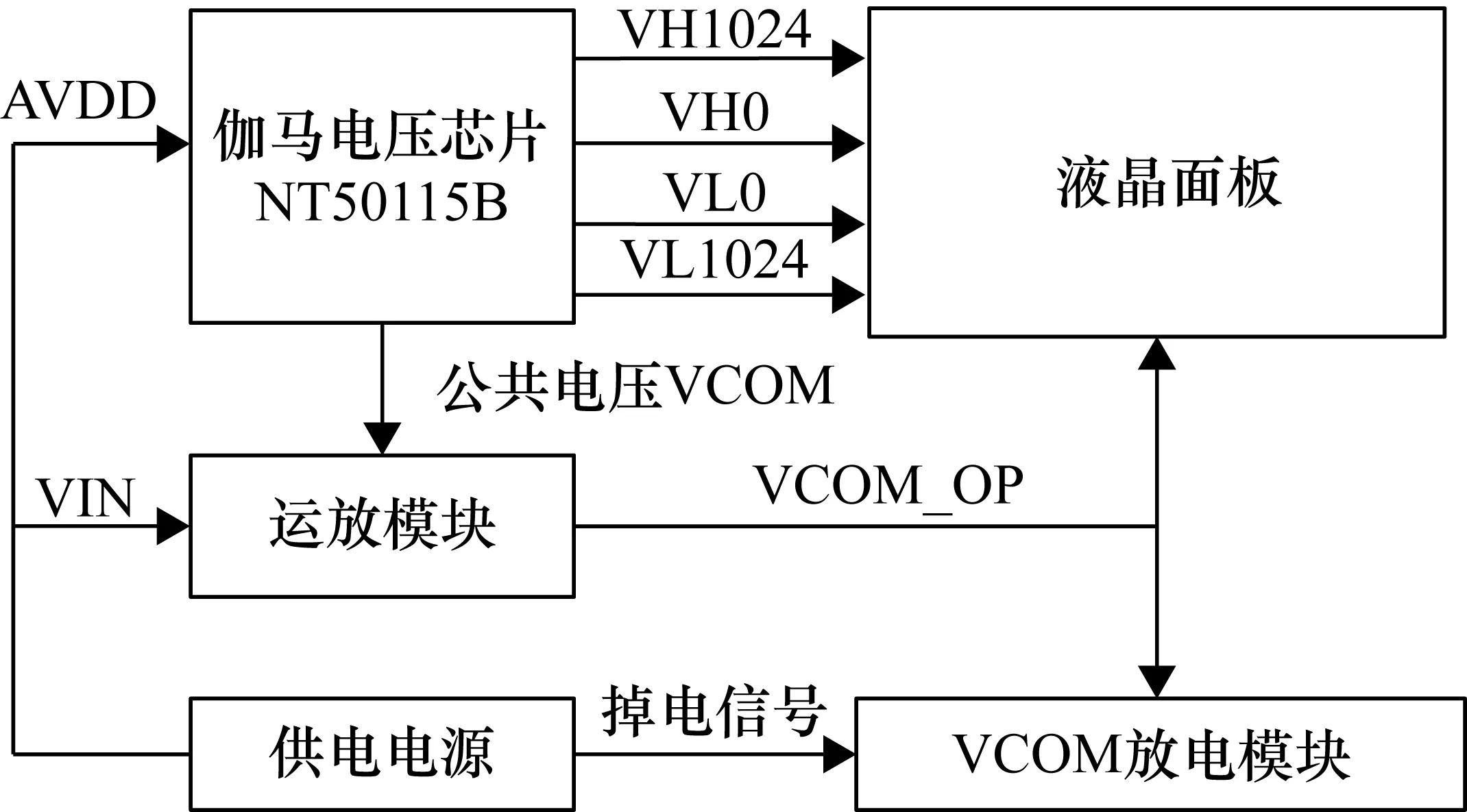

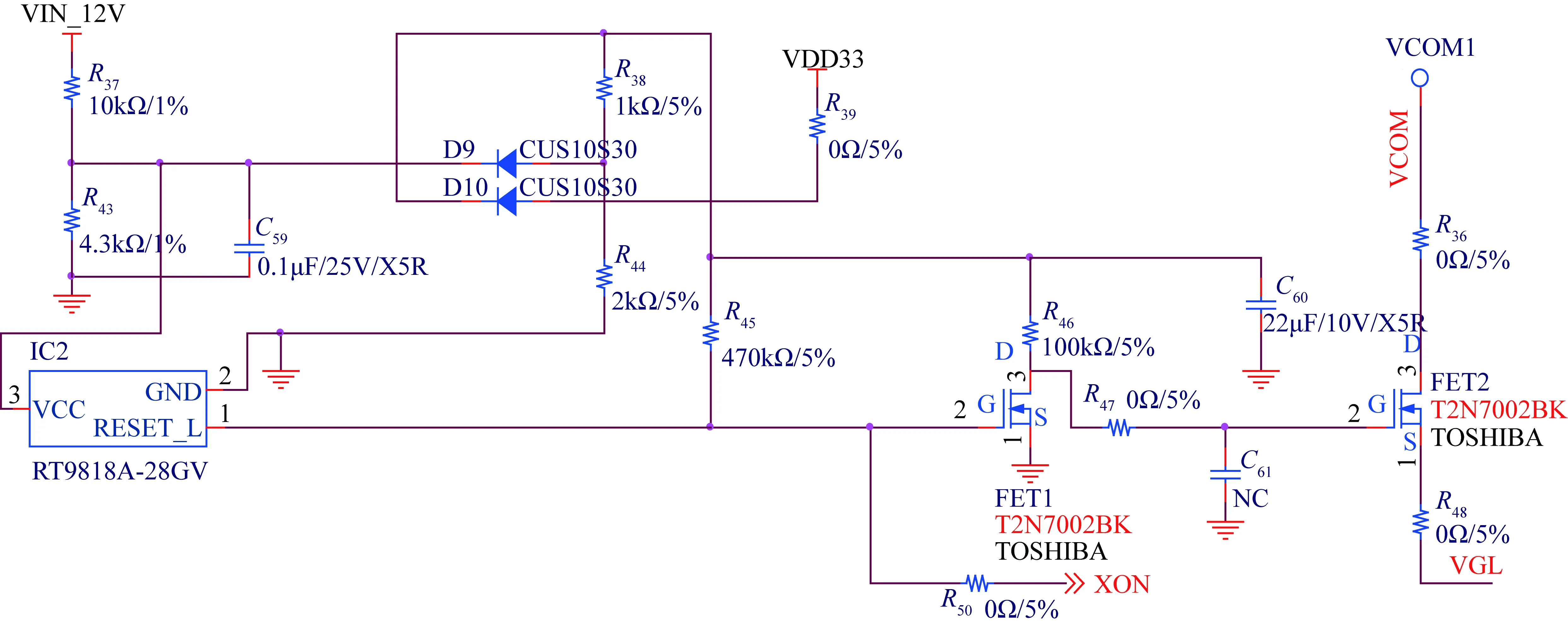

如图9所示,本系统10 bit位宽的GOA液晶面板显示的灰阶达到1024,因此通过联咏科技50115B芯片的A/D转换产生4路数字参考电压为(VH0,VH1024,VL0,VL1024)作为面板源极像素的灰阶参考电压。并且,考虑到超大尺寸液晶面板的自身的特点以及驱动能力的问题,采用致新科技公司的G1583运放芯片来实现公共参考,VCOM电压的放大提升了对面板的驱动能力,确保了负载端公共电压的稳定,改善了显示质量。在面板关机掉电中,为了解决面板关机残影的问题,本系统通过将放大后的VCOM通过放电回路电压快速释放,从而有效地消除了关机残影的现象。由于本系统为分区控制,故选用了2块501115B芯片进行了双模块的设计从而实现分区的显示和控制。图10为面板VCOM掉电控制的具体设计原理方案。

图9 单路伽马电压模块电路框图

图10 面板VCOM掉电控制方案

2 设计结果及功能测试

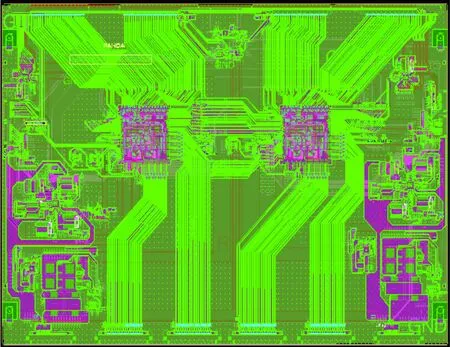

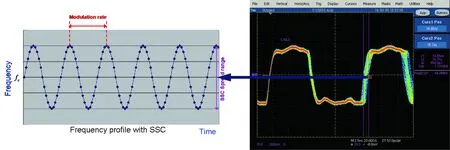

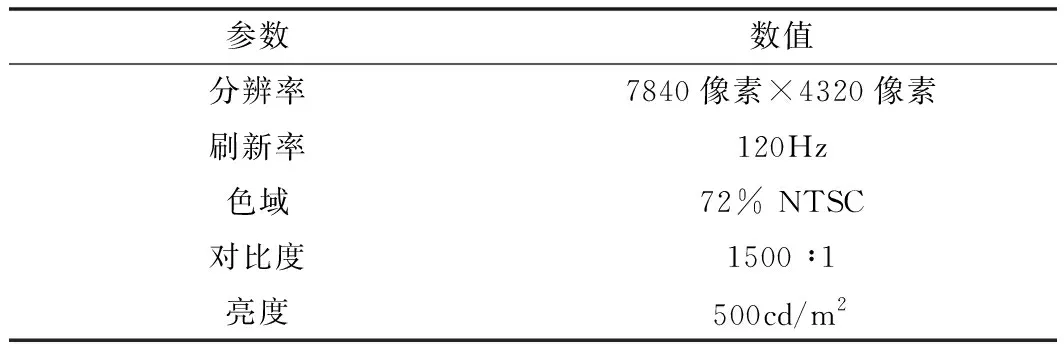

本文最终使用设计的超高带宽液晶显示逻辑驱动控制系统模块来驱动100 in 8K×4K GOA面板,通过信号源端输出的V-BY-ONE信号输入到控制模块,最终输出高清的P2P屏端数据信号完成液晶面板的驱动和显示,如图11所示。如图12所示,本系统充分考虑了产品的兼容性测试的要求,通过系统的展频方案的结果测试,确保系统的产品满足EMI的标准和要求。最终,通过该控制系统和8K×4K液晶面板的一体化整合对整个显示系统进行光电性能测试,相关性能参数满足产品的设计要求,如表1所示。

图11 面板驱动系统模块PCB效果图

图12 面板驱动系统时序驱动电路的展频实测图

表1 主要光电参数

3 结束语

基于专用的高端时序逻辑控制芯片,针对中大尺寸超高带宽GOA液晶面板采用双分区同步控制的双芯片的设计思路,突破了传统单芯片设计方案和思路,结合输入输出接口模块,可编程电源管理模块、GOA信号电平移位模块、可编程灰阶电压模块,完成了100 in 8K@120 Hz液晶显示逻辑控制系统的设计,实现了驱动控制系统的总体功能。本方案主要针对高端液晶面板市场,满足了超高清视频信号传输的应用需求,有效地切合了未来液晶显示的发展趋势和方向。本文设计驱动控制系统相对于单芯片方案具有低成本、低时延、驱动方案简单、功耗小等优势。目前,本文开发的逻辑驱动控制模块已通过产品级的功能和性能测试,性能稳定可靠,绿色环保,符合相关电气和辐射国标安全认证要求,市场应用前景广阔,同时为更高带宽的驱动系统方案设计提供了一个新的思路。