高速电路系统设计中的端接匹配分析与选择探讨

赵明松

摘要:高速电路系统设计中端接匹配选择十分重要,对于整个电路系统的设计应用都有非常重要的意义。本文笔者针对高速电路系统设计中端接匹配选择进行分析,文章中简要阐述高速电路系統的组成,同时对端接匹配进行分析,同时也总结端接匹配的设计分析。

关键字;高速电路系统;端接匹配;设计分析

电路系统设计中,针对端接匹配方式进行选择和设计非常关键,能够在一定程度上解决信号反射问题,提升系统的信号接收能力和整体工作能力。而在当前电路系统设计的端接匹配中,主要包括电路系统串行端接匹配、并行端接匹配等方式,不同的端接匹配形式具有不同的特点,对于电路系统的抗干扰影响也不同。所以,在实际的电路系统设计中,应该根据电路系统的电磁干扰需求、完成对端接匹配的选择。

1.高速电路系统设计组成要点

高速电路系统设计对于整个高速电路系统设计应用有非常重要的作用,一定程度上关系到高速电路系统的功能设计。而在实际的系统设计中,信号质量、电磁干扰等方面的设计非常关键。尤其是电磁干仍预防方面的设计对于整个系统的安全稳定运行有十分重要的作用,能够做好对系统的综合应用管控,确保设计更加合理。同时,在进行高速电路设计过程中,影响电磁干扰的主要因素除了线路板层、电力元器件之外,也包括端接匹配方式、合理的端接匹配方式设计,能够减轻反射信号影响,提升电路系统的工作稳定性。

高速电路系统设计过程中,端接匹配设计十分重要。在整个电路系统进行设计过程中,电磁干扰源、耦合路径、接收装置的应用实现了整个电磁环境的设计应用。而在系统设计中,电磁信号的发射和接收会受到电磁环境干扰。而如果在设计过程中,电磁辐射干扰将会受到信号反射影响。所以,在电路系统的综合设计中,利用端接匹配设计,能够完成系统的综合设计管控,确保设计应用更加积极合理,也能够提升设计效果。在其设计中,根据系统的电磁环境,完成对端接匹配模型的良好设计,确保模型设计应用合理。

2.端接匹配方式分析

在高速电路系统进行设计过程中,端接匹配设计过程中,应该注重对匹配接口进行综合设计,确保设计应用更加合理。而在现代化端接设计中,不同的接口形式不同,其功能特性也不同,以下是对端接匹配接口的良好设计应用。

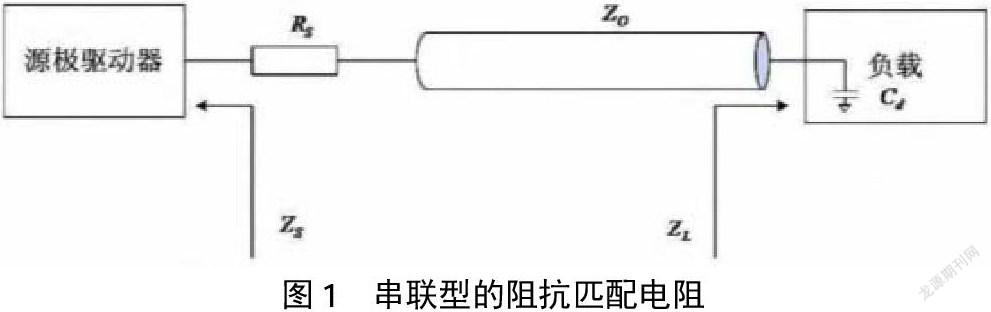

(1)串行端接匹配

串行端接匹配是一种常见的端接阻抗匹配方式,其主要包括源极驱动装置、负载控制装置以及阻抗匹配电阻组成。以下图1为串行端接匹配原理图。在串行端接连接之后,使用源极驱动装置进行电力负载,从而实现阻抗匹配。同时在串行端接应用过程中,为了实现最好的匹配新效果,对于高速PCB电路板布线也有一定的要求。匹配电阻应该与源极驱动装置保持最近的距离,匹配电阻的大小一般都在10欧姆-75欧姆范围之内。同时在进行电阻设计过程中,为了防止电路形成自激振荡问题,需要设计输出阻抗,提升设计效果。

串行匹配电阻的主要优点在于其本身的结构相对比较简单,采用串联的方式将整体端接匹配模块联系到一起、而在其应用过程中,串联端接方式在高速运行状态下,信号方式相对平缓、从而能够起到稳定电压的作用。而在其低速系统运行中,其本身也比较稳定。而在进一步的研究表明。在整个系统中,串行端接匹配,信号源端到终端的传输相对延迟、从而容易造成输出逻辑混乱等问题,所以一般情况下,串联端接匹配更适合应用低速系统电路当中。

(2)并行端接匹配

并行端接匹配形式也是一种常见的端接匹配方式,在其进行匹配过程中,也是采用直流匹配方式进行设计,在级间匹配设计中,负载端的电路输入阻抗相对比较大,所以将负载端与匹配电阻进行并联。在实施并行端接匹配过程中,是在PCB线路板信号传输导线中安装了特征阻抗。要求在端接电阻设计中,要求端接电阻与负载端下拉电阻保持一致,从而减少信号反射问题。

并行端匹配电路设计附加一个并联端接匹配电阻、为满足极间前后极门限电压、完成对高电平的充足供应。从而提升整个电路系统的稳定性。在并行端接匹配应用过程中,其本身的应用优势在于分布负载、 并联端接电阻电源上拉连接方式也能够完成设计应用。同时在并联端接电阻设计中,可以落实好各项设计原则,同时在信号传输设计中,连接电源也具有良好的消除反射信号功能,确保消除信号反射的同时也能够降低噪音。

(3)RC端接匹配

RC端接匹配也被称作为交流端接匹配、在RC端接匹配应用过程中,主要是以并行端接匹配方式为基础的优化匹配方式,在二者进行匹配过程中,针对前者进行了升级,主要是从降级电路损耗控制方面进行了技术升级,通过技术升级管控,确保二者的良好升级应用更加合理,也能够最大程度上提升设计质量。RC端接匹配进行设计中,设计了其端口的总体有点,RC端接匹配具有噪声容限低、功能消耗大的问题,同时功耗也主要包括布线设计,提升设计质量,确保设计应用更加合理,也能够提升设计质量。在进行综合设计应用过程中,采用分布负载和总线布线的设计应用。同时在其进行综合设计中,也包括RC端接匹配缺点综合设计,提升设计质量。在其进行综合设计中,更可以完成对其端接的综合设计。

(4)戴维宁并行端接匹配

戴维宁进行并行端接匹配设计中,需要注重电阻分压器端接匹配设计。在其进行设计中,也是对并行端接匹配进行综合设计,确保设计应用更加合理。在进行戴维宁并行端接匹配设计中,电阻语言电源构成上拉形式、同时在电阻进行设计中,并行端接逻辑高电平和逻辑低电平进行了目标负载符合,确保其设计应用更加合理,也能够最大程度上提升端接匹配设计效果。在并行端接匹配设计中,主要优势在于能够吸收传输波,同时消除反射。在戴维宁并行端接匹配中,负载可以通过驱动多扇、完成对分支短线沿线分布设计,确保设计应用更加合理,提升设计效果,确保短线的综合设计应用更加合理,也能够提升源端器件驱动能力的综合设计,通过各方面的设计,确保源端器件驱动能力设计符合设计标准,确保其综合设计更加合理[1]。

3.端接匹配的合理选择

端接匹配对于高速电路系统设计有关键的影响,所以在系统的设计过程中,应该注重对端接匹配的合理选择,提升端接匹配的在综合设计效果,对于系统的抗电磁能力以及发射信号消除能力提升有重要的作用。在进行选择过程中,应该从成本、系统功率需求以及功能特性进行分析设计,确保端接匹配设计合理。其具体的设计应用过程中。上述总结了串行端接匹配、并行端接匹配、RC端接匹配、戴维宁端接匹配等多种匹配方式,而不同的端接匹配具有不同的匹配方式,同时各信号端接方法也适合应用不同的高速电路。以下是对不同端接方式的比较,针对端接运行成本、增加延迟效果、功率需求、以及特性进行了比较。分析中将各端接比较分为高、中、低三个档次[2]。

①串行端接匹配成本相对比较低、增加延迟效果,对于电路系统的工作功率需求相对比较低,并且的串行端接匹配直流噪声极限特性相对比较好。

②并行端接匹配成本也比较低、增加延迟效果相对比较小、但是对于电路系统 工作功率需求比较高、所以从整体而言并行端接方式的功率消耗相对比较大。

③RC端接匹配成本控制中等,成本与其他两种方式相比适中,增加延迟效果相对比较小,对于电路系统 工作功率需求比较高。而与其他两种并行方式相比较而言,RC端匹配降低带宽的同时也能够呈现容性,这是一种良好性能。

④戴维宁端接匹配成本相对比较高、增加延迟功能比较小、而对于系统的功率需求比较低、戴维宁端接匹配实施过程中,存在有极限过冲现象,一定程度上提升极限过冲效果。

在进行端接匹配的选择过程中,可以根据上述特点总结進行端接匹配应用,确保端接匹配的综合设计更加合理[3]。

结束语

本文笔者针对高速电路系统端接匹配进行设计,文章中简要阐述了高速电路系统的综合设计应用,在电路系统的综合设计中,应该注重系统的综合管控设计,确保电路系统的设计应用更加合理。

参考文献

[1]黄世瑜. 高速电路系统设计中的端接匹配分析与选择[J]. 2021(2017-1):157-161.

[2]王若溪. 微通道板CMOS读出电路的研究与设计[D]. 吉林大学, 2019.

[3]王祎帆, 王杨, 王强,等. 基于Hyperlynx的高速电路端接技术仿真研究[J]. 汽车文摘, 2020(5):6-6