基于可见光通信的LED载流子清除电路设计

刘正翔,陈建国,王洪丽

(1.福州职业技术学院 机器人学院,福建 福州 350108;2.福州大学 电气工程与自动化学院,福建 福州 350108)

0 引 言

自Tanaka等[1]提出可见光通信(VLC)技术以来,由于其不占用传统无线通信频带,且绿色环保、保密性好,使得该技术得到飞速发展。可见光通信使用可控的、快速闪烁的LED传输信息,由于人眼无法感知其高速闪烁状态,使得LED既可用于照明,又有快速传输信息的功能[2-3]。迟楠等[4]总结目前国内外的可见光通信研究进展时指出可见光通信急待解决的问题之一就是如何提高LED调制带宽和系统传输速率。Tanaka等[5-6]也意识到LED调制带宽受限,且在频率较高情况下,LED无法完全熄灭是因为载流子无法及时释放,导致LED端电压无法快速下降。为解决该问题,Tanaka设计了一种用于可见光通信的高速LED载流子清除电路,在LED熄灭瞬间导通MOS管,使LED正负端短路而形成载流子快速释放回路。该设计虽然可快速缩短LED端电压下降时间,但该电路使用3个大功率高速MOS管驱动LED,不仅价格昂贵,且功耗较大。随后Halbritter等[7]提出一种基于电容峰值技术的LED驱动电路,虽然也可快速释放载流子,但该电路为获取峰值瞬间电流,要求电路具有较大电流,被动增加电路复杂度,且为防止LED被击穿,需内部封装ESD保护。

目前,国内在利用载流子清除方法来改善LED驱动电路性能的研究比较少。谢鑫[8]虽然指出载流子清除电路可用于增加传输速率,但并未深入研究该部分内容。夏忠金[9]主要研究Tanaka设计之电路在蓝光、紫光LED下的载流子清除性能,但未对降低成本与功耗方面做深入研究。为了获得较低成本和功耗的LED驱动电路,本研究在不额外增加MOS管的情况下,设计了LED改进电路,在LED熄灭瞬间即接入载流子释放回路(短路),可使LED快速完全熄灭,进而提升系统性能。

1 LED发射速率受限原因分析

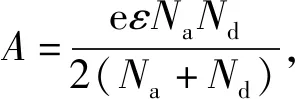

当LED内部PN结附加的正偏电压增大至PN结的接触电势差UD(1.7~2.0 V),耗尽区宽度减小为零。若正偏电压继续增大,P区空穴和N区自由电子即可越过PN结,进行空穴与自由电子的复合而释放出光能。正是由于自由电子与空穴(载流子)的运动,形成了结电容,单位面积结电容计算如式(1)、式(2)[10]所示。

(1)

(2)

式中:Na和Nd分别是P型和N型半导体掺杂浓度;e为1.6×10-19C;ε是材料介电系数;U是LED的正偏电压。考虑到给定材料的LED参数e、ε、Na、Nd均为常量,设为A,由此得到式(2)所示单位面积结电容表达式。对给定的LED,PN结接触电势差UD为某固定值,根据式(2)可知,LED正偏电压U增大,则结电容变大。也即LED附加正脉冲电压,结电容快速增大,载流子数量随之达到最大值。此时若LED端电压突然消失,式(2)的结电容理论上变为最小,但实际LED中的载流子无法快速释放,LED端电压也就无法快速降为零,导致LED实际无法真正熄灭,所以当驱动脉冲频率增大时,就会出现LED还未熄灭,下一周期的高脉冲已驱动LED再点亮,因此,要使得LED端电压快速降为零(即LED完全熄灭),需要及时清除结电容里的载流子。

2 现有载流子清除电路分析

作为可见光通信技术的提出者之一,Tanaka等为提高LED调制速率进行了大量的研究工作,在载流子清除驱动电路方面,提出在LED熄灭瞬间,使其接入一个短路(回路)来释放载流子[5],如图1所示。左半部分是传统的Q1驱动LED电路,右边绿色实线方框内是载流子清除电路部分。

图1 LED载流子清除电路Fig.1 LED circuit with drawing-out of carrier

Q3控制Q2,发送Q1的反相电压至Q2。当Vin驱动LED输入高电平时,Q1、Q3导通,LED亮,同时Q2关闭,即载流子回路断开。因此该电路不影响LED点亮操作。当Vin输入低电平,Q1、Q3关闭,LED熄灭,此时Q2导通,LED被短路,即提供一个释放载流子的通道。电路看似简单,却使得LED熄灭瞬间,接收端电压波形下降沿时间从56 ns下降为10 ns。然而,该电路在传统LED驱动电路基础上增加2个大功率分立高频器件MGF2407A(Q2和Q3),该器件价格昂贵,虽然能有效清除载流子,但也因此增加了电路的功耗。

3 改进系统电路设计

3.1 载流子清除电路改进

为尽可能减小功耗,设计去掉图1中的Q2和Q3元件。Q1既用于驱动LED,同时也作为其熄灭瞬间的短接回路,电路图如图2所示。当Vin输入低电平,Q1关闭,由VCC经R2电阻点亮LED。由于Q1关闭,此时并不影响LED点亮。当Vin输入高电平,Q1导通,LED被短路,LED瞬间熄灭,载流子快速流入GND,即达到快速清除载流子目的。

图2 改进电路设计图Fig.2 The improved circuit in this paper

考虑到MOS管的GS端悬空可能会导致自动导通,甚至损坏MOS管。因此接入R4以防止漏极电压通过寄生电容直接灌到栅极,导致MOS损坏。同时改进电路使用二极管D1和电阻C3并联,使得在Vin电压为高电平时,通过隔直电容C3,打开Q1。Vin拉低时,Q1关闭,电容C3被二极管D1短路,加快寄生电容放电,也缩短Q1的关闭时间,有利于高速开关管更快工作。

实验中的元器件需根据实际电路精准选取,对应元器件清单如表1所示。

表1 驱动电路所用元器件清单Tab.1 List of components used for driving circuit

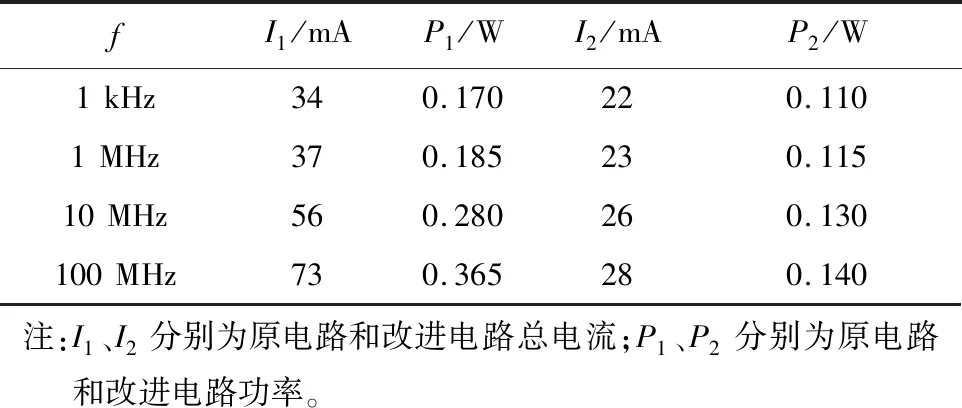

3.2 改进电路的功率分析

为研究改进电路的功率情况,使用Multisim测试LED驱动频率在1 kHz~100 MHz时,Tanaka设计的电路与改进电路在功率方面的差异。测试图2、图3电路得到的对应数据如表2所示。可见,随着LED驱动频率的增大,两个电路消耗功率均呈现上升趋势。当频率超过10 MHz 后,功率递增量明显加大,特别是在100 MHz 时,改进电路相比于Tanaka电路,功率只有后者的38.36%。

表2 电路功率对比数据Tab.2 Data of circuit power comparison

3.3 接收电路设计

为验证改进电路的通信效果,设计光电检测电路[11],采用光电二极管BPX65,其信号接收波形的上升沿/下降沿时间为12 ns;采用超低噪声、高精度运算放大器OPA37芯片,增益带宽达到63 MHz,以上两款芯片均满足本实验需求,具体电路设计如图3所示。

图3 BPX65接收电路原理图Fig.3 Diagram of BPX65 receiving circuit

该设计只进行光电检测前置放大电路设计,将BPX65工作于反接短路方式,降低其暗电流,可得到较好的信噪比。为杂散噪声,将R2并联C2。R1提供增益,C1为消振电容[12],与R1并联。

4 实验与分析

4.1 实验装置与实验过程

使用电子设计大赛实训平台的电源模块给收发两端的电路板提供+5 V、+12 V、-12 V、GND。发射端脉冲驱动序列从STM32开发板编程PC5引脚输出(也可使用函数信号发生器),信号输出采用BNC双头公线连接至发射端。示波器型号选用优利德UTD2102CM,带宽达100 MHz、采样率达1 G/s,实验设备可满足本实验需求。发射端电路与接收电路测试实验装置如图4所示。

图4 实验装置示意图Fig.4 Schematic diagram of experimental device

测试分两个阶段进行。第一阶段测试 1 MHz 频率下,改进电路的载流子清除效果;第二阶段进行接收信号测试。两个阶段实验均对传统LED电路(关闭载流子清除功能),与改进电路(打开载流子清除功能)的信号进行对比,分析相应性能的改善。

4.2 LED端电压测试

由于实验对电流(在PN结内的载流子数量)较为敏感,因此示波器测试端电压时,采用其两个通道的正极探头分别连接LED正、负极,负极探头接地的方式,在示波器上做两个通道信号的减法进行测试端电压。

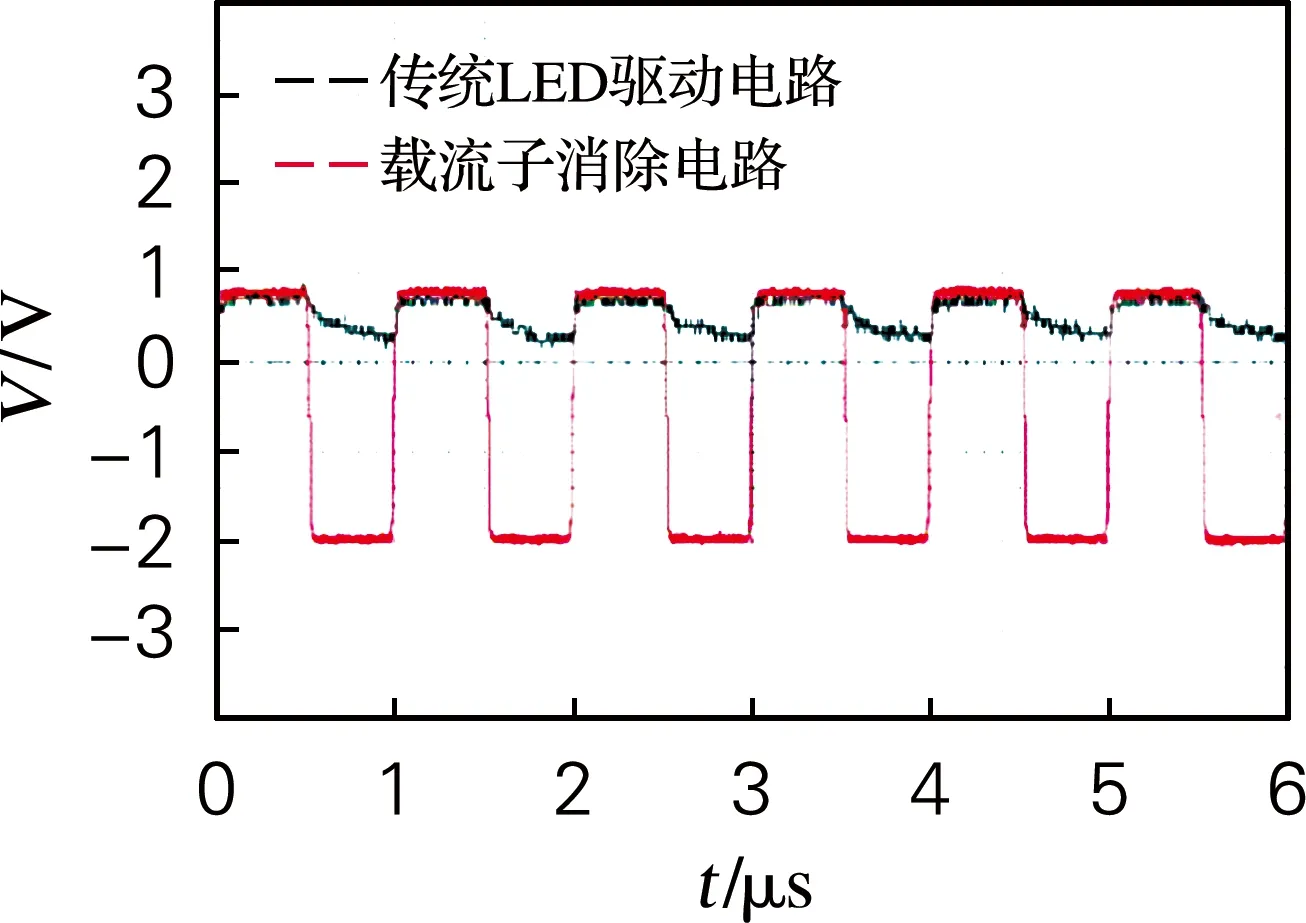

为更好地对比波形,实验同样测试了传统LED驱动电路的端电压波形,如图5所示。黑色曲线为传统LED驱动电路时的LED端电压波形,红色曲线为使用载流子清除电路时的波形。

图5 传统与改进电路的LED端电压对比Fig.5 Comparison of LED terminal voltage between traditional and improved circuits

可知,黑色曲线电压约0.7 V,即为结电容无法快速释放载流子在端电压上的反映;红色曲线波形则为较为规则的矩形脉冲波,端电压波形下降沿陡峭,说明载流子清除较为及时。同时也可以看出,传统LED驱动电路在1 MHz脉冲频率时,下降沿时间甚至超过200 ns,而使用载流子清除改进电路后,高电压下降时间极短。

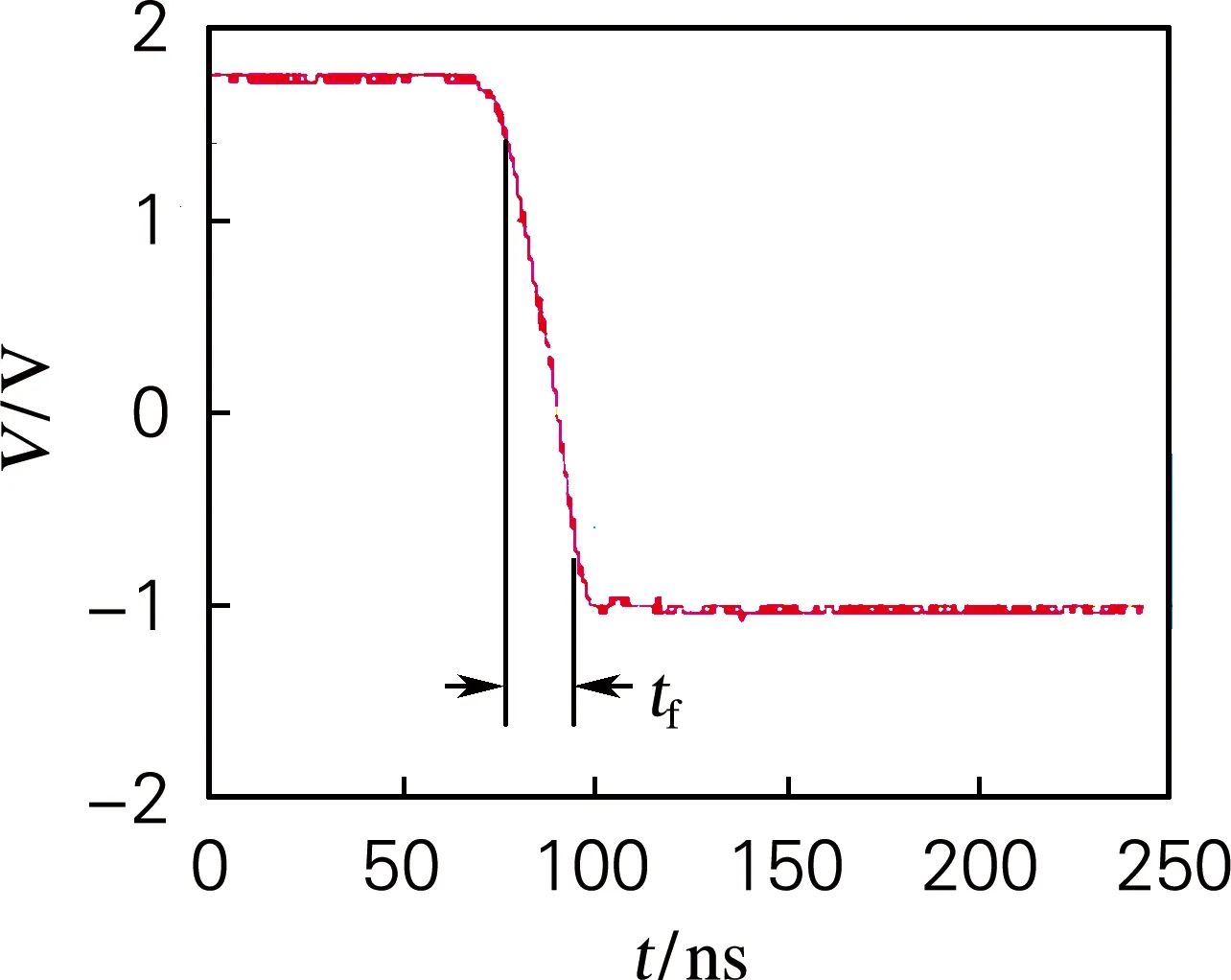

针对载流子清除电路中端电压的上升、下降时间,如图6、图7所示,改进电路的LED端电压下降沿时间tf仅约15 ns,比传统电路的下降沿时间200 ns有了很大改善;上升沿时间tr约20 ns,与传统电路的上升时间几乎相同。由此可知,改进电路的载流子清除效果良好。

图6 改进电路LED端电压下降沿时间Fig.6 The voltage drop time at LED terminal of the improved circuit

图7 改进电路LED端电压上升时间Fig.7 The voltage rise time at LED terminal of the improved circuit

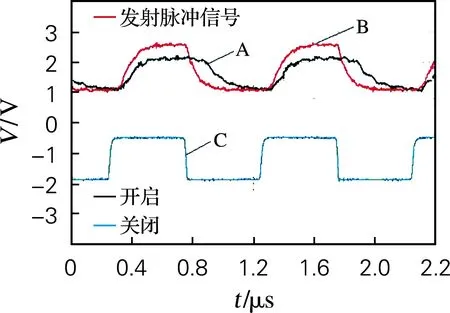

4.3 接收信号下降/上升时间

为分析接收信号性能,设置发射频率为1 MHz 脉冲,使用光电二极管BPX65接收,分别对传统LED发射电路和载流子清除电路进行测试,得到的接收端波形如图8所示。为分析方便,黑色曲线为传统LED电路发射的接收波形,记为A;红色曲线为使用载流子清除改进电路发射的接收波形,记为B;STM32开发板PC5引脚输出的脉冲波形,记为C;由图8可知,在接收端收到的B波形幅值明显高于A波形,甚至较之高出近50%幅度。同时可以看出,B波形上升至高电平的时间与A波形相近,但下降沿时间明显小于A波形。经过发射、接收电路后得到的A、B波形,比原始脉冲波形C滞后约15 ns,收发波形的滞后性也将是后续电路改进研究的方向之一。

图8 开启与关闭载流子清除电路的接收信号对比图Fig.8 Comparison of received signals between opening and closing sweep-out carrier circuits

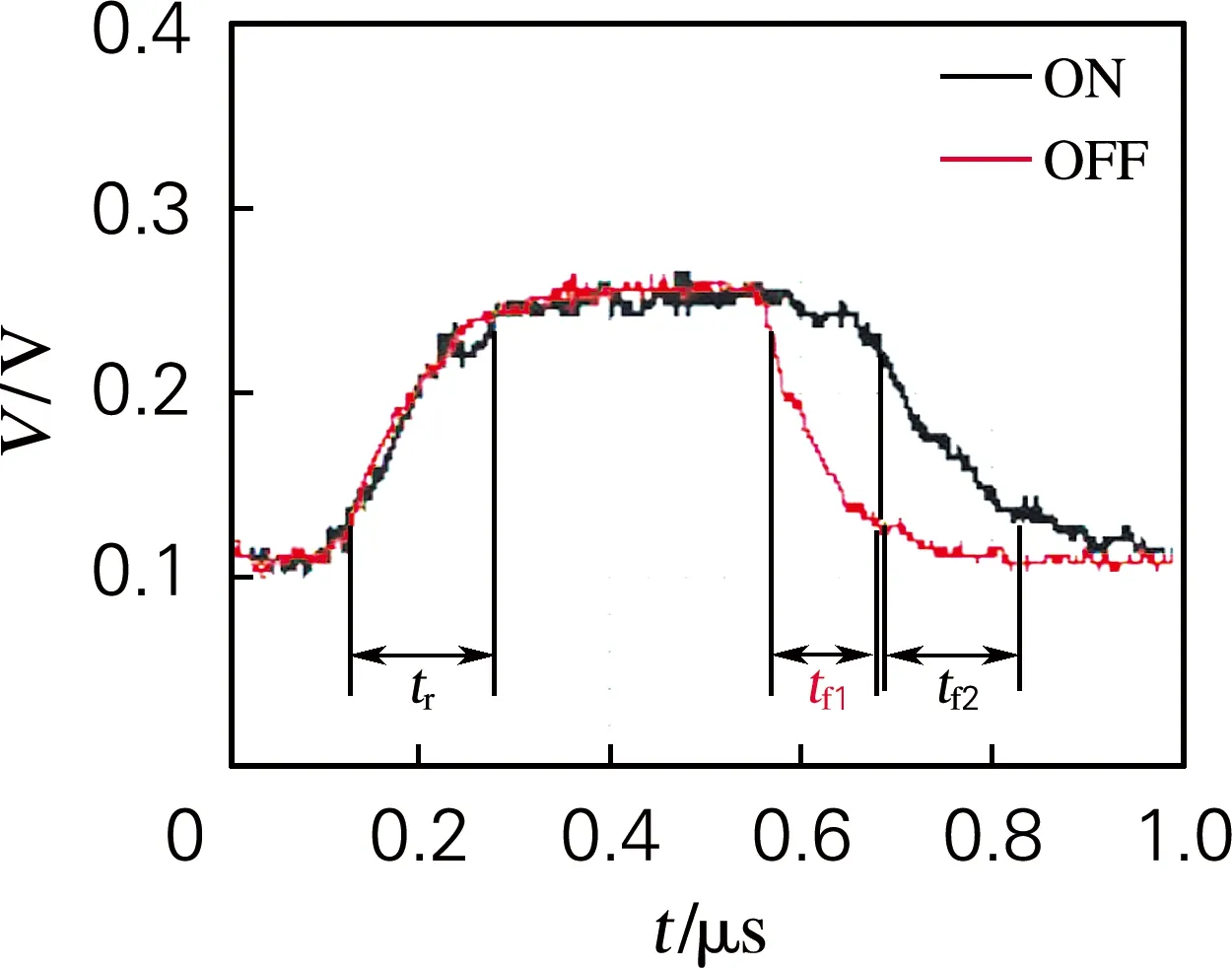

通过图9所示波形的上升沿/下降沿时间详细对比,发现传统LED驱动电路的接收波形(OFF)和改进电路的接收波形(ON),其上升沿时间几乎一致。但对电压下降时间tf1和tf2进行对比发现,采用清除载流子改进电路后,接收波形的下降沿时间缩短至约58 ns;不使用载流子清除电路则为85 ns,且该波形延时约40 ns才进入下降沿时间,即相当于用125 ns才降为低电平。

图9 接收波形上升沿/下降沿时间对比图Fig.9 Rise/drop time comparison of receiving waveform

5 结束语

通过分析现有的载流子清除电路,进行电路改进,将MOS管用于驱动LED的同时,也作为载流子释放回路,从而省掉了原电路中的2个MOS管,降低功耗,节省成本。使用该改进电路进行测试,得到的LED端电压下降时间从传统电路的200 ns,下降为约15 ns。接收端波形的下降沿时间也从85 ns下降为58 ns,系统性能得到提升。同时实验过程也出现信号接收延迟问题,将在后续进行深入研究。