基于FPGA的FTIR光谱仪采集系统的设计

贾明俊,陆安江,赵 麒,白忠臣,卢学敏,袁钱图

(1贵州大学大数据与信息工程学院,贵州贵阳 550025;2贵州民族大学机械电子工程学院,贵州贵阳 550025)

0 引言

因为不同物质对于红外光谱的吸收与反射情况不同,近红外光谱分析便成了分析物质的重要方法。FTIR光谱仪就是其中重要使用工具之一[1-3],此类光谱仪广泛用于化工、军事、农牧业、林业、环保、制药工艺等领域。由于传统的光谱仪体积庞大、延时高、便携性差等缺点[4-8],无法满足实时在线测试的需求。本文研究了一种实时在线的FTIR光谱仪[9-10],国内很多光谱仪都是CCD光谱采集系统,本文利用FPGA高速、高效、灵活性强的优势设计了一种硬件描述语言的采集系统[11-15]。通过使用AD7903将采集的光PD信号转换为数字量,利用DAC8568将存入ROM的预制电压数字量转换为模拟量从而驱动MEMS微镜,最终实现的快速FTIR光谱仪最高分辨率达到了0.06 cm-1,具有16位的采样精度与1 MSPS的转换速度。经验证,基本满足了现场在线测试需求。

1 原理分析

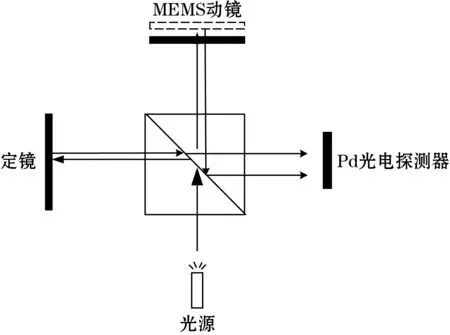

如图1所示,本次设计的干涉仪基于迈克尔逊干涉仪原理,采用分波阵面法产生干涉信号,图中虚线表示动镜移动时的位置,整个系统由动镜、定镜、窄带光源、分束器以及探测器构成。动镜与定镜相互垂直且到分束器初始距离相同,且分束器与动镜和定镜分别构成45°夹角。整个工作过程由光源发出入射光,入射光经过分束器,一半的入射光反射到定镜上再经过定镜全反射回分束器经透射到达光电探测器,于此同时,另一半的入射光经过透射到达MEMS动镜,由于动镜的移动而产生光程差,这样就会导致经过动镜全反射的光再经过分束器反射后汇聚在探测器时产生干涉,探测器将干涉信号采集下来。动镜的移动距离决定着干涉仪的性能。理想情况下,动镜的移动距离是匀速变化的,但是MEMS电热式微镜在不同电压情况下其弯曲度不是理想的线性,因此会导致附加谱线。因此本次设计的光谱仪通过增加同步采集参考光,经过CPU利用Bault方法最终提高采样精度。

图1 干涉仪框图

2 模块设计

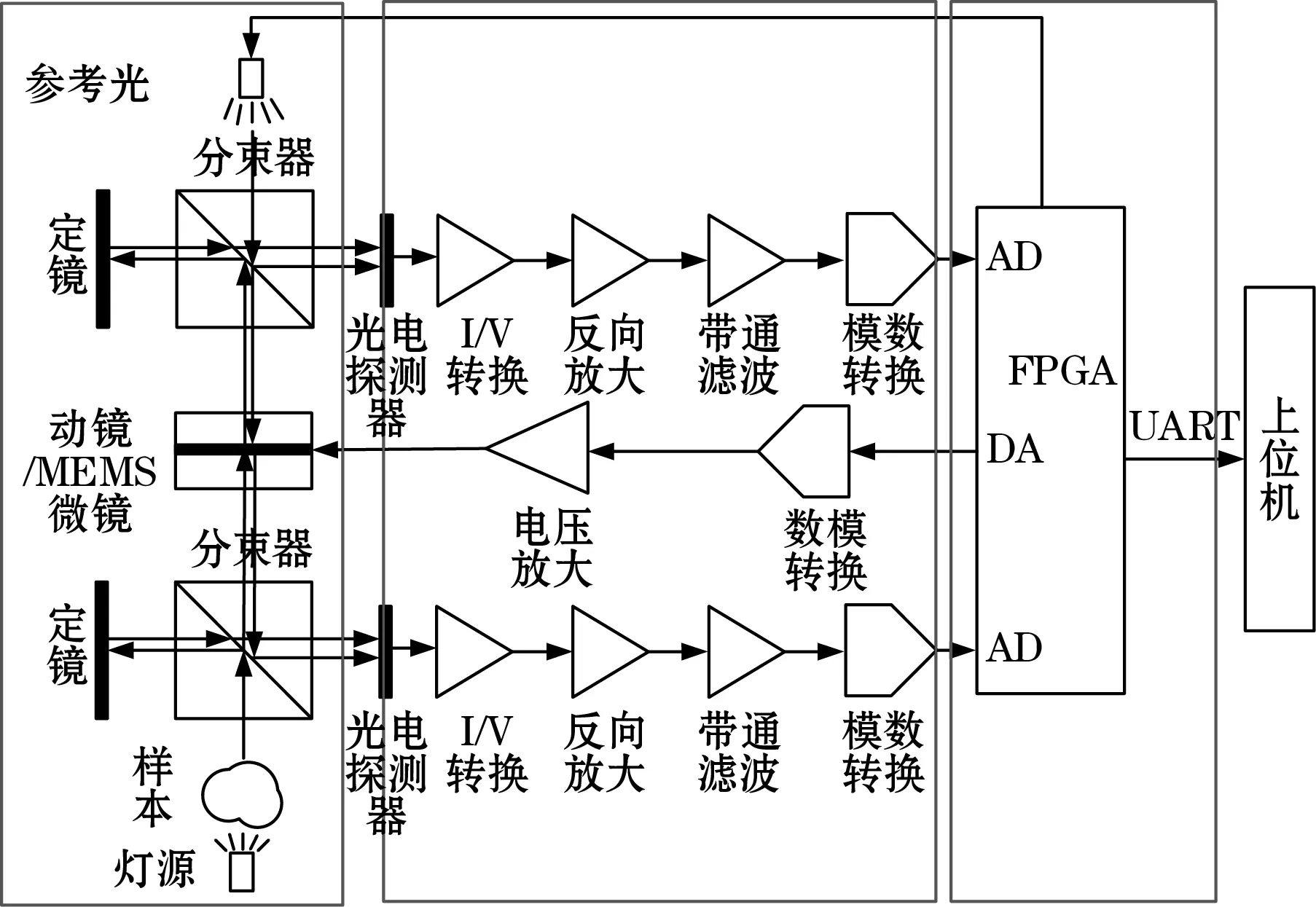

如图2所示,整个系统由2部分组成,分别是上位机跨平台的C++图形用户界面应用程序,该框架(QT Creator)通过编程形成,主要功能是对下位机输送操作指令、对于发回的光谱数字数据进行分析并绘制光谱图。下位机部分有3个细分模块,第一部分是光电生成部分,系统有2路光源,分别是参考光源和样本光源,它们通过迈克尔逊干涉原理的干涉仪产生等光程差的相干干涉;由此产生的不同光强同步转换为数字量。第二部分由硬件底层采集电路组成,主要完成I/V转换、放大、滤波得到稳定的数据信号。第三部分是FPGA控制处理部分,用于实现对ADC、DAC、RS232的时序控制,设计出符合器件技术手册要求的verilog时序代码,最后要将每个模块整合在一个top文件下,所有时序都按要求的方式运行。最终通过引脚绑定至EMIO引出。最后整个系统密切配合完成光谱绘制。

图2 光谱仪系统

3 模块设计

3.1 DAC

光谱仪分辨率可以表示一个仪器的分辨能力,对于波长为a1和a2的2个单色光,定义Δa=a1-a2为分辨率。在最大光程差l处,a1,a2分别有n和n+1个余弦波,定义动镜最远位移为l,则有:

2l=n/a1=(n+1)/a2

(1)

Δa=a1-a2

(2)

(3)

不难得出,动镜的移动距离决定着光谱仪的分辨率,设置多分辨率的光谱仪,就需要不同最大光程差移动距离,本系统的光程差有0.033、0.015、0.024 cm,所以驱动MEMS微镜就需要给出不同的电压。分别对应8、4、6 V,这是由MEMS微镜移动与电压关系决定的,而且由于驱动速度不同直接影响着光谱仪动镜加速度,所以驱动频率应在建议频率之下。为此设置了1-2-5 Hz的频率以验证最好效果。为了满足多通道、高精度、低延时的要求。选用了DAC8568器件,DAC8568具有8个通道、16位精度。满足了本采集系统驱动设计需求。设计MEMS四通道等距移动即可。DAC控制时序相对复杂。对于参考电压外接口,如果不使用就需要接电容后再接地滤波。DAC8568的使用需要一些指令的输入,首先是将器件复位,设计选用所有通道复位到0。接着把lDAC加载引脚设置为无效。因为使用同步加载模式不需要加载控制。接下来就是poweron步骤了,这里有2点须注意,一个就是选择Flexible Mode,因为Static Mode会不断关闭内部参考,还有一个就是使用稳定的内部参考,故此选择090A操作语句。在这种语句控制下,器件一直使用内部参考电压并且无需反复重启。最后一个语句是所有寄存器写0,输入所有指令后DAC8568与普通DAC工作方式相同,控制命令如图3定位流程。再通过技术手册得知主要问题在于同步脚SYNC何时拉高拉低和32个sclk给入。Clr直接拉高即可。

图3 指令图

3.2 ADC

ADC采集数据的频率需要根据所采信号的最大频率设定,根据奈奎斯特采样定理,采样频率应该为被采频率的2倍以上,而我们一般习惯使用过采样。所以需要计算被采信号的最高频率fmax。根据本次设计的光谱探测范围为900~2 600 nm,则相应的波数υ为:1/2 600~1/900 nm-1。根据最大移动距离L值为0.033 cm,完成一次扫描的时间(T)在最快驱动频率5 Hz情况下为0.2 s。设速度为v,根据式(4):

(4)

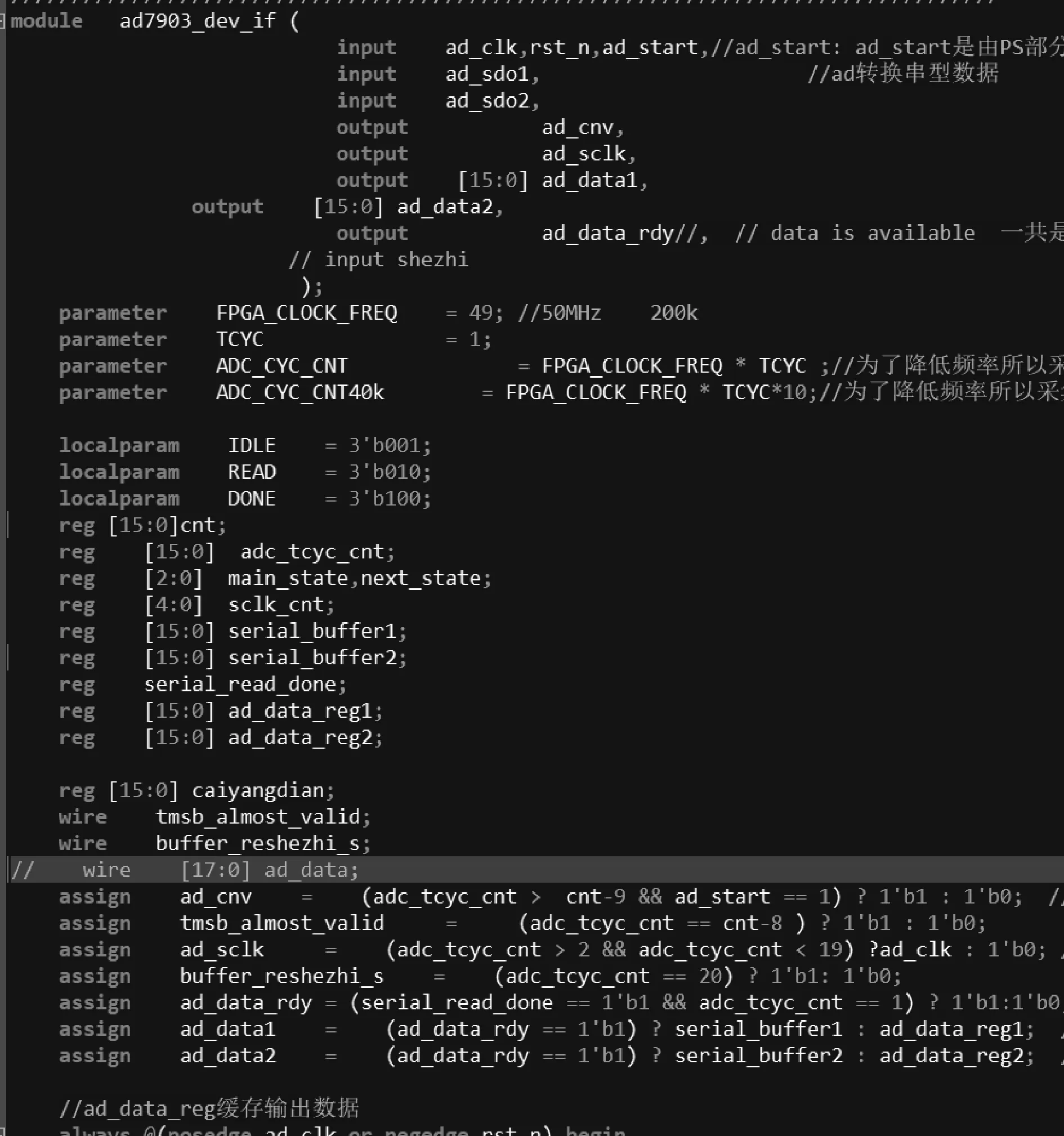

得到最大信号频率为3.6 kHz,据此综合考虑选择了DAC8568型号的ADC器件。该器件具有16位的高精度双通道模拟输入、吞吐速率为1 MSPS、支持轨到轨的转换。查看技术手册,选用了符合要求的四线同步采样模式(CS模式),根据设计要求,主机通过一个片选CONVERT和同一个时钟SCLK同时控制2个从机工作实现同步采集。通常所有的ADC时序设计都是围绕技术手册进行的,第一步看sclk,查看得知sclk最小周期为11.5~16 ns,但是一般选用典型时钟速率,故而选用50 MHz时钟作为串行时钟。接着看CNV,设计主要关注何时拉低拉高,同时要明确这是一个先转换后采集的过程,另外要关注保持建立时间。最后,AD7903也和大部分器件一样,下降沿数据逐渐输入,所以上升沿串行取出。最终利用vivado编写的主体代码如图4所示。

图4 代码图

3.3 UART及数据缓存

设计选用了CP2101串口并设置460800的最大波特率传输机制。数据采集和数据控制字宽度不一样,所以对于UART做了不同的处理,对于下位机接收UART采用普通的UART机制,10 bit数据,包括1个起始、1个结束和8 bit数据。UART_rx时刻保持等待状态,等着上位机指令。只要上位机有指令发出,则立刻分析。对于采集的数据,下位机UART_tx采用了16位发送方式并且例化了2个发送tx,这样做有助于提高传输速率,ADC的数据是16位的,所以设计16位发送更有利于理解。这样做也发挥了FPGA灵活多变的特点。在数据缓冲时,利用了比较常用的FIFO,FIFO深度很大,达到10 000 bit,之所以这样做是因为串口相对于采集的吞吐率过大,所以1 s内数据也需要大的缓存空间,在FIFO设计中最重要的是关注读写使能的设置,FIFO的写使能选用A/D采集的dataready,保障了写入数据的可靠,读使能选用tx_busy,保证了发送的有序。FIFO的空empty也作为tx的数据有效标识,保证了tx不传输空数据和无效数据。

4 系统仿真

对于整个系统的设计,遵循着自顶向下的设计方式,即首先给出设计方案整体架构,然后依据需求将系统各部分模块化,每个接口放在顶层,每个模块单独设计好,设计出满足需要的模块小单元。正是基于这样的原因,必须在仿真时先对模块测试是否符合需求,然后再对整体仿真,对每个用例都要测试。保证系统的可靠性。

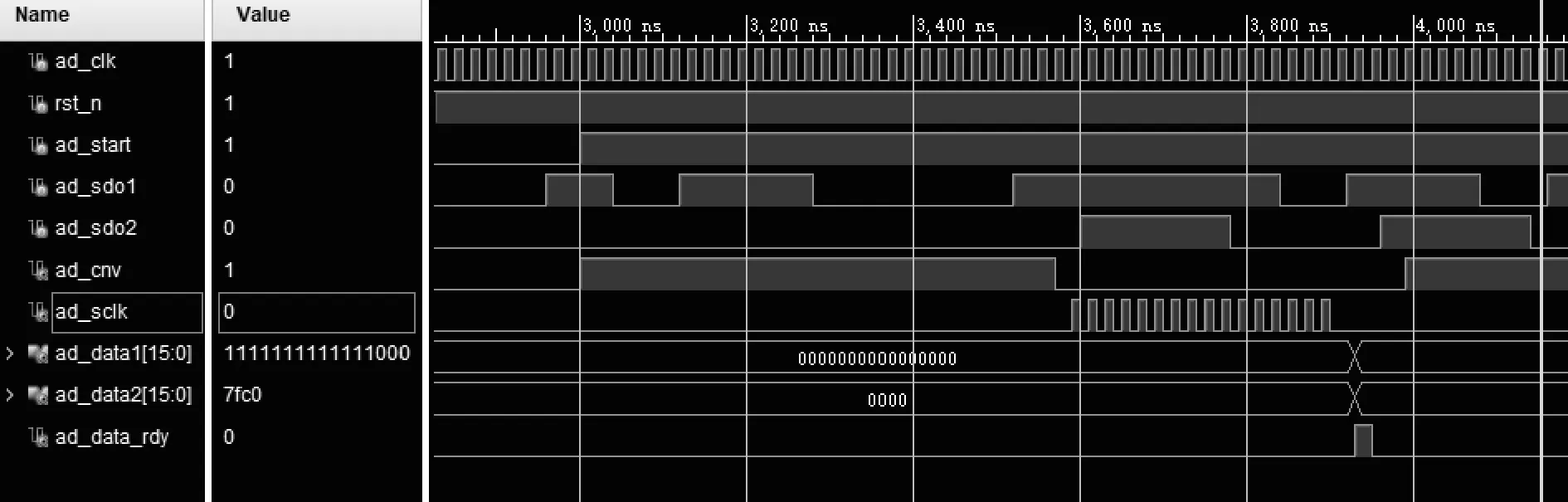

4.1 ADC仿真

对于ADC测试代码,需要给出的激励有时钟ad_sclk和输入的数字数据ad_sdo1(2)以及启动信号ad_start。经过查看仿真图5可以看出,在时钟与信号有效时,A/D数据转换并没有立即开始,直到ad_start启动后,数据采集才开始,片选ad_cnv拉高、采集过程循环进行,ad_data也输出了寄存的数值,得出结论满足时序要求。

图5 ADC仿真时序

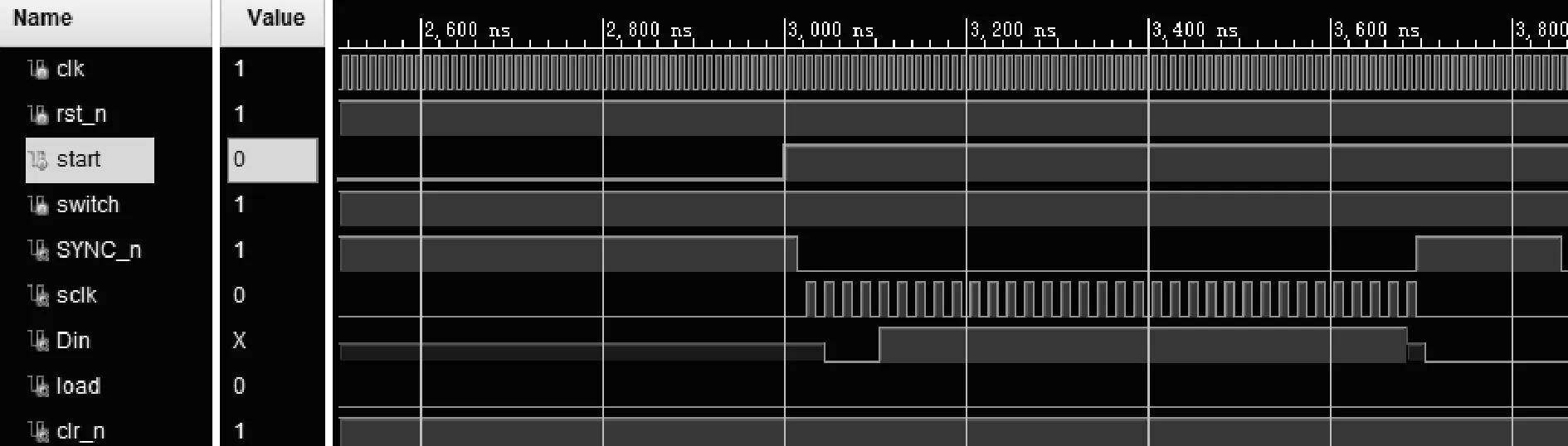

4.2 DAC仿真

DAC时序首先必须有时钟clk、复位rst以及启动da_start指令。查看仿真图6可以看到,在rst无效、clk有效时,DAC并没有立即输出信码Din,这是因为da_start没有启动,时序仿真在启动start有效后立即进入工作状态。在启动信号有效时,持续进行信码输出。

图6 DAC仿真时序

4.3 系统仿真

对于UART串口没有单独测试。把它作为系统代码测试的一部分进行了综合仿真。在系统仿真图7中,仿真了上位机发送代码senddata为8h10指令,即ADC、DAC同时工作,可以从图7看到rxd拉低发生了接收,最后可以看到寄存器rx_data成功接收了8h10。可见指令正确接收。紧接着系统在得到rx_data的信息码后,ADC和DAC的start都拉高启动。ADC和DAC随后都进入工作模式。在数据有效后采集数据通过2个UART发送到发送线txd1和txd2。最终得出时序仿真符合要求。

图7 采集系统仿真时序

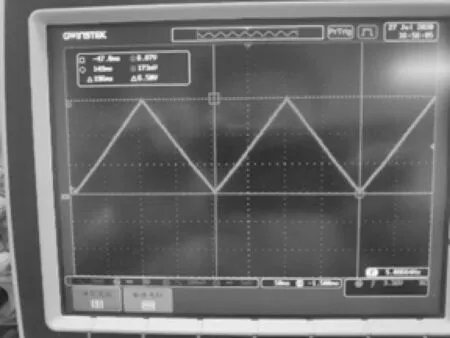

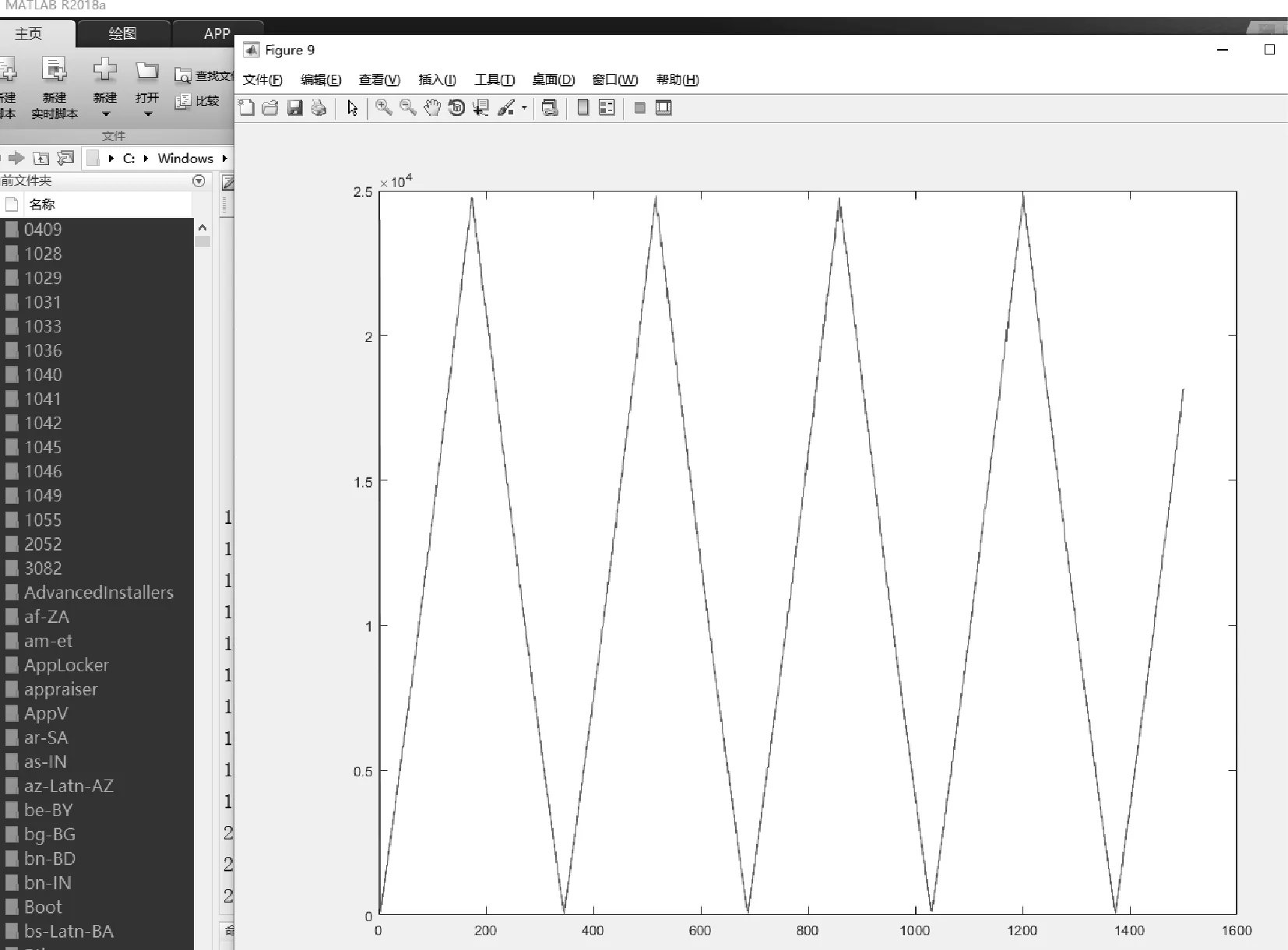

5 实际测试

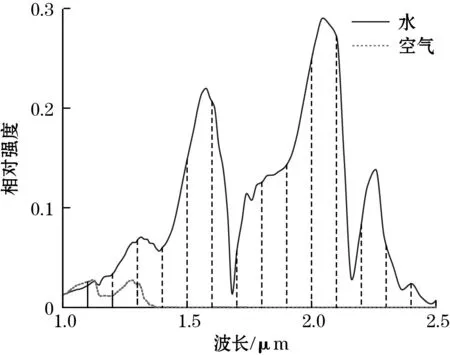

本次设计主要测试有DAC驱动测试、ADC采集测试。主要用到仪器有GDS-2204A(200 MHz)、小型MEMS干涉仪、1 310 nm的近红外作为参考光源、CPU主机。整体布局图如图8所示,示波器主要为了观察ADC采集输入信号与DAC的输出信号,首先测试FPGA输出电压数据与频率是否符合要求,图9是1 Hz与6.6 V的测试结果,可以看出三角波十分标准。验证了驱动没有问题,下一步就可以进行采集设置了,首先利用信号发生器产生一个三角波,然后利用MATLAB将串口发回数据绘制出来,结果如图10所示,虽然有少许毛刺,但是经计算是输入的20 kHz三角波,最后在ADC和DAC都符合要求时,进行系统连接,最终采集的光谱信号如图11所示,可以看出水和空气的光谱具有明显的特征差别。最终得出,光谱仪采集部分结果基本符合设计要求,后期进一步的光谱数据处理交由CPU部分处理。

图8 布局图

图9 驱动电压

图10 采集三角波

图11 水和空气采集的相对强度图

6 结论与不足

设计的基于FPGA的光谱采集系统,经仿真论证设计满足要求,并且改变了多数利用ARM设计驱动底层器件的现状,为广大科研人员提供了一个更为可靠的路线。与此同时,采用FPGA设计整个下位机系统,不仅缩短了开发周期,而且节约了成本。利用FPGA开发的系统不仅更加高速高效灵活,而且便携升级换代也可以发挥技术沉淀的优势。但是整套系统还可以进一步提高,集成度也可进一步优化。在下一步设计中,从ARM与FPGA结合的角度出发,开发更加小型化的设备。