多通道低相噪同步频率源设计

胥 伟,潘明海,张艳睛

(南京航空航天大学 电子信息工程学院,江苏 南京211106)

0 引言

DRFM 系统在产生雷达欺骗干扰回波时,需要一个高稳定度的频率源信号用于对外部输入信号的采集与重构。 作为DRFM 系统关键技术之一,频率源一旦出现偏差,整个系统将无法正常工作。 当前,最主要的频率源产生技术包括直接数字合成[1-2]以及锁相环频率合成[3-4],直接数字合成技术一般结构相对复杂,且很容易输出较高的杂散[5],而锁相环技术相对已比较成熟,且在设计时会考虑加入环路滤波器,因此能有效地过滤相位噪声。此外,锁相环技术频率源电路的结构较为简单,且能输出低相噪、高稳定度的频率信号[6]。 本文将采用锁相环频率合成技术进行设计。

1 锁相环的基本原理

图1 锁相环工作原理框图

负反馈系统的锁相环通常由鉴相器、电荷泵、环路滤波器、压控振荡器(VCO)、分频器等组成[7],如图1 所示。 鉴相器对经过R 分频的参考频率信号与经过N 分频的锁相环输出信号进行比较并产生两者的相位误差信号;电荷泵将相位误差信号转变为与此成比例的电流信号;低通环路滤波器对电荷泵输出电流积分以产生对应的电压信号;VCO 根据输入电压信号输出对应的频率[8-9]。

2 锁相环相位噪声理论分析

2.1 相位噪声的定义

锁相环稳定工作时,其自身的非线性效应能有效抑制输出信号振幅波动,但是其相位波动无法抑制。 因为相位波动的存在,锁相环输出信号在时域上的过零点间隔不再均匀,造成频率信号的“抖动”。 “抖动”的存在会使部分功率产生频偏,中心频谱周边产生的边带,即为相位噪声[10]。

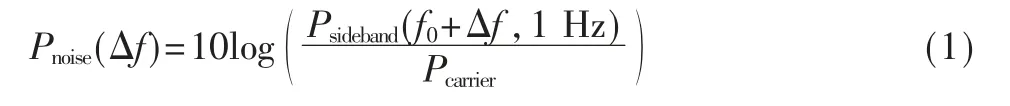

相位噪声定义为一个频偏上的噪声功率与输出信号载波功率的比值,一般将其归一化到1 Hz 带宽,如图2所示,单位为dBc/Hz。 则相位噪声计算公式为[11]:

图2 相位波动谱密度

2.2 频率源相位噪声对采样性能影响

频率源信号的性能会严重影响ADC 器件,对高速信号的采集,会造成采样值严重偏离理想采样值,破坏采样的时序。

当频率源相位噪声较高时,频率源会存在随机性“抖动”,假设时钟抖动量为ΔT,此时的频率源信号为:

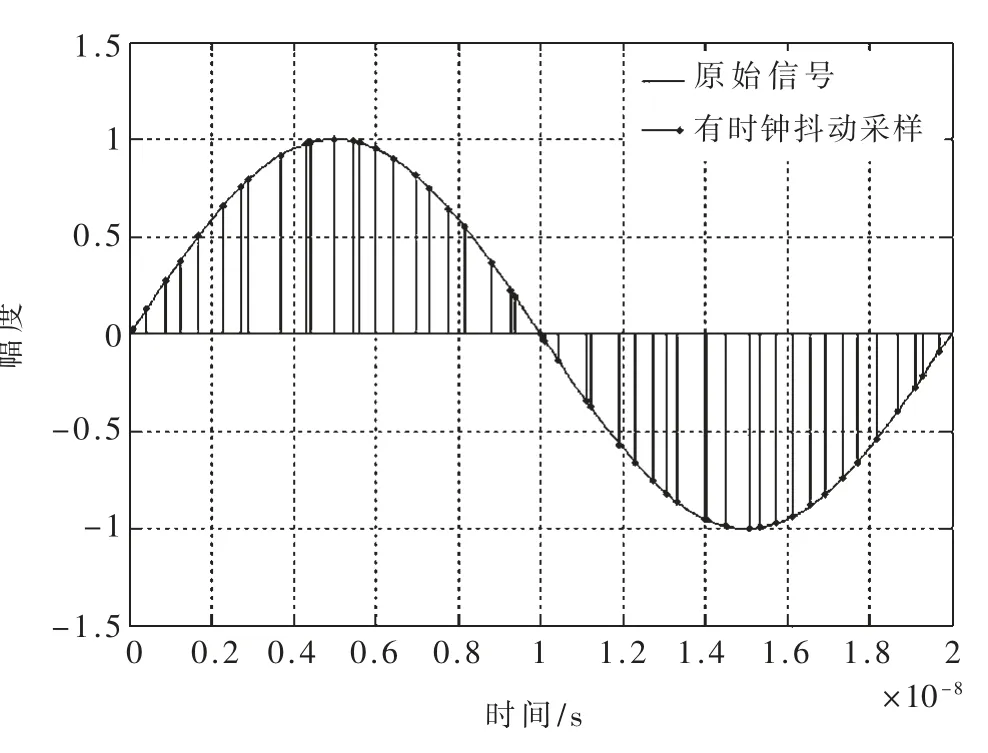

采样时刻会发生一定的随机偏移,偏移量为ΔT,此时的采样位置不再确定,ADC 器件对输入信号进行非均匀采样,采样输出如图3 所示。

图3 有相位噪声时钟采样

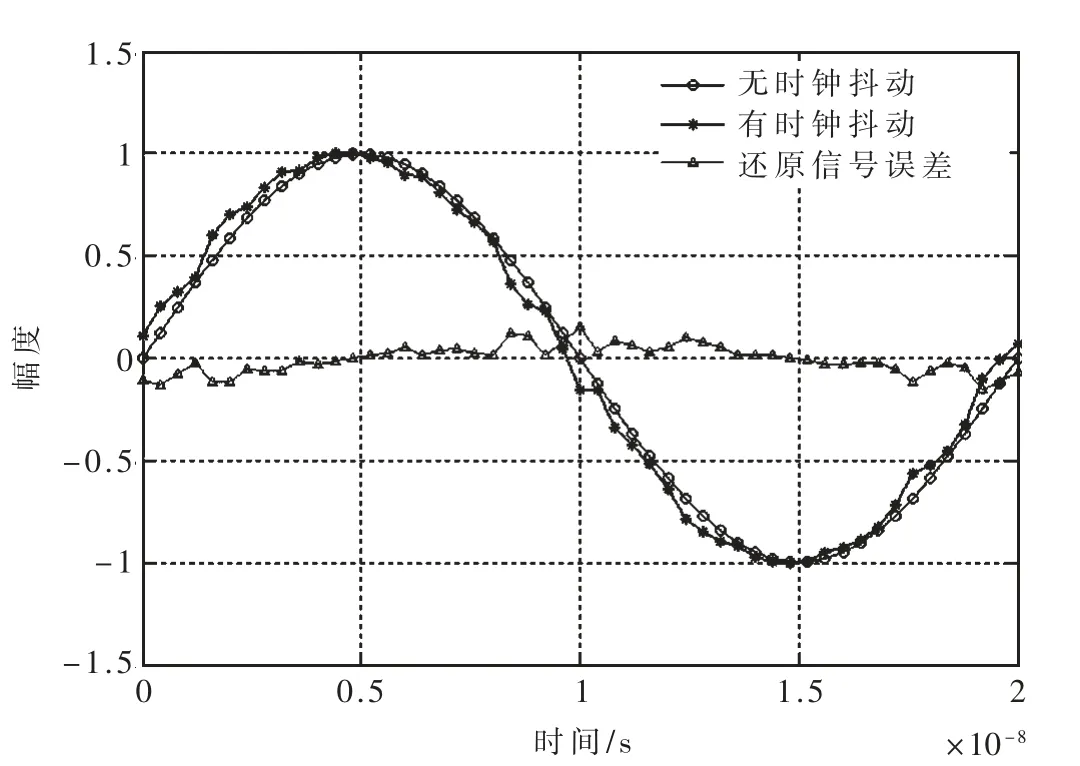

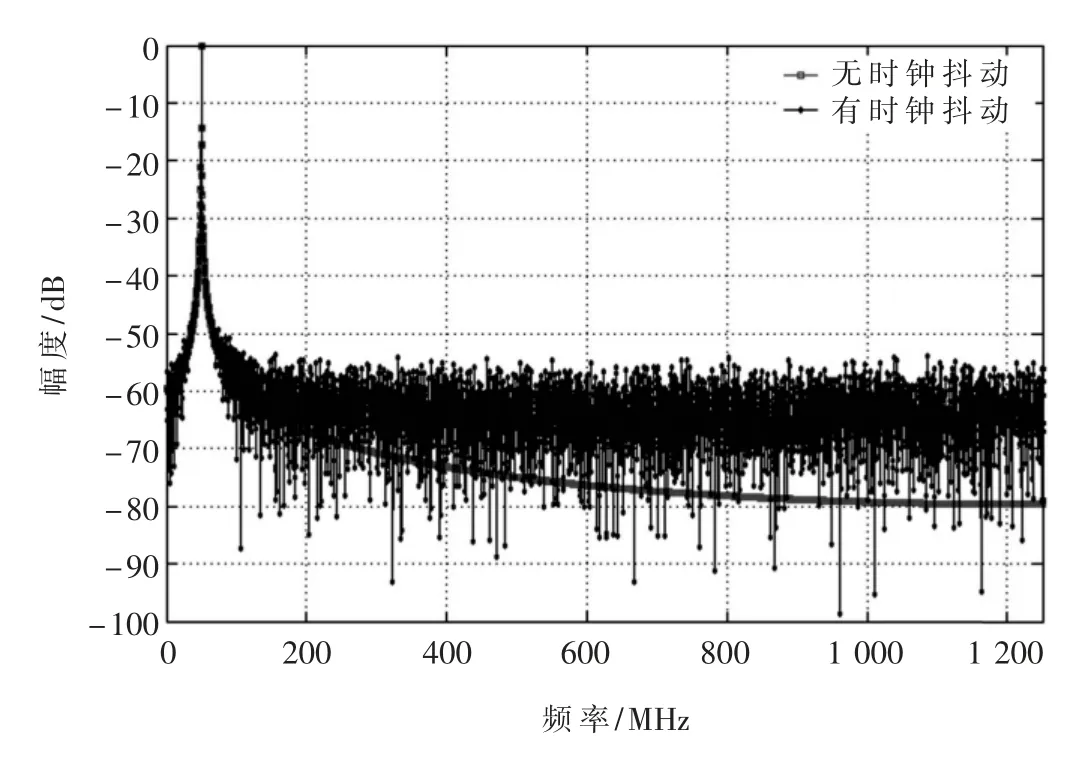

数据采集完成以后,若以无“抖动”的频率源重构采样信号时,结果如图4、图5 所示。

从时域图4 中可以得出,信号重构时出现了明显的畸变。从频域图5 中可以得出,信号杂散性能显著恶化。如果采用更高的采样速度,那么由抖动时钟引入的噪声将更加明显。 因此在ADC 采样系统孔径抖动确定时,一个高稳定度的频率源是系统稳定性的重要保证。

图4 均匀频率时域重构

图5 均匀频率频域重构

2.3 锁相环相位噪声理论

锁相环系统是一个非线性的系统,但是当锁相环的鉴相比较频率为环路带宽的10~20 倍时,可将其近似认为是一个线性系统[12]。 线性系统条件下通过传输函数分析各个模块对整个环路相位噪声产生的影响。假设锁相环路中各个模块产生的是互不相关的加性噪声,锁相环噪声线性模型如图6 所示。

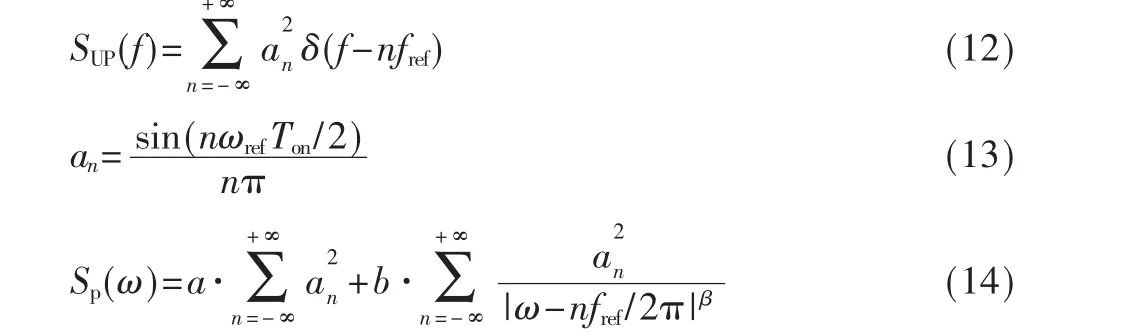

该锁相环路的开环增益为:

式中,Kd为鉴相器增益,KVCO为压控振荡器灵敏度,F(s)为环路滤波器的传输函数,N 为分频比。

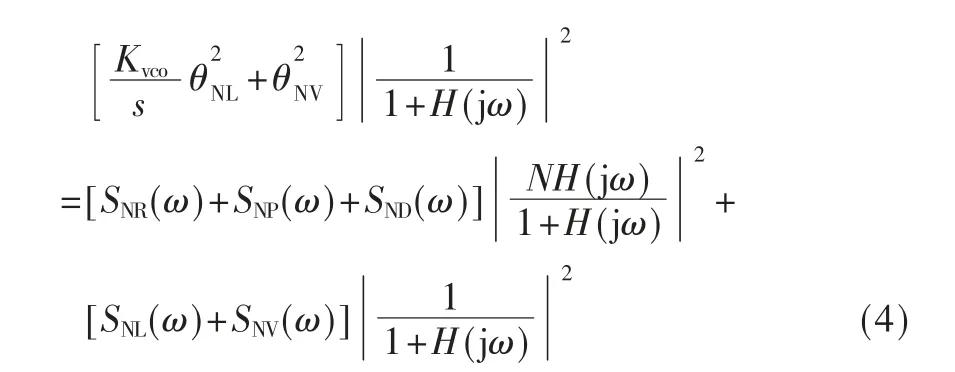

锁相环路总的相位噪声为参考频率源相位噪声、鉴相器相位噪声、环路滤波器相位噪声、压控振荡器相位噪声和分频器相位噪声的总和,即为:

图6 锁相环噪声模型

由于锁相环路中采用的是低通滤波设计,故开环传递函数H(s)和闭环传递函数NH(s)/(1+H(s))都具有低通特性,而1/(1+H(s))具有高通特性。 所以除了VCO 噪声源具有高通特性外,其余噪声源都具有低通特性。 对于低通特性的噪声,环路带宽越小,噪声抑制能力越强;而高通特性的噪声,环路带宽越大,噪声抑制能力越强。因此,为了均衡的抑制噪声,环路带宽选择确定在两种噪声谱密度线的交叉点。

2.4 各模块相位噪声模型分析

2.4.1 参考频率源相位噪声分析

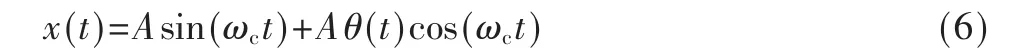

假设一个具有相位噪声的正弦波时钟信号为:

因而周期抖动可表示为Jd=θ(t)/2πfc。

因为周期抖动噪声Jd<<π/2,故式(5)可简化为:

因此式(6)的频谱可表示为:

其 中,δθ(f)是θ(t)的 频 域 表 示。

因此可以得到时钟信号的相位噪声功率谱密度函数为:

从式(8)看出,减小参考频率抖动,可减小输出信号相位噪声。

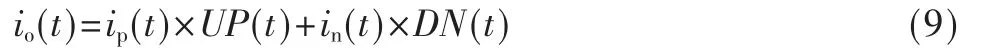

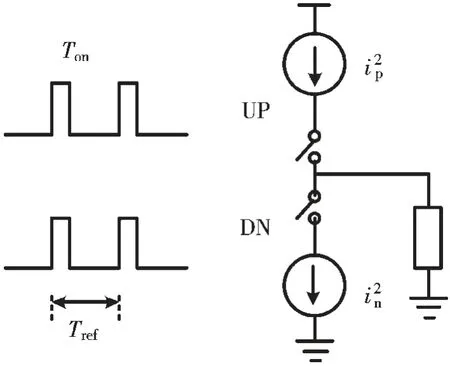

2.4.2 鉴相器等效输出相位噪声

鉴相器等效噪声模型如图7 所示。

由于式(9)中两项原理相同,故取其中一项进行分析,并对其取傅里叶变换可得:

图7 鉴相器等效噪声模型

从上式得出,提高鉴相频率fref可减小相位噪声。

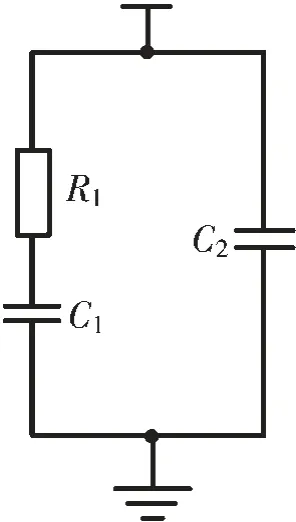

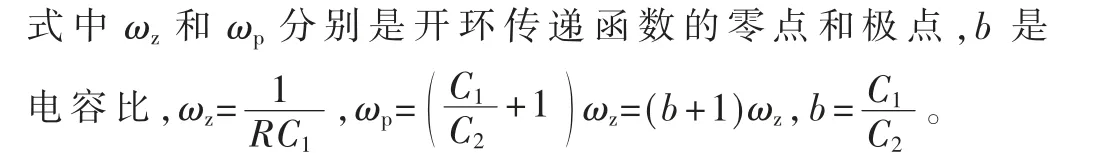

2.4.3 环路滤波器相位噪声分析

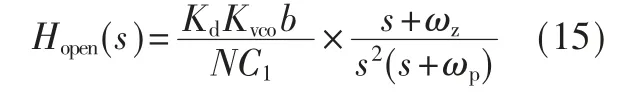

二阶无源环路滤波器模型如图8 所示,电容C2将电荷泵输出电流转换成直流电压,并通过滤除电压纹路,改善振荡器输出信号的寄生调制,同时R1、C1支路能有效提高环路稳定性。

环路滤波器的开环传递函数为:

图8 二阶无源环路滤波器模型

无源二阶环路滤波器的相位噪声功率谱密度为:

式中K 为玻尔兹曼常数,T 为温度值,B 为带宽,R 为电阻值。 从式(16)得出,降低电阻R,能够降低环路滤波器的相位噪声。

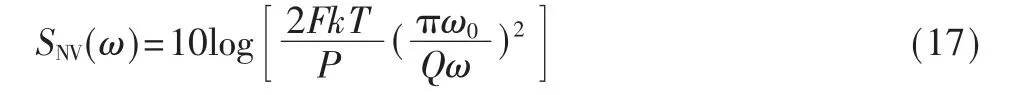

2.4.4 VCO 相位噪声分析

VCO 的相位噪声模型如图9 所示,该模型主要分成三个区:与偏移频率三次方成反比的1/f3区;与偏移频率平方成反比的1/f2区;与偏移频率无关的噪底区。 接近载波功率的1/f3区的相位噪声在工作时会被抑制,而VCO 的输出噪声主要来自1/f2区。

图9 VCO 相位噪声曲线

1/f2区相位噪声功率谱密度为[13]:

式中,F 是一个实验参数, 表示的是晶体管对相噪的影响。 k 为玻尔兹曼常数,T 为绝对温度,P 为载波功率,Q为谐振腔Q 值。

从式(17)看出,提高VCO 的载波功率,即提高VCO的输出幅值,同时降低Kvco,能够降低VCO 在1/f2区的相位噪声。

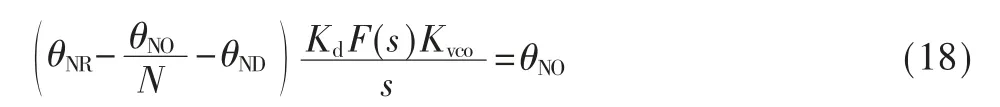

2.4.5 分频器相位噪声分析

N 分频器可在其他条件不变的情况下改变VCO 的输出频率,并且可改变鉴相频率,提高输出频率分辨率。

由于N 分频存在,输出端会引入噪声θNO/N,则:

整理可得:

其中:

故分频器相位噪声谱密度为:

显然, 输出噪声因为N 分频器而起到倍频的效果。在低频偏时,G(jω)≈1,且SθNR远大于SθND,输出噪声会增加近20logN。 因此N 分频器的值不宜不太,如果N 太大,可以提高输入参考频率或者多级锁相环来降低N分频带来的影响。

2.5 相位噪声改善措施

频率源最重要的性能指标之一就是相位噪声,综合上述分析,降低各模块相位噪声措施如下:

(1)输入参考时钟:采用高性能的恒温晶振作为参考频率源输入,并且可采用两级锁相环的设计,第一级锁相环在外部恒温晶振驱动下,为第二级锁相环提供高稳、低相噪的参考时钟;

(2)鉴相器:提高鉴相频率可以减小输出信号相位噪声;

(3)环路滤波器:降低电阻R,可减小相位噪声;

(4)VCO:提高VCO 的输出幅值,降低Kvco能够改善其相位噪声性能;

(5)分频器:采用更高的频率信号作为参考时钟,或者采用多级锁相环结构,减小分频系数N,以改善分频器的相位噪声性能。

3 频率源器件选型与方案设计

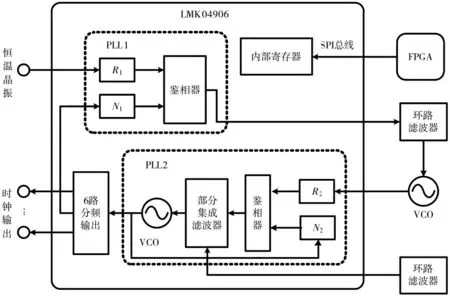

本频率源设计最核心的器件是锁相环芯片,该器件选用TI 公司的时钟管理芯片LMK04906,它具有双锁相环结构,可工作于双锁相环和单锁相环两种模式,能实现6 路差分或者12 路单端在2.26~2 600 MHz 范围内的任意同步频率输出,相位检测器速率可达155 MHz,相位噪声底低至-227 dBc/Hz,能够保证高稳频率信号的输出。

控制器采用一片Xilinx Spartan-6 FPGA 芯片通过SPI 总线完成LMK04906 芯片内部寄存器的配置。

参考输入是外部给PLL 的参考时钟信号,该信号会直接影响输出信号的性能,故采用高稳定度的恒温晶振作为参考输入。

本设计采用两级锁相环结构,如图10 所示,增加第一级锁相环的目的是为第二级锁相环提供高稳定度、低相噪的参考频率。第一级锁相环的环路滤波器为保证恒温晶振输入的性能而采用窄带设计,第二级锁相环的环路滤波器为保证VCO 输出相噪性能而采用宽带设计。在此结构下,频率源可输出多路与参考输入同相位的信号。

4 实验测试结果

多通道同步频率源设计采用6 阶PCB 层叠设计,实物加工板卡如图11 所示。

通过罗德与施瓦茨的频谱仪FSL6 对设计的频率源电路输出信号进行杂散和相位噪声测试分析,实测采用高稳定度、低相噪的10 MHz 恒温晶振作为第一级锁相环的参考频率输入。

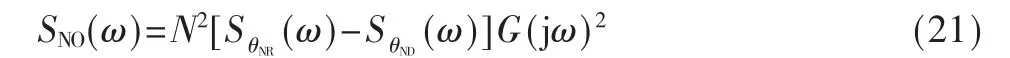

PLL2 环路带宽内基底相位噪声由式(22)估算可得[14]:

式中,N@1Hz表示PLL2 的归一化相位噪声底,LMK04906器件N@1Hz的值为-227 dBc/Hz;N 表示分频系数;fpdf表示鉴相频率。

根据相位噪声改善措施进行优化设计,设置N 分频为250,fpdf为10 MHz,则频率源基底相位噪声理论值为[15]:

图10 频率源设计方案

图11 频率源硬件实物图

从实际测试结果图12 看出,当频率源电路输出中心频率为1.25 GHz 信号时,频率信号杂散抑制优于-60 dBc/Hz,在500 kHz 频偏处的相位噪声为:

图12 频率源1.25 GHz 输出频谱

相位噪声的实测值与基底相位噪声理论值接近,偏差部分可能来自频率源电路中外部噪声输入引起的恶化。

5 结论

本文针对数字射频存储系统中,对ADC 采样频率源的实际需求,设计出基于两级锁相环技术的频率源电路,能够实现2.26~2 600 MHz 范围内任意频率信号的输出,且根据实验测试结果表明,该频率源输出信号在稳定度、低相噪方面具有非常优异的性能,完全满足本系统的设计指标,具有切实的应用价值。 同时,该频率源电路成本低、控制灵活,为雷达电子对抗等诸多领域提供了一个高性能的频率源解决方案。