小数锁相环杂散分析及优化方法

高晓强,曹振坤,张加程

(中国电子科技集团公司第十三研究所,河北 石家庄 050051)

0 引言

随着通信、雷达等领域的不断发展,对锁相环的要求越来越高,与整数锁相环相比,小数锁相环可以在采用较大鉴相频率(保证相位噪声)的情况下实现频率细步进,因此小数锁相环是锁相领域不可缺少的一部分,但是小数锁相环会引入小数杂散,如果杂散幅度过高就会影响整个频率源系统的指标,因此探究小数锁相环小数杂散的位置以及改善小数杂散的方法是非常必要的[1]。

1 小数分频实现方式

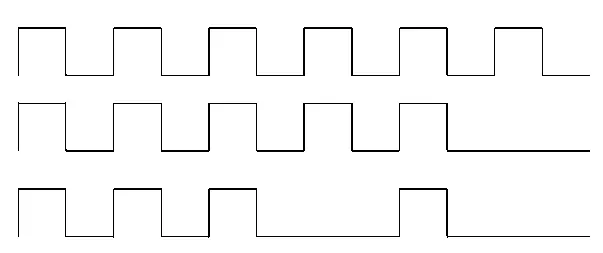

在一定时间T总内,输出的脉冲个数为M个,那么每个脉冲的平均周期为:T总/M,如图1所示。假设总时间为T总,那么第一个脉冲的平均周期为T总/6;第二个脉冲的平均周期为T总/5;第三个脉冲的平均周期为T总/4,如图1所示。

图1 相同时间不同脉冲个数

假设分频器的输入频率为f2,输出频率为f1,那么该分频器的分频比为f2/f1,如果f2/f1为整数,那么此分频为整数分频;如果f2/f1为小数,那么此分频为小数分频。

假设分频比f2/f1的整数部分为N,真分数部分为b/a。则要想实现该分频比最简单的方式为:首先有b个(N+1)分频,然后接(a-b)个N分频,则在这个大周期内总共产生的脉冲个数为a个,所用时间为:(b*(N+1)+(ab)*N)*Tclk=(a*N+b)* Tclk,平均每个脉冲的周期、频率以及实现的分频比如下所示:

从上式中可以看出,在一个大周期内该分频器实现了所需的小数分频[2]。

具体小数模式的原理框图如图2所示,在原来的整数分频器模块上增加ΔΣ调制。假设a计数器的值为a,b计数器的值为b(a>b),那么分频器实现分频比为:N+b/a。假设a计数器的位数为K位,那么分频器能够实现的最小的小数[3]为:1/2K。

图2 小数模式原理框图

2 小数锁相环各阶杂散点位置

2.1 小数分频调制模式引入的杂散

小数分频实现的过程,如果是周期性的N分频和N+1分频,那么这个周期性的信号必然产生一杂散信号调制在输出频率上。该杂散信号与ΔΣ调制的调制方式直接相关,消除该杂散信号的方式为利用算法将小数分频的实现过程随机化。

2.2 系统非线性引入的杂散

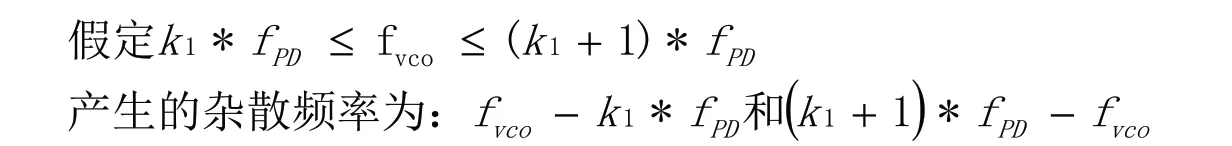

小数模式虽然在宏观上看实现了小数分频。但是从单个周期看,其实锁相环一直处于失锁重新锁定的过程,所以小数模式下输出频率的相位一直在变化,且锁相环处于动态锁定过程中,电荷泵上下偏电流一直处于工作状态。但是从频谱上看,锁相环处于“锁定状态”,因此我们假定锁相环处于稳定中。分频器的分频比实际为整数,因此在整个系统中同时存在鉴相信号以及它的高次谐波K*fpd(其中K为整数,fpd为鉴相频率),和进入N/(N+1)分频器信号的频率fvco及其高次谐波分量。

由于系统的非线性,VCO的主频及各次谐波就会和鉴相信号的各阶高次谐波相互交调产生各阶杂散。

一阶小数杂散:fvco与鉴相信号高次谐波交调产生。

二阶小数杂散:2*fvco与鉴相信号高次谐波交调产生

三阶小数杂散:3*fvco与鉴相信号高次谐波交调产生。

n阶小数杂散:VCO的n次谐波n*fvco与鉴相信号高次谐波交调产生。

3 小数杂散优化方法

3.1 已知输出频率和环路带宽

在已知输出频率和环路带宽情况下,可以通过改变鉴相频率的方式改变杂散点的位置(具体计算方式已给出),使关心的杂散点位于环路以外,从而利用环路将该杂散点抑制掉。一个应用实例如下所示:

实例:输出频率:12051MHz;外置5分频器;鉴相频率:10MHz

输出频率:12051MHz;外置5分频;鉴相频率:40MHz

从上述实例中可以看出,同样锁定12051MHz频点,当选取40MHz鉴相频率时,各阶杂散点距离主频最近的位置为9.4MHz,远远大于环路带宽,因此可以通过环路很好的将小数杂散抑制掉。

3.2 已知输出频率和鉴相频率

在已知输出频率和鉴相频率的情况下,小数杂散点的位置都已固定(具体计算方式已给出),此时可以选取合适的环路带宽使关心的杂散点处于环路以外,从而利用环路将该杂散点抑制掉。应用实例如下所示:

实例:输出频率:12076MHz;外置5分频;鉴相频率:10MHz

根据上述计算结果,距离主频最近的杂散点位置为400kHz,因此在设计过程中,将环路滤波器的带宽选取为小于400KHz,那么就可以很好抑制一阶、二阶、三阶杂散。

3.3 通过调偏电荷泵的方法改善小数杂散

小数模式下电荷泵上下偏电流一直处于工作状态,但是电荷泵的上下偏电流由于工艺问题不可能做到完成对称(上偏电流由PMOS镜像,下偏电流由NMOS镜像),此时由于电荷泵电流不对称,会导致电荷泵的线性度变差,从而恶化小数锁相环的杂散性能[4],电荷泵工作原理如图3所示:此时可以使鉴相器运行在有一定限制的相差下,这种相差条件下能够使鉴相器VCO输入信号的相位或者参考输入信号的相位始终处于超前的状态,从而降低电荷泵的非线性,改善小数杂散性能。假设电荷泵的offset上偏电流打开,由于offset 电流不由鉴相器开关控制,所以整个鉴相周期T内它都一直给环路充电,假设锁相环处于锁定状态,周期T内充的电荷量为Q1=T*Ioffset,要想达到平衡则需要放掉这些电荷,放电时间为detaT=Q1/I。在此种工作模式下,如果offset电流过大则有可能导致电荷在一个周期内无法达到平衡,从而导致失锁,如果offset电流过小则可能改善效果不明显[5]。

图3 鉴相器内电荷泵架构

4 产品制作及测试

利用文中给出的方法对一款小锁锁相环产品进行了设计并生产,其中鉴相频率为10MHz,锁定频率为12.076GHz,产品最终封装为12mm*15mm*3mm,产品照片如图4所示:

图4 鉴相器内电荷泵架构

杂散频谱测试如图5所示:

图5 频谱测试结果

从测试结果中可以看出,各阶小数杂散均小于-60dBc,性能指标良好。

5 结论

本文分析了小数分频的产生机理及实现方式。然后基于该理论推导出了小数杂散点具体的分布位置。根据上述分析的结论,可以很好的指导我们选择合适的鉴相频率或者环路带宽从而获得优良的小数杂散性能。最后根据小数工作机理给出一种优化小数杂散的方法,并利用实例验证了该方法的有效性。