无晶振USB 2.0设备时钟的新型校准设计与实现

王 周,刘兴辉,赵建中

(1.辽宁大学 物理学院,辽宁 沈阳 110000;2.中科院微电子研究所,北京 100000)

0 引 言

USB总线作为一种高速串行总线,其极高的传输速度能满足高速数据传输的应用环境要求,同时因其兼有供电简单、便捷、扩展简易、兼容性好、支持热插拔等优点,现已逐步成为各类电子器件数据传输所使用的标准扩展接口和必备接口之一[1]。USB设备对速率及偏差有着严格的协议,在高速模式下,USB接口的数据速率为480×(1±0.05%)MHz,应用如数码相机;在全速模式下,USB接口的数据速率为12×(1±0.25%)MHz,应用如声音传输;在低速模式下USB接口的数据速率为1.5×(1±1.5%)MHz,应用如鼠标等。

传统无晶振内部电路的设计多为采用RC振荡器[2],由于内部RC振荡电路时钟频率会随着PVT等因素漂移,而可能在中心频点产生最大±25%的频率偏差,不能够满足USB设备在全速模式时钟精度±2 500 ppm,以及高速模式时钟精度为±500 ppm的协议要求[3],必须设计无晶振USB芯片的内部时钟自校准电路,经校准后满足精度的准确时钟才能够用来做USB内部电路的时钟。现有设计多是基于识别起始帧(Start of Frame,SOF)包,以SOF包间隔为时间基准,即USB标准协议要求的SOF全速固定间隔1 ms做校准调整[4-5]。

文献[6]只对USB传输数据包的标识符(Packet Identifier,PID)进行判断是否是SOF的PID域,降低了SOF识别电路的设计难度,但是在复杂的电路工作环境中,USB总线信号上存在着各种干扰,使信号电平瞬间翻转,导致误识别或者丢失SOF包的概率存在。另外,由于内部振荡器时钟频率在未校准前采样时钟频率会存在较大偏差,进一步加大了识别SOF包错误的概率。

文献[7]对SOF包全部信息做校验来确定是否为SOF包,利用传统时间基准SOF间隔做校准。但是SOF包内标准的同步(Synchronous,SYNC)字段的KJKJKJ序列是固定的长度,首次同步时可用来做校准电路的一个基准,包括文献[7]的现有设计均未利用SYNC码计数值为基准在初次采样到SOF,即校准时钟偏差。

基于此,本文提出无晶振USB 2.0设备时钟的新型校准设计方法,针对无晶振USB设备内部振荡电路输出时钟做时钟校准。首先对USB串行差分数据信号进行多相位采样,识别SOF包内SYNC码的KJKJKJ序列进行计数,根据计数值调整RC振荡器参数进行一次预校准,将偏差锁定在一个较小范围,然后再利用补偿思想,对SOF包全部信息进行校验,自校准速度更快更准。利用SOF包的SYNC码参与校准,这对于频率偏差较大时锁定速度和准确度的提升是十分明显的。

1 无晶振USB设备时钟校准技术方案

1.1 SOF包格式

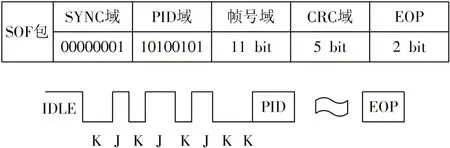

USB 2.0协议规定的SOF包[8-9]具体包括8 bit的SYNC域、8 bit的PID域、11 bit的帧号(Frame Number)域、5 bit的循环冗余校验(Cyclic Redundancy Check,CRC)域及2 bit的信息包结束(End of Packet,EOP)域。其中,EOP域是2 bit的USB总线DP/DM两个差分信号都为低电平的(Single Ended,SE)状态,作为包结束标志。包格式及编码[10]后的部分波形图如图1所示。

图1 SOF包格式及编码后的部分波形图

1.2 识别过程

本校准方法包括以下步骤:

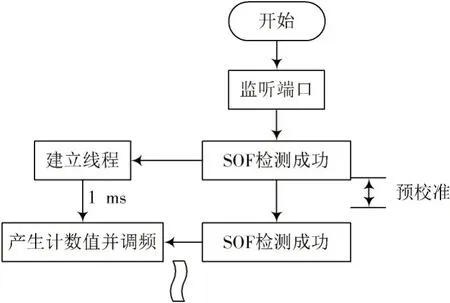

步骤1:采样识别USB 2.0总线数据上的SOF包,同时对包内SYNC码的KJKJKJ序列期间进行计数,SOF包完整识别后输出计数值进行预校准RC振荡器,并输出校验SOF成功标志。

步骤2:进入正常模式进行计数,在下一次完整检测出SOF包,利用此时计数结果与预设的应当计数值[11]进行比较,根据比较的结果调整输出参数。

步骤3:根据输出参数调整RC振荡器输出时钟频率。

在内部时钟未达到协议规定的偏差精度前,正常模式下周期循环步骤1~步骤3,做动态校准。频率调整示意图如图2所示。

图2 频率调整示意图

1.2.1 步骤1检测SOF具体流程

1)将USB串行差分总线信号转换成单信号的串行信号和SE0状态信号。

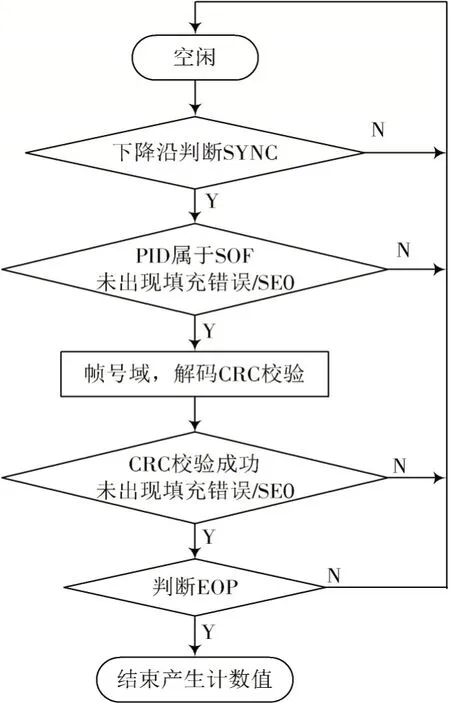

2)判断信号是否出现SYNC特征。当检测到信号下降沿时,统计串行信号每个比特位当前时钟脉冲的周期数,进一步若信号数据符合SYNC域的“010101”特征,则判断检测SYNC码成功,输出成功标志,锁定SYNC脉冲总计数值直到一次校准结束清0,进入步骤3);否则回到空闲状态等待下降沿。

3)检测PID域。根据步骤2)计算的每bit脉冲平均时钟周期数,利用补偿思想对后面的串行信号进行10个周期数的数据采样,解码并判断2~10 bit位信号值是否符合PID域值特征为“10100101”,若是则进入步骤4),若否则等待串行差分信号检测到SE0回到空闲状态,或者USB串行差分信号出现位填充错误,立即返回空闲状态。

4)接收帧号域同时进行CRC校验计算。利用补偿思想继续进行11个信号脉冲周期数据采样,解码信号的帧号域值并锁存入寄存器进行CRC校验运算,进入步骤5),此过程中若检测到SE0状态或者发现位填充错误则立即返回空闲状态。

5)接收CRC域,判断CRC校验结果。利用补偿思想继续数据采样5个信号脉冲。解码信号的CRC域值并锁存入寄存器进行CRC循环冗余校验运算。若校验结果准确则进入步骤6),否则等待串行差分信号检测到SE0回到空闲状态,或者发现位填充错误立即返回空闲状态。

6)检测EOP。USB串行差分信号出现连续两个单比特的SE0状态,即为USB传输包结束标志EOP。若检测到EOP则证明SOF包检测成功,开始校准计数并回到空闲状态,否则2个信号脉冲周期后同样返回空闲状态。预调准模式下检测成功则输出SYNC“010101”单比特脉冲计数值,进行RC振荡器预校准,校准一次后进入正常模式。检测SOF流程如图3所示。

图3 检测SOF流程

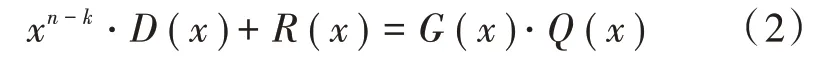

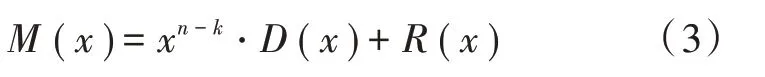

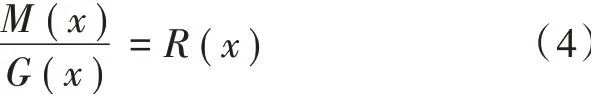

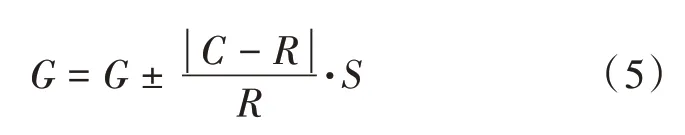

1.2.2 CRC5校验算法

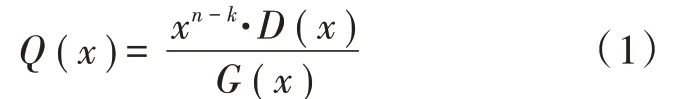

数据在计算机系统中形成、存取和传送的过程中,由于随机噪声的影响可能发生错误,USB协议为了检测和减少这类错误,对每个包提供了循环冗余校验,若出现了错误,则认为该包损坏[12]。设D(x)代表信息码多项式,G(x)为系统规定的生成多项式,信息码长度为k位,循环冗余码长度为n位,则校验码的长度为(n-k)位。

1)循环冗余码的发送

首先,利用生成多项式G(x)的最高位xn-k去乘D(x),然后用G(x)去除可得:

余数为R(x)。由于没有进位模2的加减法都是一样的,所以应有:

然后将式(2)左边作为信息码M(x)发送去接收端。

2)循环冗余码的接收

即:

余数为0表示除尽。如果传输有错,余数则不为0。

1.2.3 步骤2计算过程

预处理后进行正常模式,利用待校准时钟对从成功检测到SOF到下次成功检测到SOF之间1 ms进行计数,利用计数值C与预设的计数值R通过式(5)得到要调整的RC振荡器参数G,对应RC振荡器调整的不同档位。

式中S为满足精度的RC振荡器所能调整的最大档位范围值。

2 核心思想

预处理思想:利用SOF包的SYNC域经编码后的KJKJKJ电平翻转进行计数,在此状态中理想计数值应为一固定值a,但由于PVT导致的振荡器时钟频率漂移后计数值为b,第一次锁定之前a,b值会有较大的偏差范围,利用a,b的值对应C,R分别代入式(5),调整RC振荡器参数G做预校准。

补偿思想:频率存在偏差时,相对于数据脉冲,采集数据的时钟边沿会累计出现前移或后移,如果每次都在同一时刻采样数据,会累计出错。设计利用SOF包的SYNC域经编码后的KJKJKJ电平翻转进行计数,取6周期平均值,保留余数部分,即为单比特脉宽整数值n和余数值m,对后续的USB串行差分信号进行补偿采样,确定每个比特位所代表的电平值。

具体补偿采样与判定USB串行信号单比特电平值的方法为:利用2个计数器,即计数器1(整数计数器)和计数器2(余数计数器),对USB串行信号进行采样计数。采样过程中,若检测到USB串行信号边沿跳变(上升沿或下降沿),则初始化计数器1和计数器2为若采样到USB串行信号为电平状态,则计数器1加1。当计数器1的值为时,则判定此刻串行信号的电平为USB串行信号的取值电平。当计数器1的值累加到n-1时,则该时刻计数器1归0,并且将计数器2的值增加m。同时,采样过程中,若计数器2的值大于等于6(全速模式单bit脉冲标准计数值),代表小数部分的采样周期已经冗余出整数个采样周期,则在下一时刻将计数器2减去6。并且在此时刻暂停1周期计数器1计数,补偿小数部分溢出的采样周期,防止由于小数部分采样周期的累加,导致后续采样电平误判而引起SOF包识别错误。以每个待校准时钟采样周期的速度对USB串行信号取值。

3 仿真结果分析

本文设计研究的无晶振USB 2.0设备时钟的新型校准设计方法采用Semiconductor Manufactory International Corporation 65 nm工艺,全速模式下把时钟频率校准到满足协议要求,设计的仿真综合使用Synopsis的仿真综合工具。

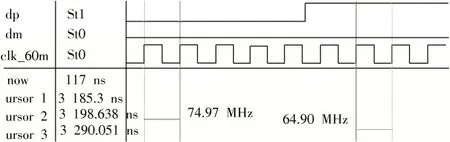

图4为正偏差较大时预处理后的时钟频率校准结果仿真波形。对SYNC的KJKJKJ序列多相位采样,首次检测到SOF时利用计数值进行预校准,初始待校准时钟为74.97 MHz,正偏差24.95%,将待校准时钟校准到64.90 MHz,偏差缩小了16.79%,同时可见初始频率的偏差越大,预校准后缩小幅度越明显,对后续校准越有利。

图4 正偏差校准波形

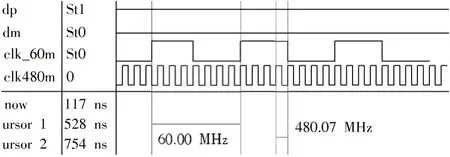

图5为第11次校准时的时钟频率。本设计所使用的RC振荡器有2 048个可调整的档位,结合图5可以看出校准到11次时,RC振荡器输出的时钟已经能够满足协议的要求。图5中,高速模式下时钟周期为2 083 ps,频率为480.07 MHz,相对于480 MHz时钟频率满足500 ppm的要求;全速模式下时钟周期为16 668 ps,频率为60.00 MHz,相对于60 MHz的时钟频率满足2 500 ppm。

图5 校准完成时钟频率

表1为本文所提USB 2.0设备的无晶振时钟校准设计方法与相关文献在校准目标、校准精度、第一次校准的时间点对比。从中可以看出,本设计方法相对其他方案在速度、准确度方面有所提升,优于其他设计。对于偏差较大的初次校准,本文设计更能节省校准时间,也能提高后续校准精度。

表1 不同设计的校准方案

4 结 论

本文提出一种无晶振USB 2.0设备内部振荡电路时钟校准设计方法并进行实现。本设计同时利用SOF包内SYNC码JKJKJK序列及SOF包间隔做时间基准,利用时间基准内待校准时钟计数值调准RC振荡器输出时钟频率,优势是第1次校准,采集到SOF包即可进行校准,缩小时钟偏差,而无需连续2次准确采集到SOF包,最终将时钟频率校准到全速60.00 MHz,高速480.07 MHz满足协议要求的频率偏差范围。