基于四路ADC芯片交替采样的宽带信号采集系统设计

雷 雯,栗敬雨

(1.海军驻湘潭地区军事代表室,湖南 湘潭 411100;2.国防科技大学 前沿交叉学科学院,湖南 长沙 410073)

逆合成孔径雷达(Inverse Synthetic Aperture Radar,ISAR)能够获取空间目标的高分辨图像,是近地空间探测领域中获得目标具体信息的有效途径之一[1-2]。增大逆合成孔径雷达的信号带宽是提升ISAR图像分辨率的发展方向[3]。目前国际上先进的逆合成孔径雷达的信号带宽已经达到数个吉赫兹[4-6]。根据采样定理,系统采样频率应至少大于模拟信号带宽的两倍,这就要求ISAR的采集系统具有极高的模数转换速率。在一些特殊应用场景中,单片模数转换器(Analog to Digital Converter,ADC)无法满足系统对采样率的要求。并行交替采样(Time-Interleaved Analog-to-Digital Converter,TIADC)技术是提升系统采样率的有效方法。该方法将采样率较低的若干个ADC在相同的时钟频率、不同的时钟相位下交替采集信号,然后将这些ADC的采样数据按照顺序组合输出,即可提升系统的采样率[7-18]。

本文针对单片高精度ADC的采样率无法满足大带宽雷达系统中频直接采样的问题,设计了一种基于四路ADC芯片交替采样的宽带信号采集系统。该系统具备对5 GHz带宽的雷达信号进行高精度直接采集的能力,为基于多路ADC芯片交替采样的信号采集系统提供了技术基础和设计参考。

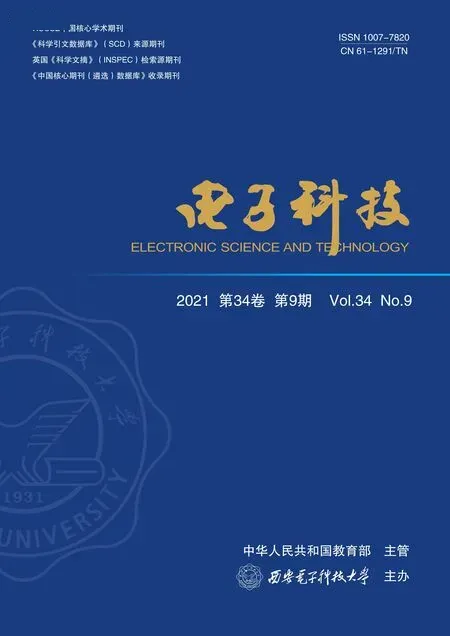

1 多路ADC芯片交替采样模型

采样率较低的M个ADC在相同的采样时钟频率、不同的采样时钟相位下并行采集信号,然后组合这M个ADC的采样序列作为系统输出以增加采样率。多路ADC芯片交替采样系统的模型如图1所示:采样时钟经过多个固定的延时器后得到系统所需的多个相位的采样时钟;模拟信号经等功率分配后分别送入各个ADC进行采样;各路采集的数据在多路合成器中合并输出数字信号。

图1 M通道交替采样系统模型Figure 1. The model of M-channels TIADC system

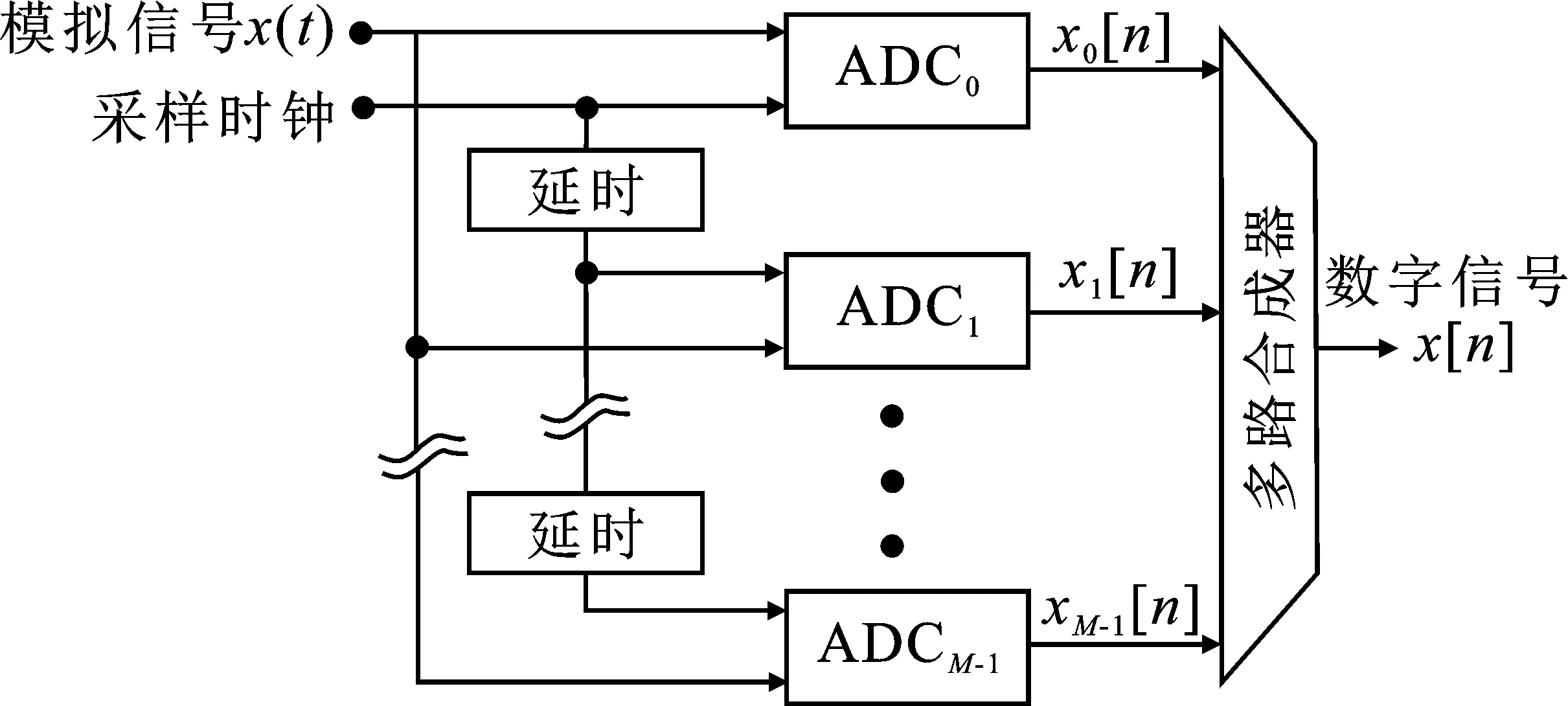

设通道数M=4,交替采样系统各通道采样时序如图2所示。模拟信号在每个相位的时钟的上升沿被ADC采集,采集输出数字信号的采样率是单个ADC采样率的4倍,即系统的采样率得到成倍提升。

图2 四通道交替采样系统时序图Figure 2. The sequence diagram of four-channels TIADC system

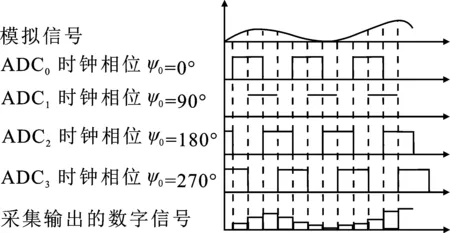

2 系统总体设计

Open VPX平台在电路模块化、数据传输带宽、可扩展性以及可靠性等多方面有着突出优势,是数字化雷达接收机和信号处理平台的重要发展方向。本文设计的TIADC系统基于Open VPX平台,如图3所示。该系统采用4片采样率为3.4 GS·s-1的ADC芯片进行交替采样,其总采样率为13.6 GS·s-1。系统硬件主要包括:4块采集卡、两块FPGA(Field Programmable Gate Array)处理板、两块后光纤板、1块时钟板、两个功率分配器和1块机箱背板。采集卡的设计采用FPGA夹层卡(FPGA Mezzanine Card,FMC)的形式。模拟信号与功率分配器相连,通过功率分配器将信号分为4路,这4路信号分别送到4块采集卡中。基准时钟与时钟板相连,产生FMC采集卡所需的采样时钟和SYSREF时钟。背板起到电路板互连和供电的作用。ADC采集的数据首先在FPGA中进行预处理,然后送至DDR3进行数据缓存,缓存后的数据通过MGT(Multi-Gigabit Transceiver)进行传输。后光纤板中的光收发器将采集到的数据从电信号转换成光信号,通过光纤向后端储存设备进行传输。

图3 系统总体设计框图Figure 3. System overall design diagram

3 功能板卡设计

3.1 FMC采集卡设计

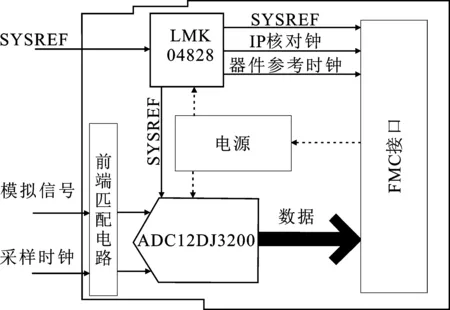

本文采用TI公司的商用ADC(ADC12DJ3200)实现单板3.4 GS·s-1采样率的FMC采集卡。ADC芯片的量化位数为12位,带宽为8 GHz。ADC芯片的采样时钟路径中有一条可变延迟线,可用于调整多路ADC芯片TIADC系统各采集通道的相位。ADC12DJ3200工作在JESD204B子类1的模式下,采用SYSREF时钟进行各通道的数据同步。LMK04828是TI公司针对JESD204B器件设计的一种时钟芯片。该芯片工作在零延迟模式,锁定输入参考时钟与输出各路时钟的相位关系,为ADC提供SYSREF时钟,为FPGA提供SYSREF时钟、JSED204B IP核时钟和器件参考时钟。前端匹配电路实现了单端信号转换差分信号和信号路径的阻抗匹配。FMC采集卡的结构设计如图4所示。

图4 FMC采集卡结构图Figure 4. The framework of FMC

3.2 FPGA处理板设计

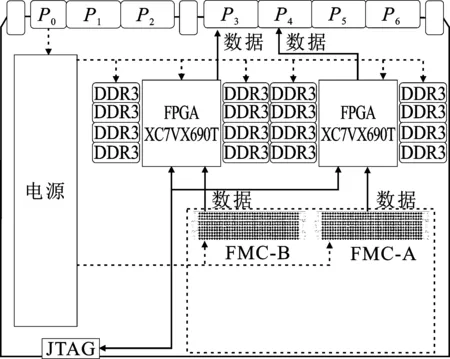

FPGA处理板的结构设计如图5所示。FPGA处理板集成了两个FMC接口,实现与FMC采集卡的多通道高速串行通信,接收来自FMC采集卡的数据,并在FPGA中进行JESD204B帧对齐、位宽转换、数据打包等预处理,然后通过P3和P4接口将数据传送到后光纤板。雷达信号中频直接采集数据的峰值速率非常高,需要通过高速缓存减小数据传输的压力。每块处理板上集成2片Xilinx公司的高性能FPGA(XC7VX690T),每片FPGA外接2组2 GB容量的DDR3缓存。

图5 FPGA处理板结构图Figure 5. The framework of FPGA board

3.3 时钟板设计

对于TIADC系统而言,时钟的设计非常关键,要从端口数量、时钟频率、时钟幅度、时钟同步、输出相位噪声等多方面进行考虑。为产生4片ADC12DJ3200需要的1.7 GHz采样时钟和5 MHz的SYSREF时钟,本文设计了如图6所示的时钟板。TI公司的时钟芯片LMX2582具有两路同步时钟输出,一路用于产生1.7 GHz采样时钟,另一路用于时钟芯片HMC7044的外部VCO(Voltage Controlled Oscillator)。本文设计的TIADC系统需要4路采样时钟。LMX2582输出的1.7 GHz采样时钟经过低噪放(Low Noise Amplifier, LNA)放大后,再通过功率分配器分为4路,分别送至4个FMC采集卡。ADI公司的时钟芯片HMC7044用于产生FMC采集卡所需的相参SYSREF时钟。HMC7044将LMX2582输出的一路1.7 GHz采样时钟分频得到5路5 MHz的SYSREF时钟,其中4路分别送至4个FMC采集卡。

图6 时钟板结构图Figure 6. The framework of clock board

3.4 后光纤板设计

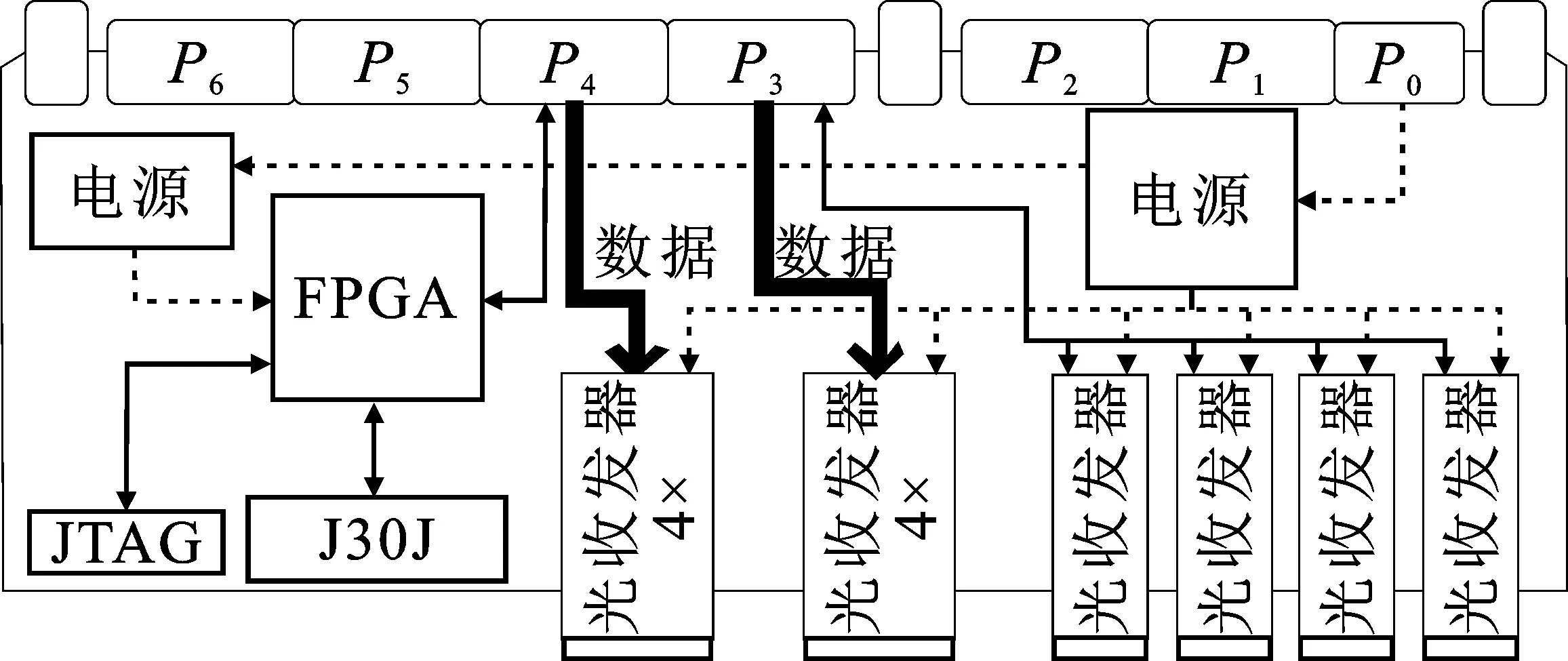

后光纤板与FPGA处理板通过背板互连,等同于对FPGA处理板扩展了光收发器和J30J接口,将采集的数据通过光纤向后端储存设备进行传输。后光纤板的接口主要包括两个四通道光收发器、4个单通道光收发器和1个J30J接口。每个4×光收发器由4个光纤通道组成,单个光纤通道支持10 Gbit·s-1的最大传输速率,用于传输采集数据。单通道光收发器可用于接收采集控制信息,并通过P3传递到FPGA处理板。J30J接口用于接收RS-422信号,该信号通过P4传输到FPGA处理板。后光纤板的结构设计如图7所示。

图7 后光纤板结构图Figure 7. The framework of backend fiber optic board

4 测试与分析

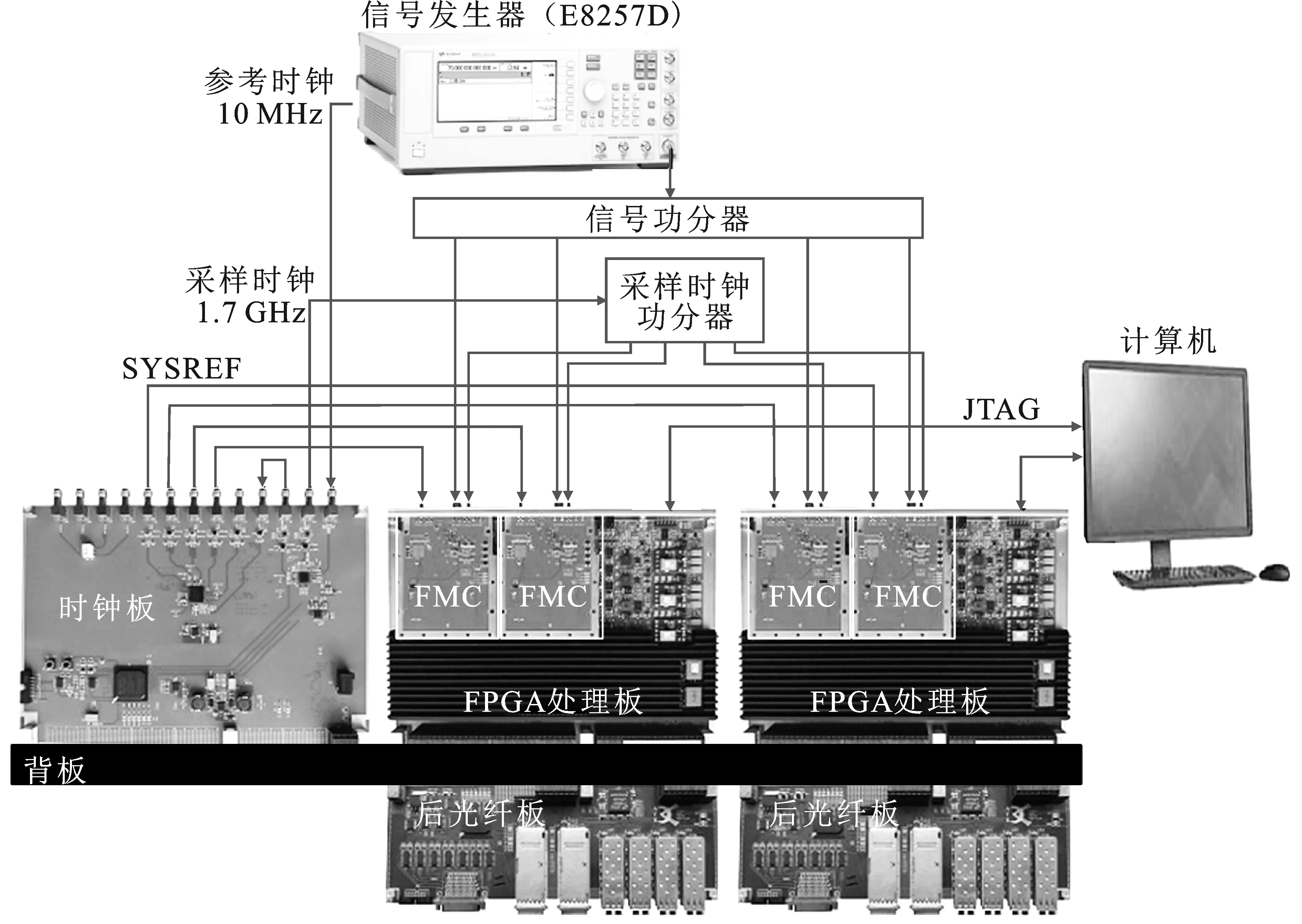

对设计的基于四路ADC芯片交替采样的宽带信号采集系统进行测试,测试环境如图8所示。系统采用4个3.4 GS·s-1的FMC采集卡交替采样,实现了一个采样率为13.6 GS·s-1的四通道TIADC系统。时钟板所需的10 MHz参考时钟由信号发生器的后面板输出端口产生,用于测试系统采样性能的正弦信号由信号发生器的前面板输出端口产生。测试信号通过功率分配器后分别传输到4个FMC采集卡。时钟板产生的1.7 GHz采样时钟通过另一个功率分配器后,传递到这4个FMC采集卡。通过FPGA处理板上的JTAG(Joint Test Action Group)接口获取采集数据,在计算机中利用MATLAB软件进行采样性能计算。

图8 TIADC系统实验测试环境Figure 8. Experimental setup for the TIADC system

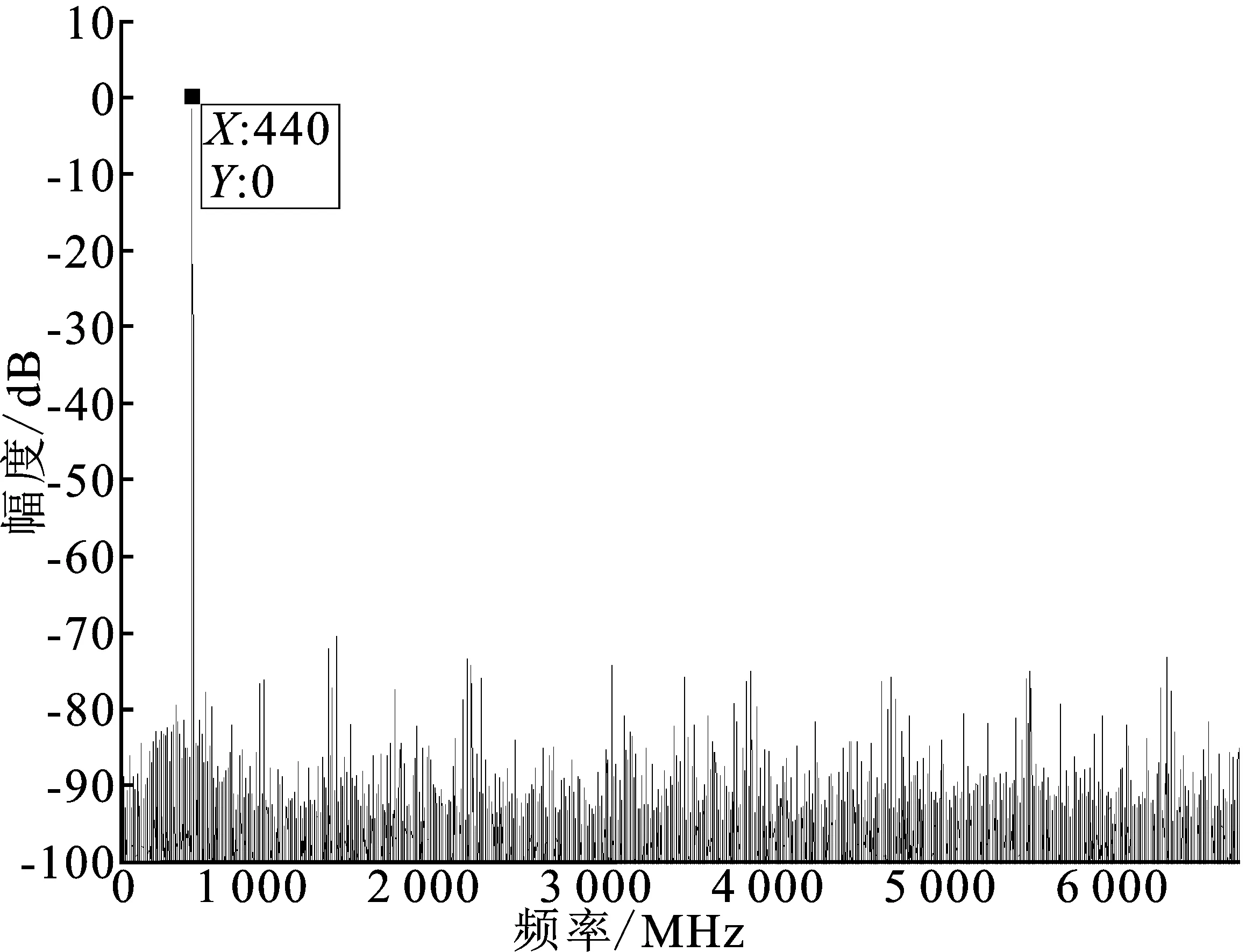

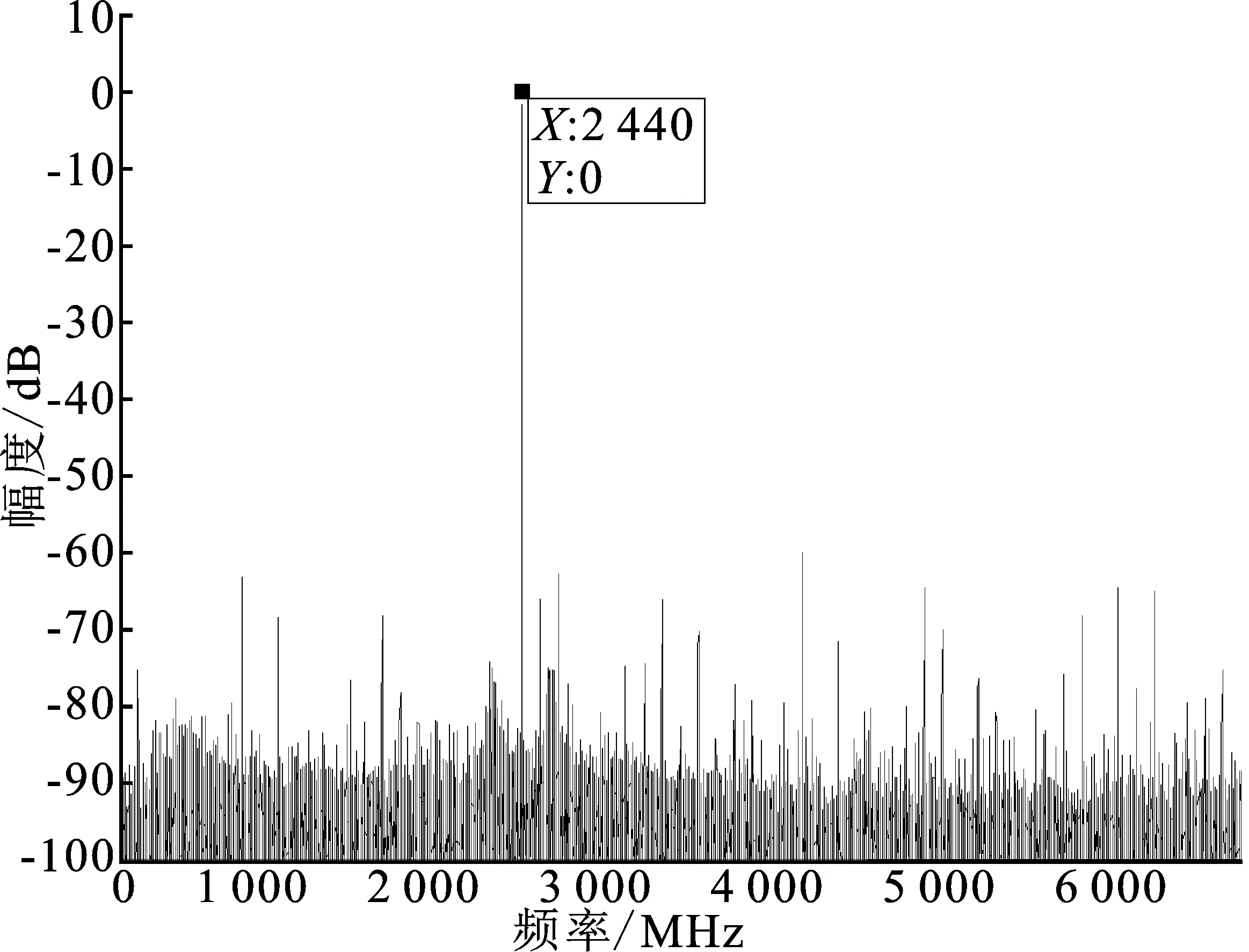

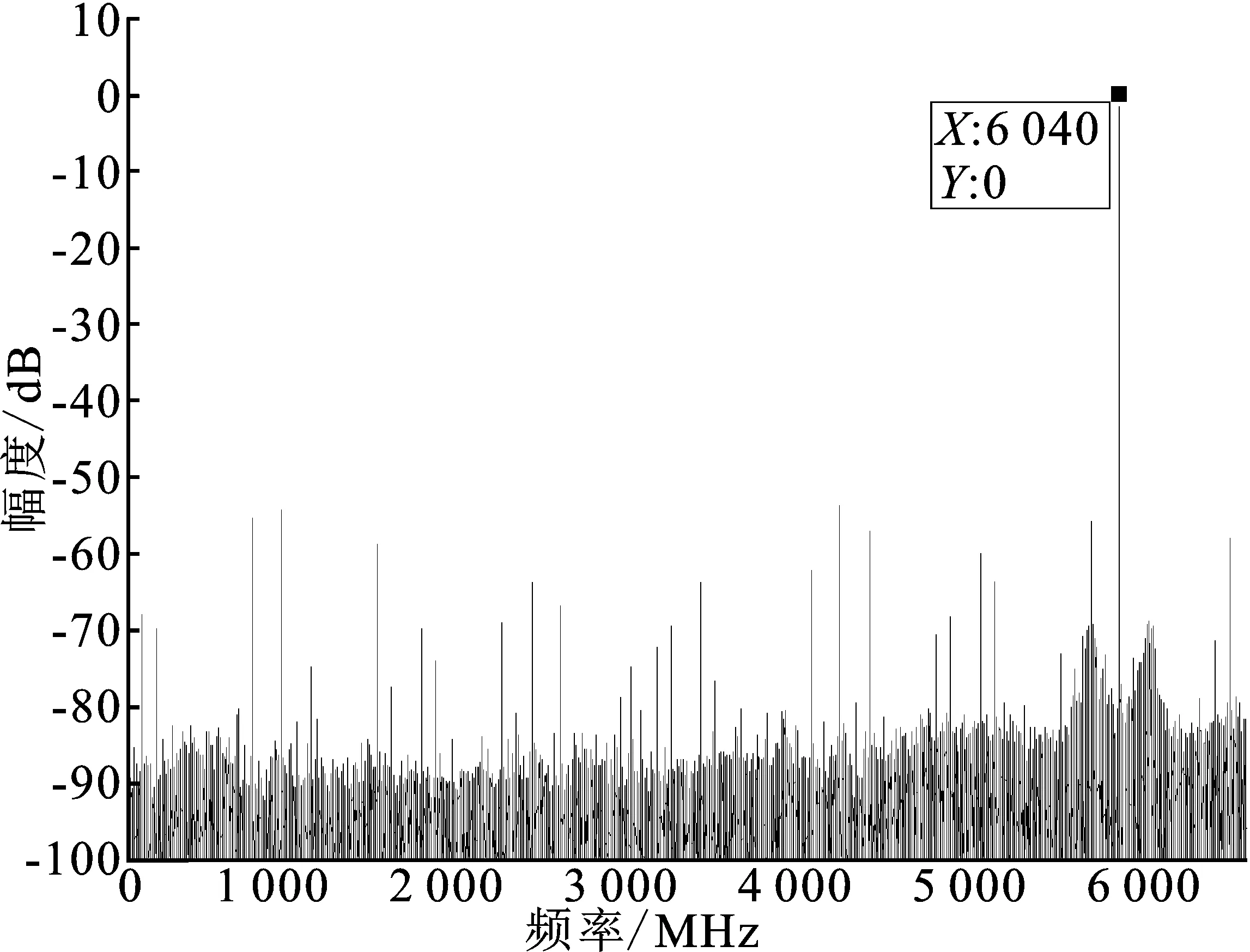

向系统分别输入440 MHz、2 440 MHz、6 040 MHz的正弦波信号,采集后的频谱如图9~图11所示。

图9 系统采集440 MHz正弦信号的频谱Figure 9. The spectrum of 440 MHz sine signal sampled by the proposed system

图10 系统采集2 440 MHz正弦信号的频谱Figure 10. The spectrum of 2 440 MHz sine signal sampled by the proposed system

图11 系统采集6 040 MHz正弦信号的频谱Figure 11. The spectrum of 6 040 MHz sine signal sampled by the proposed system

输入信号频率为440 MHz时,TIADC系统的有效位(Effective Number of Bits, ENOB)是8.67 bit,无杂散动态范围(Spurious Free Dynamic Range,SFDR)是71.6 dB。输入信号频率为2 440 MHz时,TIADC系统的ENOB是7.93 bit,SFDR为60.2 dB;输入信号频率为6 040 MHz时,TIADC系统的ENOB是7.00 bit,SFDR为53.6 dB。该系统对低、中、高频正弦信号采样均能够获得良好的采样性能。

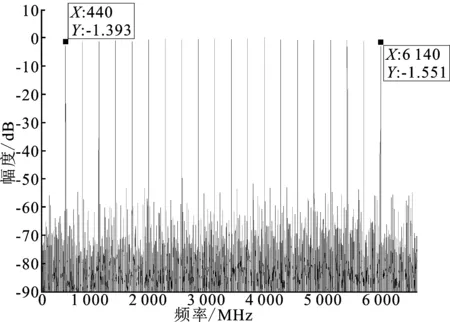

在该系统上进行多音功率比(Multi-Tone Power Ratio,MTPR)测试。多音正弦信号频率从440 MHz到6 140 MHz,频率间隔300 MHz。TIADC系统采集该多音正弦信号的频谱如图12所示。从该图可以看出,系统对宽带信号采样,能够有效地抑制杂散信号。

图12 系统采集多音正弦信号的频谱Figure 12. The spectrum of multi-tone sine signal sampled by the proposed system

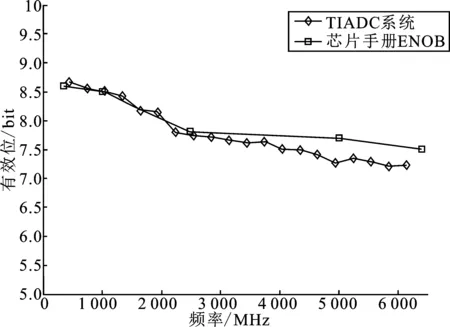

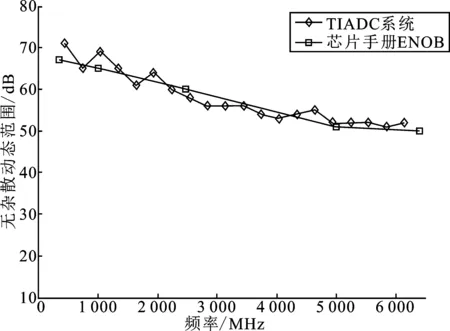

该系统的采样性能与ADC芯片手册中测试性能的对比如图13和图14所示。从测试结果可以看出,在440~6 140 MHz频率范围内,本文设计的基于4路ADC芯片交替采样的宽带信号采集系统的ENOB>7.2 bit,SFDR>51 dB。在采样率成倍提升的条件下,本文设计的TIADC系统的ENOB和SFDR接近ADC芯片手册中的测试值,具有良好的采样性能。

图13 系统的ENOB测试结果Figure 13. The test results of ENOB

图14系统的SFDR测试结果Figure 14. The test results of SFDR

5 结束语

本文设计并实现了一种基于四路ADC芯片交替采样的宽带信号采集系统,单片ADC采样率为3.4 GS·s-1,系统总采样率为13.6 GS·s-1,量化位数为12 bit。该系统在440~6 140 MHz频率范围内时,对ENOB>7.2 bit,SFDR>51 dB,均接近ADC芯片手册中的测试值,在保持ADC采样精度不变的条件下成倍提升了系统采样率。系统具备对5 GHz带宽的信号进行高精度直接采集的能力,解决了单片高精度ADC的采样率无法满足大带宽成像雷达中频直接采样的问题,为基于多路ADC芯片的TIADC系统提供了技术基础和设计参考。