基于变压器反馈的平坦噪声系数超宽带CMOS低噪声放大器

吴小平 刘继业 郑士源 吴亮

0 引言

互补金属氧化物半导体(CMO)技术以其易于集成、较低成本和较高良率的优势在射频芯片领域有广泛的使用.在室内定位等移动通信技术的发展趋势下,接收机前端的超宽带(Ultra-WideBand,UWB)频段(3.1~10.6 GHz)低噪声放大器(Low Noise Amplifier,LNA)模块的设计是一个非常重要的挑战.优良的UWB LNA应具有高增益、低输入反射损耗、良好的输出匹配、低而平坦的噪声系数和高线性度等指标.其中,高线性度在UWB脉冲系统中的地位举足轻重,可以使波形在放大后不易失真[1].

传统的低噪声放大器架构在超宽带实现时,噪声、增益和输入匹配之间存在较明显的性能折中关系,因此无法达到良好的综合性能指标要求.而传统的UWB LNA宽带输入匹配在信号输入端配置多个LC(电感、电容)匹配网络改变输入回波损耗的曲线特性,但是片上LC的低品质因数不仅会引入较大的噪声,而且存在增益衰减[2].近年来,一种采用电感反馈的输入匹配结构在宽带匹配中展现了优势[3],该结构在输入匹配的情况下允许有更高的晶体管跨导来提高增益并减小噪声.此外,传统结构的UWB LNA多采用单端结构,并配置源跟随器做输出驱动,但单端结构的抗干扰能力较差.对于源跟随器而言,虽然其结构的输出阻抗很小,但在差分结构中差分转单端功能的缺少使芯片不易测试,而且LNA整体的线性度也会被限制.综合来看,良好的增益平坦和群时延变化已经可以实现[4],高增益的UWB LNA也可以实现[5],但是文献[5]等高增益LNA的噪声系数比较差.低噪声(<3 dB)且平坦噪声系数(<0.3 dB)的高增益LNA还没有被设计.综上,UWB频段的高增益低噪声放大器的总体性能还比较低.

尽管是低频设计,文献[3]的高综合性能依然可以给高增益UWB LNA的性能改善带来启发.本文采用基于变压器反馈的共源共栅结构作为第一级,一种多功能输出驱动结构作为第二级,使该LNA实现了高增益下良好且更平坦的噪声系数和更优的综合性能.在版图后仿真部分中,LNA芯片偏置电压上的金属焊盘(pad)、pad连接到外部电源的金丝键合线和版图内部金属长连线的寄生效应均被考虑进去.仿真结果表明,在差分结构的虚地特性下,它们对LNA的影响被极大地抑制.

1 变压器反馈和输入阻抗

图1是该LNA 采用的结构,图2是其单端等效的第一级结构原理.其中:Vs是电压小信号的输入端,Vo1是该级的输出端;M1和M2是同长同宽的增强型NMOS晶体管,M3为增强型PMOS晶体管;电阻Rs模拟输入测试探针的阻抗,默认50 Ω;初级电感Lp和次级电感Ls形成的变压器用于输入匹配;初级线圈和次级线圈的圈数比为n∶1,耦合系数为k;电感Lk和电阻RL串联作为输出负载,等效阻抗为Rp.

图1 低噪声放大器原理Fig.1 Schematic of Low Noise Amplifier (LNA)

图2 基于变压器反馈的第一级放大器单端结构Fig.2 Single-ended first stage of LNA with transformer feedback

经小信号模型分析,该LNA的输入导纳可表达为(假设CB足够大):

s2LsgM1Cgd1,

(1)

沿此思路设计的电感反馈变压器如图3所示.为了实现较大的耦合系数k,电感Lp和Ls采取了交错式跨接的方法,M8(版图中第8层金属)为换层跨接,M9为变压器主体部分.线间距为最小的2 μm,线宽取3 μm,变压器的最终尺寸为 158 μm×158 μm.

图3 输入匹配变压器Fig.3 Input matching transformer

耦合系数的电磁仿真结果如图4所示.仿真结果表明,在3.1 GHz输入匹配变压器的耦合系数大于0.68.在3~10 GHz,耦合系数为0.68~0.95.Lp在6.5 GHz处约为3.4 nH,Ls约为0.9 nH.两者圈数比为3.5∶2=1.75∶1.

图4 输入匹配变压器的耦合系数仿真Fig.4 Coupling factor simulation of input matching transformer

2 电流复用和噪声抵消

为了减小放大器的噪声系数(Noise Figure,NF),该LNA的第一级沿用了文献[3]中的噪声消除方法.图5列出了3个噪声节点A,X和Y便于分析.首先确定需要优化的噪声源来自电阻Rs和M1,因为后一级的噪声会被前一级的增益所抑制,优化这两处的噪声源可以显著地减小噪声系数.在图6的噪声分析中,假设来自M1的噪声以对地电流(设为iN1)的形式出现,那么iN1在节点A处的等效电压噪声可以表示为

图5 电流复用和噪声消除Fig.5 Current reuse and noise cancellation

(2)

(3)

由此,晶体管M3的存在可以用于噪声抵消,这里使用电容CB和电阻Rb3做M3的直流偏置,CB隔直的同时也用于耦合噪声和输入信号.需要注意的是过小的CB会使输入匹配和噪声抵消能力变差.通过增益分析易得,M3的引入增大了LNA的总跨导,因此在噪声分析中等效总跨导为gM1+gM3.若同时考虑M1和M3的噪声,则总的噪声系数可以表示为

(4)

γ为M1和M3的噪声因数(假设相等),而(4)中的β为

(5)

式(5)中的r01和r03分别是M1和M3的输出电阻,它们的比值相当于两个晶体管跨导的比值.这里M1选择了宽64 μm,长60 nm的NMOS管,M3选择了宽90 μm,长60 nm的PMOS管(节省功耗).图6表明在6.5 GHz处,LNA噪声系数和M3与M1跨导比值的关系,并可以确定M1和M3的最佳跨导设置.

图6 噪声系数和M3,M1跨导比值的关系Fig.6 Relationship between noise figure and gM3/gM1

3 第一级负载端零点补偿和平坦噪声

由式(4)可知,噪声系数的变化主要由阻抗Rp随频率的变化而变化.因此为了达到平坦噪声系数,第一级的输出负载不能选择LC谐振腔,因其阻抗变化在共振频率附近很大从而无法满足设计要求.选择电感Lk和电阻RL串联做负载端即可以得到较小的阻抗变化,又可以阻碍UWB频段的高频小信号泄漏.另一方面,电感和电阻的串联会引入一个左零点来补偿增益的频率相应的带宽,使增益曲线更加平坦.另一个要考虑的设计因素是如何让3.1 GHz和10.6 GHz处的NF值尽可能保持相等并将NF最低点设计在UWB频段之间,综上才可以实现最平坦的噪声系数.

4 多功能输出驱动设计

由于超宽带LNA需要平坦的增益,在满足3.1~10.6 GHz的输入匹配下需要保证大的3-dB带宽.尽管第一级结构使用了零点补偿,其带宽依然无法满足频带的80%.因此可以考虑增加第二级做增益叠加来实现平坦增益,原理如图7所示.

图7 两级增益平坦方法示意Fig.7 Diagram of flat gain method using two stages

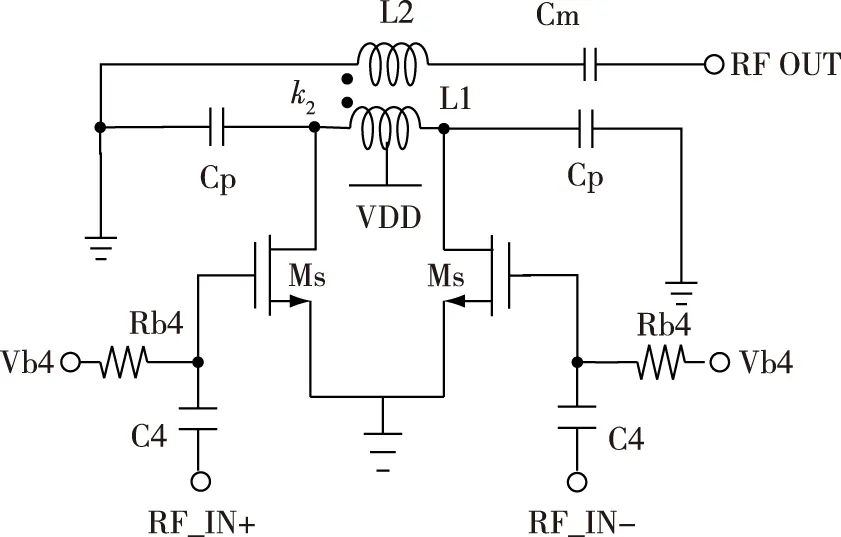

根据图7,第二级的作用主要是负责5~10 GHz的信号增益.由于第一级的3-dB带宽在补偿后有所提升,第二级的带宽可以不做严格要求.第二级还需要解决输出匹配的问题.为了方便芯片测试,该级还需具有差分信号转单端的功能,因此需要设计一个片上驱动.综上,第二级多功能输出驱动设计的原理如图8所示.

图8 多功能输出驱动Fig.8 Multi-functional output driver

第二级是差分结构的输出驱动,输入端为差分输入,第一级的小信号由电容C4耦合进第二级晶体管Ms.偏置电压vb4用于Ms的直流偏置,并避免输出端Vo1处的直流工作点和管子Ms的直流工作点产生冲突.L1为初级线圈,L2为次级线圈,二者耦合系数为k2.由于输出测试探针的特征阻抗也为50 Ω,则在单端分析下从Ms的漏端看进去的阻抗也应满足50 Ω匹配.L1端的半边串联等效输出阻抗Z1反映到L2端的并联阻抗值Z2为

(6)

n12为L1和L2的圈数比,k2为输出驱动的变压器耦合系数.为了方便设计,这里选择圈数比为1∶1.同理,高耦合系数k2可以保证Z2在频带的阻抗变化幅度较小来做较可靠的输出匹配.输出匹配则需要L2和Z2的并联阻抗满足 50 Ω,若考虑半边电路,从Ms的漏端看进去的输出阻抗表达式约为

(7)

其中M是输出变压器的互感,Cdss为Ms的漏源间的寄生电容.注意到输出电阻实部和r0s有密切关系,‖ 代表并联,而

(8)

Vdss是Ms的漏源间电压,IDs是Ms的直流偏置电流,λ是晶体管Ms的长度沟道调制参数,一般在0~0.2 V-1之间.从式(8)可得,输出电阻和偏置电流存在折中.Ms直流偏置电流过大会提高放大器的功耗,而过小会导致r0s增大从而使S22失配严重.为了降低输出电阻的实部,并联多个Ms晶体管(相当于并联多个r0s)是一种有效的方法,但依然需要和功耗做折中考虑.在信号输出端,单端输出的匹配电容Cm可以直接调整输出电阻的虚部.虽然变压器做输出的线性度要比有源器件好,但是两级的高增益需要给输出信号留出足够的电压摆幅裕度,因此这里L1的中心抽头处需要连接1.2 V电源电压,用vb4来控制功耗和输出电阻的值.

除此之外,输出驱动变压器的设计还需考虑信号的衰减带宽和衰减中心频率.从文献[7]中可得一些指导思想.对于衰减带宽,其至少需要覆盖UWB全频带.这里不妨定义UWB频段的上界频率fU为11 GHz,下界频率fL为3 GHz,而上界频率与下界频率之比又与变压器的耦合系数直接相关,表达式为

(9)

由此可以估算出在UWB频段,k2需要大于0.6.对于衰减中心频率,这里不妨假设有一个圈数比为1∶1、初级线圈为L′p的简单变压器模型,且L′p端存在一组值R的串联电阻,则衰减曲线的中心频率fpk约为

(10)

综合式(8)和式(9)的结果可得图9的输出驱动变压器的版图设计.其中电感主体层数选择M9,变压器内径为70 μm.同样为了得到较大耦合系数,这里依然和输入匹配变压器一样,采用交错式跨接法,线间距为2 μm.仿真显示,耦合系数k2在3 GHz处大于0.7,6.5 GHz处L1的电感值约5.8 nH,L2电感值约为1.62 nH.

图9 输出变压器版图设计Fig.9 Output transformer layout design

5 仿真结果与性能比较

5.1 S参数、噪声系数、稳定性、功耗和线性度仿真

本节通过Cadence和Sonnet的仿真来验证该结构的有效性.图10是UWB LNA 的S参数仿真,且晶体管的寄生参数、版图中长连线的寄生电感和寄生电容都已考虑,差分输入的信号拟来自片外巴伦,所有电源接1 nH的电感来模拟键合线,输入和输出信号端口各接35~37 fF的电容来模拟管脚的电容.

图10 S参数仿真Fig.10 Simulation of S-parameters

在3.1~10.6 GHz的频率范围下,LNA的增益(S21)为20 ±2.6 dB,3-dB 带宽为10.45-3.66=6.8 GHz,占UWB频带的90.5%.S11范围为-10~-22.4 dB.S22范围为-9.57~-16 dB,反向隔离度(S12)<-60 dB.在电源电压1.2 V的工作条件下,核心电路的静态功耗为32.8 mW.

图11是LNA噪声系数(NF)仿真,NF值为2.71±0.28 dB.

图11 噪声系数仿真Fig.11 Noise figure simulation

图12为LNA的稳定性仿真,Kf全频带大于1,B1f大于0.86,表明该LNA稳定工作.其中Kf和B1f为衡量LNA稳定性的参数.其中LNA的无条件稳定条件为Kf大于1且B1f大于0.二者分别为

图12 稳定性仿真Fig.12 Stability simulation

(11)

(12)

图13是LNA的1-dB压缩点仿真,用来衡量LNA线性度.横轴代表输入信号在6.5 GHz处的功率,纵轴代表LNA输出端口的小信号功率.在6.5 GHz处,1-dB压缩点为-17.5 dBm.

图13 1-dB压缩点仿真Fig.13 Simulation of 1-dB compression point

5.2 性能对比

本节列出了以往较好的UWB LNA的性能,并与本文的LNA性能进行对比.这里对比文中的仿真结果,并给出FoM-Ⅰ和FoM-Ⅱ的值.FoM-Ⅰ衡量不考虑线性度的放大器性能,FoM-Ⅱ为考虑线性度的放大器性能.二者的计算公式分别如下:

FoM-Ⅰ=(平均增益×(3-dB带宽))/[(功耗×(平均噪声系数-1)] ,

(13)

FoM-Ⅱ=(三阶交调点×平均增益×(3-dB)带宽/[(功耗×(平均噪声系数-1)] .

(14)

其中:平均增益和噪声系数单位:1;3-dB带宽单位:GHz;功耗和三阶交调点单位:mW.

表1主要对比CMOS工艺下高增益[5,11]的UWB LNA的仿真性能,并将其他UWB LNA 的性能列出.可以看出,在平均增益为20 dB左右时,本文LNA有最低的平均噪声系数2.71 dB,且在所有LNA 中噪声系数最平坦(±0.28 dB)同时,高增益下本文LNA有比文献[5]和文献[11]更高的1-dB压缩点,在差分结构下,其功耗也比文献[5]的低.最后,对比文献[5]和文献[11]的高增益LNA,本文结构的FoM-Ⅰ和FoM-Ⅱ更优.因此本文LNA更适于用在要求高增益、低噪声及对噪声变化敏感的场景中.

表1 LNA 性能对比

6 结束语

本文利用基于变压器反馈的输入匹配的第一级架构和第二级电感反馈的多功能输出驱动结构,实现了高增益下更低更平坦的噪声系数和更优的平均性能.差分结构也使该放大器比单端结构有更好的抗干扰和共模抑制能力.