一种微光像增强器阴极选通模块的设计

杜培德,朱文锦,周盛涛,李晓露,李亚情,褚祝军,杨可洁

〈微光技术〉

一种微光像增强器阴极选通模块的设计

杜培德,朱文锦,周盛涛,李晓露,李亚情,褚祝军,杨可洁

(北方夜视技术股份有限公司,云南 昆明 650223)

高速成像分幅相机通过阴极选通模块控制微光像增强器的光电阴极选通工作可实现ns级的时间分辨率,传统阴极选通模块存在开关速度慢、只有负压输出或正负压不能满幅值输出等问题。本文基于CMOS推挽输出结构和电压电平转移电路,设计实现一种能够使用低边驱动器驱动PMOS和NMOS开关的阴极选通模块,并采用死区时间控制避免上、下管交叉导通。实测验证该电路具有结构简单、性能可靠等优点,实现了ns级上升、下降沿,占空比0~100%可调和满幅值+30~-200V脉冲输出,十分适合微光像增强器阴极选通使用。

微光像增强器;阴极选通;正负脉冲发生器

0 引言

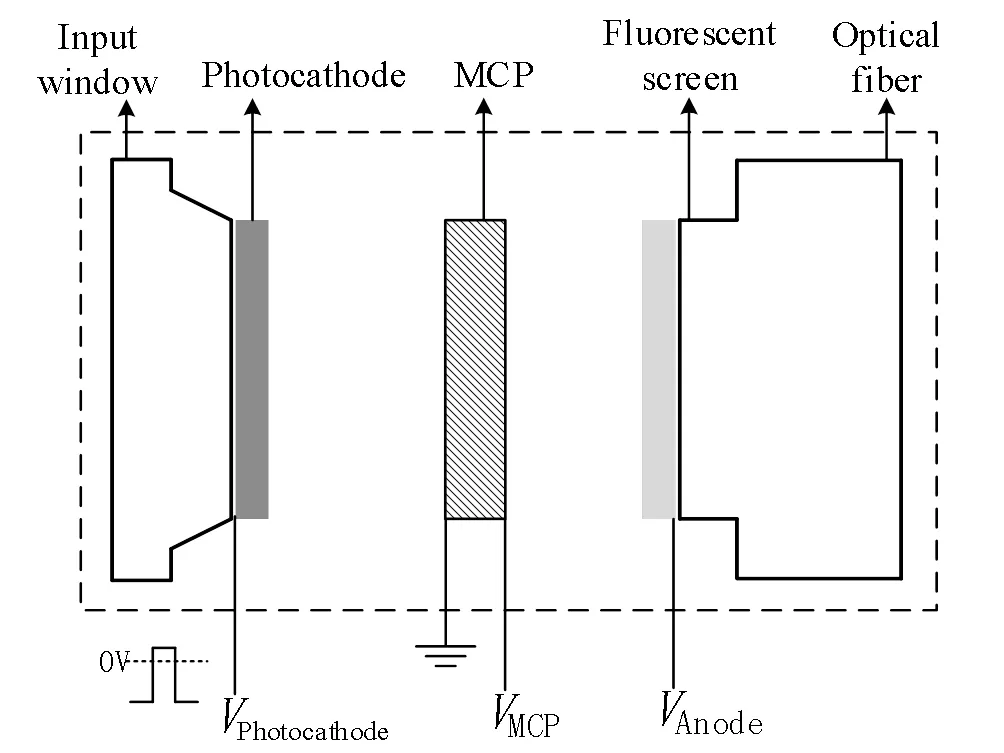

微光像增强器是将目标物体反射的极弱光线通过阴极光电转换、微通道板(microchannel plate, MCP)电子倍增和荧光屏电光转换实现图像再现和亮度增强的真空成像器件[1],除广泛用于观察镜、头盔、枪瞄等微光夜视仪中外,其具有超快成像特性,是分幅相机中的关键器件之一[2-3],这些设备利用像增强的阴极选通功能(施加到阴极的电压是一定时间宽度的正、负脉冲,负电压时阴极工作,正电压时阴极不工作)起到光学快门的作用,实现ns级的时间分辨[4]。通常,高速成像系统只提供一个低压脉宽控制信号,由专门的阴极选通模块响应并输出ns级上升、下降沿的正负高压脉冲来控制阴极工作。

目前,阴极选通模块主要采用雪崩三极管、功率MOS管等高速开关器件设计实现ns级脉冲,但雪崩三极管设计不易实现脉宽任意可调;MOS管设计则是只实现负压输出,或存在正、负压互通导致输出幅值不能达到最大的问题。

本文基于CMOS输出结构和电压电平转移电路,采用死区时间控制避免上、下管导通,设计实现一种能够使用低边驱动器驱动MOS管开关的阴极选通模块,在负载电容100pF条件下实测输出为满幅值+30~-200V正负脉冲,上升、下降时间小于8ns,最小脉宽30ns,占空比0%~100%可调。

1 设计分析

1.1 容性负载分析

图1为双近贴像增强管的结构,光电阴极、MCP和荧光屏相互靠近,采用陶瓷环隔离和铜片钎焊构接,其中阴极和MCP输入端(GND)之间的距离为0.1mm[5],近贴和陶瓷构件使得阴极和GND之间存在几十至数百pF的寄生电容[6],阴极材料为高阻半导体,因此阴极选通模块输出为容性负载。电容的基本特性是电压不能突变,且阴极电压需在+30V和-200V之间切换,电压差值高达230V,要实现高幅值且ns级上升、下降沿的脉冲,这就要求阴极选通输出对电容具有强大的充放电能力,即驱动能力。以寄生电容200pF、上升下降时间10ns为例,根据C=dC/d计算驱动能力至少为4.6A。

图1 双近贴像增强管的结构

1.2 正负输出电路结构分析

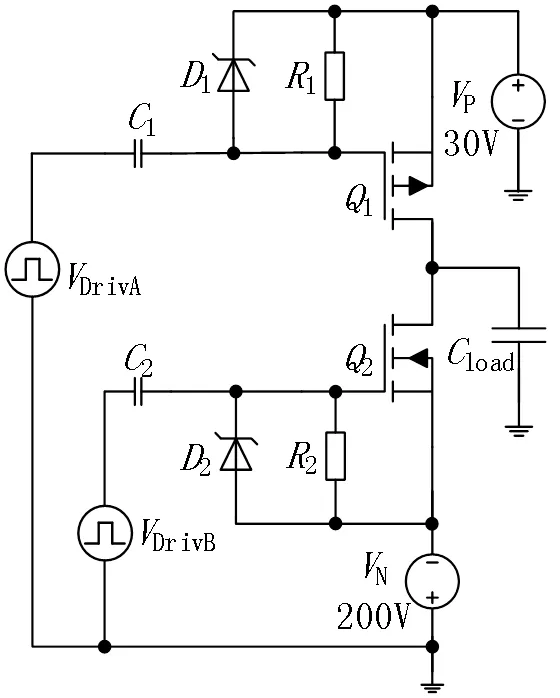

阴极选通模块的本质是一个正负输出结构,电路建模见图2(a),正电源P通过上开关管P连接至负载电容load,负电源N通过下开关管N连接至load。P和N在驱动信号DrivA和DrivB控制下互补开通和关断,便在load两端形成了正负脉冲。

P和N通常采用MOS管,为满足ns级开关速度,DrivA和DrivB应具备大电流驱动能力,需使用驱动器,但输出结点SW处会出现-200V负压,这将导致常规的高边驱动器输出闭锁[7],使得P、N贯通短路,因此需要设计专门的自举驱动或电平转移电路。另外,当输入触发脉冲占空比(y)为100%或0%时,称之为全占空比状态,自举电路或电平转移电路的电容电荷无法刷新,P、N将关断无输出,因此需设计全占空比输出维持电路。

图2(a)近似CMOS结构,存在上、下开关管交叉导通固有问题。这是因为MOS管的“米勒效应”使得开关过程存在延时,若P开通时,N没有完全关断,此时便会存在一定时间的交叉导通,导致输出幅值达不到最大,甚至P和N贯通短路,即使选择参数严格对称的PMOS和NMOS也存在交叉导通隐患。

死区时间调整可避免交叉导通,见图2(b)原理所示。当外部触发输入上升沿时,DrivA经传播延时l后翻转为低电平即P关断,DrivB继续保持为低直至经死区时间dead后翻转为高电平即N开通,在dead内P和N均关断,因此称“dead time”(死区时间),死区时间能够保证上、下管正确开关时序,因此需设计死区时间调整电路。

图2 正负输出结构分析

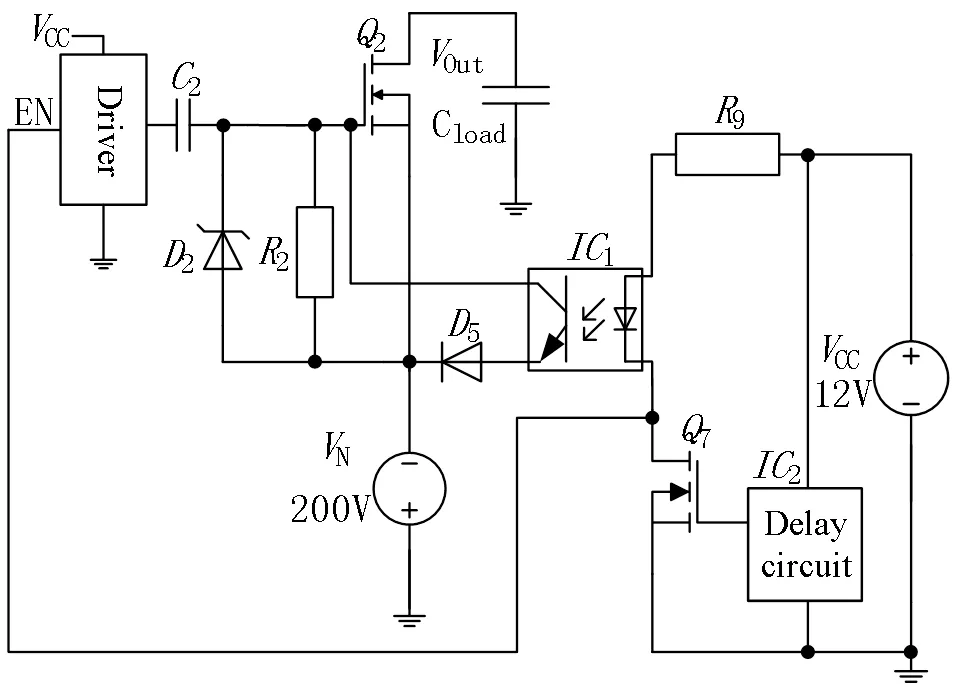

2 电路结构设计

综上设计分析,本文设计的阴极选通模块电路结构如图3所示。

图3 本文设计的电路结构

电路原理:上电过程中,上电时序电路控制驱动器输出恒低,待外围偏置电压完全建立后使能死区时间调整电路响应外部触发信号Trig,得到具有死区时间间隔的SignA和SignB,再分别经低边驱动器加强驱动能力后得到DrivA和DrivB,然后供给正负脉冲电路得到输出。Trig为高时,Out为-200V;Trig为低时,Out为+30V;+30V和-200V由12V dc供电通过DC-DC转换得到。

3 电路设计

重点对正负脉冲电路、全占空比输出维持电路、上电时序电路、死区时间调整电路和驱动器选型进行设计分析。

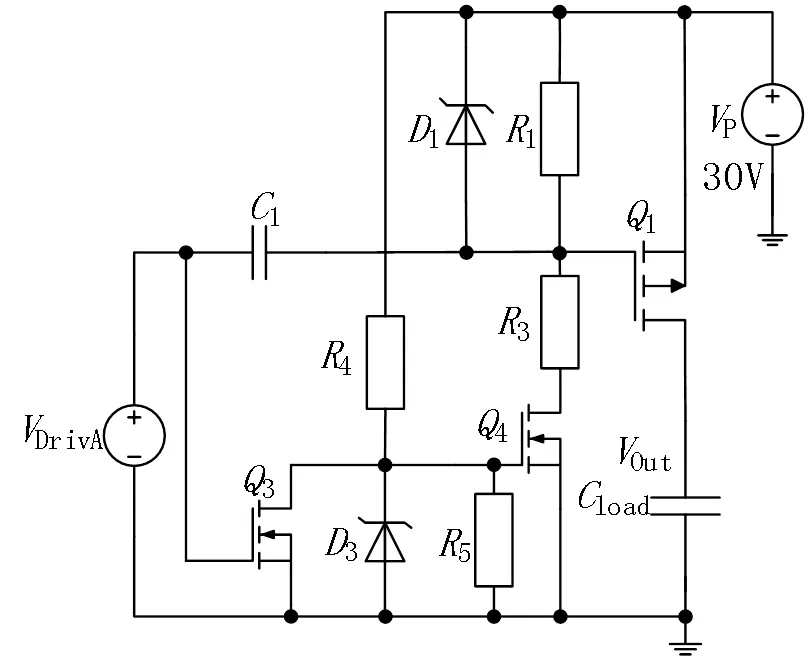

3.1 正负脉冲电路

如图4所示,采用NMOS和PMOS构成CMOS推挽输出结构,由1、1、1和2、2、2构成电压电平转移电路,分别将DrivA和DrivB转移至MOS管G-S级控制互补导通和关断,最终在load两端形成正负脉冲。全占空比输出维持电路实现100%或0%占空比输出,上电时序电路避免开机过程中上、下管短路,具体设计如下所述。

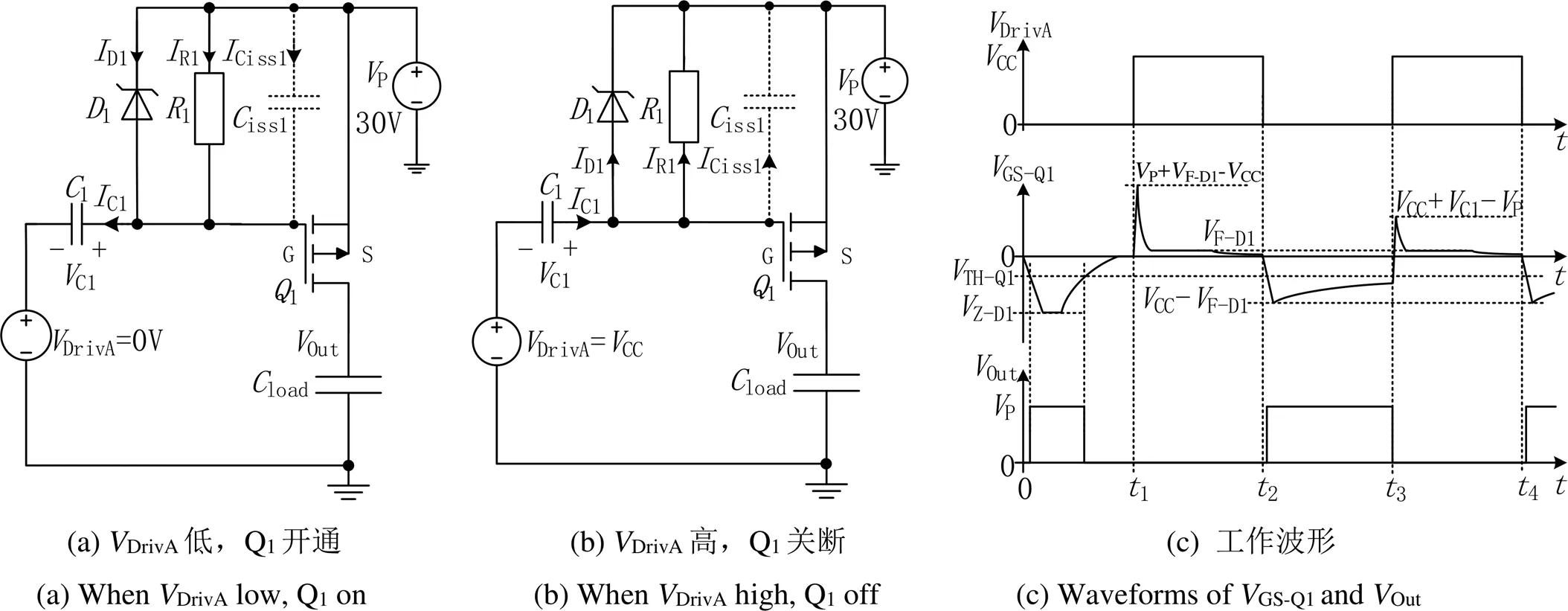

3.1.1 正压脉冲电路设计

正压脉冲电路基于低边驱动器、电压电平转移电路和PMOS设计,为便于分析,假设电路工作在较小的开关频率且CC<Z-D1,工作原理如图5所示。

图4 正负脉冲电路结构

图5 正压脉冲电路原理

0~1时段为上电过程,见图5(a),DrivA=0V,随着P的建立,稳压管1随之导通并对GS-Q1钳位,电容1通过支路电流D1和R1最终被充电至P,上电过程中GS-Q1从0V下降到1稳压值Z-D1后缓慢升高至0V,Q1开通后又关断;

1时刻,见图5(b),DrivA=CC,C1=P,DrivA经过1同1、iss1(Q1内部输入电容)、P分别形成反向D1和Ciss1回路对1快速放电,由于1的正向开通特性,GS-Q1快速从0V上升到约P+F-D1-CC后被1正向导通电压F-D1钳位直至缓慢到0V,C1最终约P-VCC,期间Q1保持关断;

2时刻,见图5(a),DrivA=0V,C1≈P-CC,iss1被快速充电,GS-Q1快速从0V降低至CC,Q1快速导通,之后P通过1对1缓慢充电,G极电压缓慢上升,GS-Q1差值逐渐减小,直到小于开启电压TH-Q1时关断,因此1、1的取值不能太小,否则GS-Q1很快低于TH-Q1不能维持Q1导通,尤其在较小y时Q1将提前关断;合理1、1的取值,保证3时刻|GS-Q1|=P-C1>|TH-Q1|。

3时刻,DrivA=CC,则同1~2时段一样,1和iss1被快速放电,GS-Q1快速从-(P-C1)上升到CC+C1-P后被F-D1钳位又降低为0V,快速关断Q1。

因此,如图5(c)所示,正压脉冲电路控制机理是:DrivA为高电平时,Q1关断;DrivA为低电平时,Q1导通。随着开关频率的提高,1充放电减缓,C1将趋于P-CC+F-D1处轻微波动,GS-Q1波形近似DrivA整体向下偏移CC-F-D1,即1、1和1实现了将DrivA转移至Q1的G-S两极并转换成负压进行开关控制。

3.1.2 负压脉冲电路设计

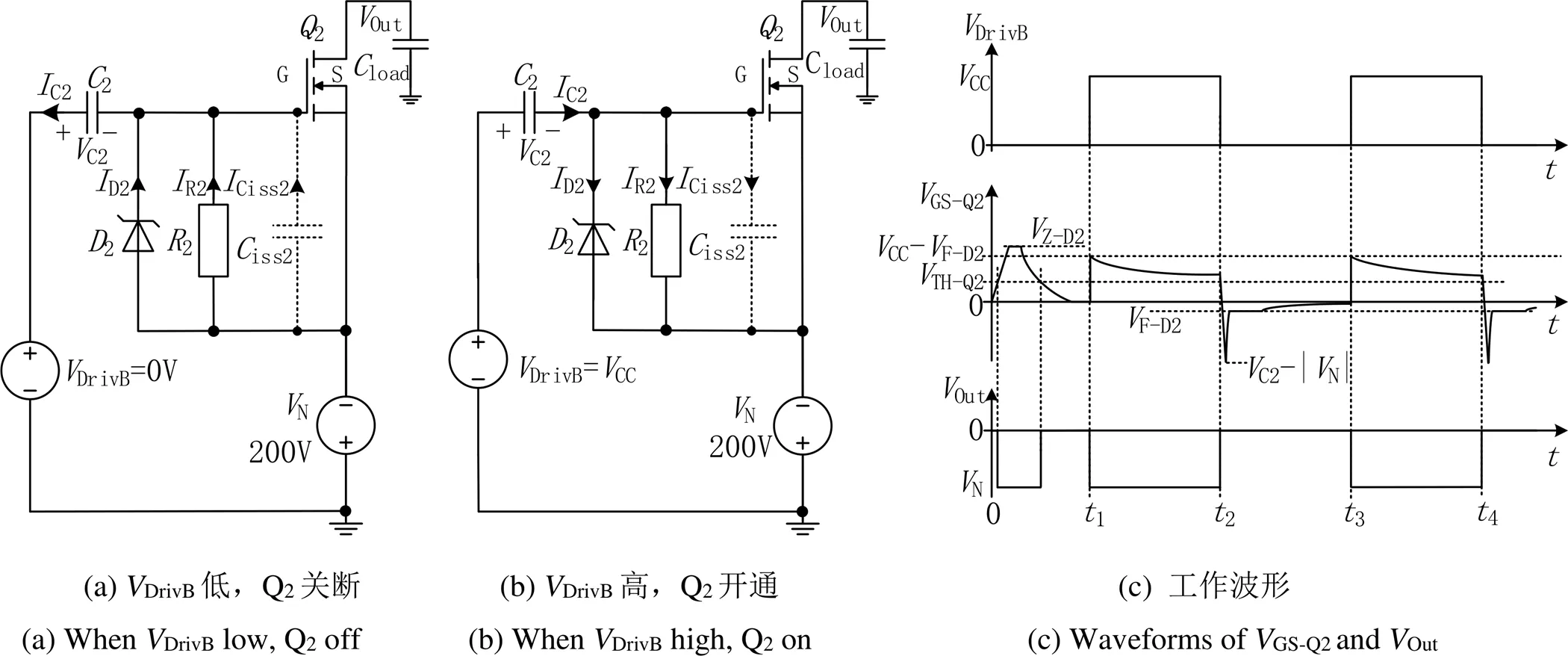

负压脉冲电路基于低边驱动器、电压电平转移电路和NMOS设计,为便于分析,假设电路工作在较小的开关频率且CC<Z-D2,工作原理如图6所示。

图6 负压脉冲电路原理

0~1时段为上电过程,见图6(a),DrivB=0V,随着N的建立,稳压管2随之导通并对GS-Q2钳位,电容2通过支路电流D2和R2最终被缓慢充电至N,上电过程中GS-Q2从0V上升到2稳压值Z-D2后缓慢下降至0V,Q2开通后又关断;

1时刻,见图6(b),DrivB=CC,C2=|N|,DrivB经过2同2、iss2(Q2内部输入电容)、N形成反向D2、Ciss2回路,iss2被迅速充电,GS从0V上升到CC,Q2导通;之后DrivB通过2对2缓慢充电,GS-Q2逐渐降低,直到低于开启电压TH-Q2时关断,因此2、2取值不能太小,否则GS-Q2很快低于TH-Q2不能维持Q2导通,尤其较y时Q2将提前关断;合理2、2的取值,保证2时刻GS-Q2=|N|+CC-C2>TH-Q2。

2时刻,见图6(a),DrivB=0V,同样由于2的正向开通特性,GS-Q2快速从|N|+CC-C2下降到约-(C2-|N|)后被2正向导通电压F-D2钳位直至缓慢到0V,C2最终约|N|,期间Q2保持关断;

3时刻,DrivB=12V,C2=|N|,GS-Q2波形和1~2时段内一样,Q2再次导通。

因此,见图6(c),负压脉冲电路控制机理是:DrivB为高电平时,Q2开通;DrivB为低电平时,Q2关断。随着开关频率的提高,2充放电减缓,C2将趋于|N|+F-D2处轻微波动,GS-Q2波形近似DrivB整体向下偏移F-D2,即2、2和2实现了将DrivB转移至Q2的G-S两极进行开关控制。

3.2 全占空比输出维持电路设计

全占空比条件下,即y为100%或0%时,1、2不能实现电平转移,Q1和Q2将保持关断。设计要求是当y=0%时,Out恒为+30V;y=100%时,Out恒为-200V。如图7所示为y=0%时正压维持输出电路设计,当DrivA为低电平时,Q3关断,Q4导通,Q1导通,控制逻辑同3.1.1所述一致;当DrivA恒低时,Out=+30V,实现正压直通。

图7 Dy=0%时正压输出维持电路设计

图8所示y=100%时负压维持输出电路设计,当DrivB为高时,Q5关断,Q6导通,Q2导通,控制逻辑同3.1.2所述一致。当DrivB恒高时,OUT=-200V,即负压直通。

图8 Dy=100%时负压输出维持电路设计

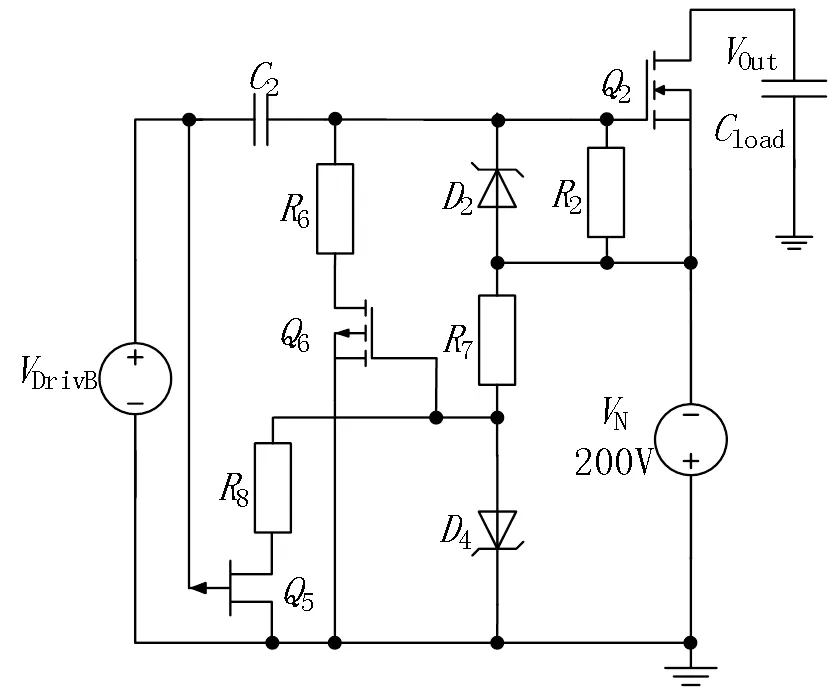

3.3 上电时序电路设计

如3.1分析,正、负脉冲电路在上电过程中Q1、Q2都存在导通后又关断的现象,将导致交叉导通。正压脉冲电路在DrivA恒低时输出正压,可以保护光电阴极,因此只需在上电过程中将驱动器输出置低并锁死关断Q2即可。见图9设计,上电启动2延时电路,延时时间大于N和P建立所需时间,延时期内将驱动器输出使能置低,光耦1将GS-Q2短路,强制关断Q2。

图9 上电时序电路设计

3.4 死区时间调整电路和驱动器设计

死区时间调整在同步整流、正激有源钳位等开关电源中已大量应用,从图5、图6可看出DrivA、DrivB同相,因此选择同相输出的死区时间实现设计。要实现ns级开关速度,关键在于对iss快速充放电,本文设计的优势在于可采用驱动力更强、结构更简单、封装更小的低边驱动器,简化设计并提高了正、负脉冲输出的驱动能力。

4 测试验证

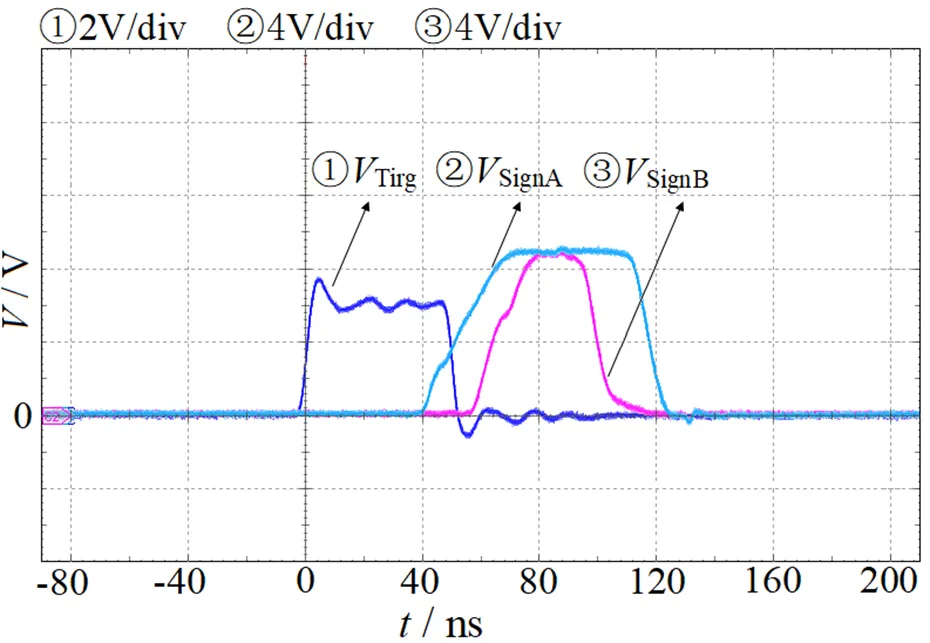

基于上述设计研发了样机,在开关频率sw=200Hz,load=100pF条件下,对关键波形进行测试。见图10,死区时间调整电路将Trig转换为同相信号SignA和SignB。

图10 VSignA、VSignB波形

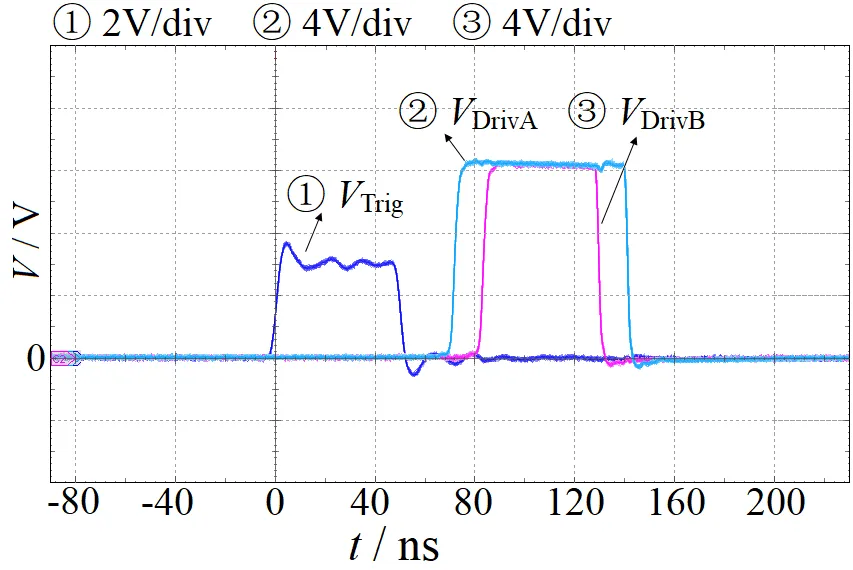

图11为DrivA和DrivB波形,同SignA、SignB波形相近但更快速,上升沿2.2ns,下降沿1.7ns,大幅提高Q1、Q2的开关速度。

图11 VDrivA、VDrivB波形

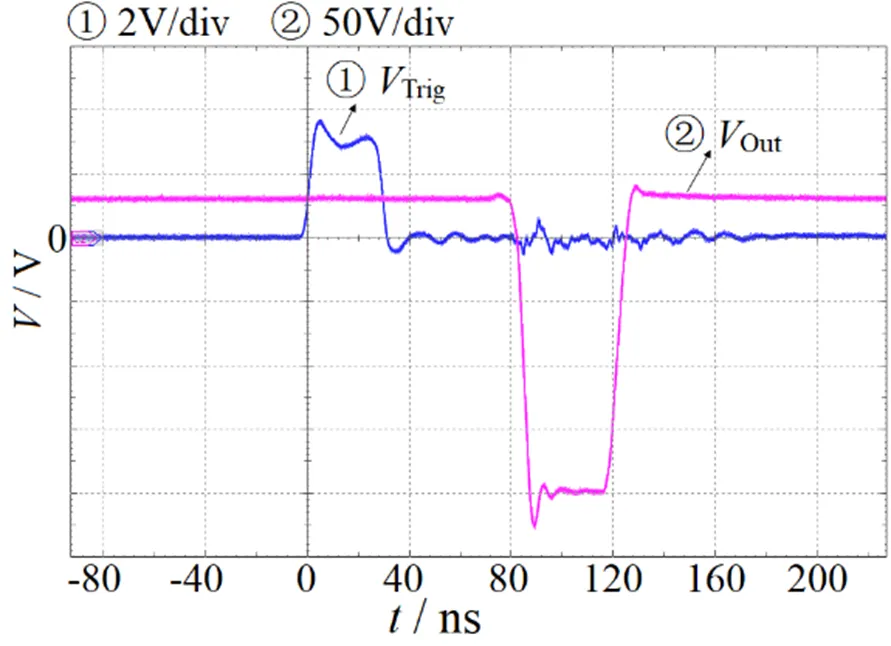

死区时间能够避免交叉导通提高可靠性,保证Out满幅值输出,但会限制最小脉宽,图12为本文设计能够实现的最小脉宽为30ns的Out波形,+30~200V满幅值输出,上升时间7.3ns,下降时间5.2ns,输出延时82ns,实现了ns级上升、下降沿正、负高压脉冲输出。

图12 最小脉宽VOut波形

逐渐降低Trig的脉宽直至28ns,即y≈0%时,上管Q1直通,下管Q2完全关断,Out恒为+30V,见图13所示。

图13 Dy≈0%的VOut波形

逐渐增大Trig的脉宽直至4.999942ms,即y≈100%时,上管Q1完全关断,下管Q2直通,Out恒为-200V,见图14所示,实现了脉冲占空比0%~100%可调。

图14 Dy≈100%时的VOut波形

5 结论

针对微光像增强器高速选通成像应用,本文进行电路建模分析设计要求,提出一种阴极选通模块设计,主体基于CMOS输出结构和电压电平转移电路,该设计能够使用低边驱动器实现ns级正负输出上升、下降沿;外围设计死区时间调整电路、全占空比输出维持电路和上电时序电路,能够避免上、下管交叉导通,实现了0%~100%占空比可调、+30~-200V满幅值输出,实测验证了电路具有结构简单、性能可靠等优点。国外Photek、Photonis公司等已经推出了各种选通模块,以Photek公司GM300-3模块为例对比,本文设计除最小脉宽指标稍低于进口模块外,其余指标均和进口模块相当,可用于相关领域国产化替代。

[1] 汪贵华. 光电子器件[M]. 北京: 国防工业出版社, 2014: 115-118.

WANG Guihua.[M]. Beijing: National defense industry press, 2014: 115-118.

[2] 郭明安, 杨少华, 罗通顶, 等. 用于高速成像的紧凑式像增强选通脉冲发生器[J]. 现代应用物理, 2016, 7(4): 041203.

GUO Ming’an, YANG Shaohua, LUO Tongding, et al. A compact image intensifier gate pulse generator for high speed imaging[J]., 2016, 7(4): 041203.

[3] 虎俊宇, 裴承全, 田进寿, 等. ICCD选通脉冲源的设计与实验研究[J].光子学报, 2018, 47(9): 0911001.

HU Junyu, PEI Chengquan, TIAN Jinshou, et al. Design and experimental study of ICCD gated pulse source[J]., 2018, 47(9): 0911001.

[4] 刘宁文, 畅里华, 肖正飞, 等. 门控型像增强器开门时间测量[J]. 强激光与粒子束, 2012, 24(10): 2447-2450.

LIU Ningwen, CHANG Lihua, XIAO Zhengfei, et al. Measuring gating time of gated image intensifier[J]., 2012, 24(10): 2447-2450

[5] 张昆林. 小型16mm双近贴式像增强器研究[D]. 南京: 南京理工大学, 2008: 40-41.

ZHANG Kunlin. Research on minitype 16mm double-proximity image intensifier[D]. Nanjing: Nanjing University of Science and Technology, 2008: 40-41.

[6] Photek Inc. Photomultiplier & photodiode user guide [R/OL]. www. photek.co.uk, 2016.

[7] Onsemiinc. Design and application guide of bootstrap circuit for high- voltage gate-drive IC [R/OL]. www.Onsemi.com, 2014.

Design of Image Intensifier Photocathode Gating Module

DU Peide,ZHU Wenjin,ZHOU Shengtao,LI Xiaolu,LI Yaqing,CHU Zhujun,YANG Kejie

(North Night Vision Technology Co. Ltd, Kunming 650217, China)

For high-speed imagingframing cameras, nanosecond-level time resolution can be achieved using a photocathode gating module to control the image intensifierphotocathode.Traditional moduleshave some problems, such as slow switching speed, exclusively negative voltage output, and positive or negative voltage outputs that cannot reach the full amplitude. Based on the CMOS push-pull output structure and voltage level transfer circuit, a photocathode gating module was designed, which could usea low-side driverdriving PMOS and NMOS. Dead-time control was used to avoid cross conduction of the upper and lower MOSFETs. The actual test results verified that this module has the advantages of simple structure and reliable performance;moreover,the ns level rising or falling edge, adjustable duty ratio 0 to 100%, and +30 to-200V pulse output amplitude were realized. Thismodule was found to be suitable for gating the photocathode of the image intensifier.

image intensifier, photocathode gating, positive and negative pulse generator

TN22

A

1001-8891(2021)10-1008-06

2020-10-08;

2020-12-04.

杜培德(1986-),男,云南玉溪人,硕士,工程师,主要从事像增强器电源设计。E-mail:541395364@qq.com。