基于FPGA的四象限探测器信号处理板设计

田 静,马 伟,卢晓东

(1.宁夏大学新华学院,宁夏 银川 750021;2.西北工业大学航天学院精确制导与控制研究所,陕西 西安 710072)

1 引 言

现代战争强调精确打击,激光制导武器因具有打击精度高、成本低、抗干扰性能好等优点,成为各国竞相研制的重点技术领域[1-2]。目前激光制导武器中大多采用半主动激光制导方式,其主要由带导引头的弹体、发射平台和激光目标指示器构成[1]。随着技术发展,导引头和激光目标指示器都在不断地朝着通用化、标准化、系列化、小型化及多功能方向发展,对激光半主动导引头提出了新的挑战[2]。导引头的主要功能是精确提取回波信号进行目标位置解算,形成制导指令,导引激光制导武器实现精确打击[3-5],其工作状态直接决定武器系统的精度[6]。在激光通信中,常用的位置敏感器件有位置灵敏探测器(Position Sensitive Detector,PSD)、电荷耦合器件(Charge-coupled Device,CCD)和四象限探测器(Four-quadrant detector,4-QD),PSD简单可靠,但分辨率较低;CCD线性度较好,但驱动电路复杂、信号不连续;四象限探测器[3-4]因体积小、灵敏度高、抗干扰性强成为优选[7]。四象限探测器主要负责搜索和捕获由激光器经目标漫反射后的回波信号,传给后续信号处理电路,进行目标位置解算。

常用的光斑位置解算算法是和差比幅法[3-4],需获取四象限峰值电压信号。由于使用FPGA实现数字寻峰需要采样全波形,对ADC采样率要求较高[8],因此需要实现模拟寻峰。目前实现峰值保持功能有多种电路结构和模块。但存在电路结构复杂、跟随性差、转换速率慢[9]、封装大、成本高、功耗大以及需要辅助电路等不足之处。本设计针对四象限探测器输出信号特点,设计一款基于FPGA的信号处理板,设计核心是峰值检测模块(Peak Detector,PKD),获取信号峰值电压信息,确定光斑中心相对于探测器中心位置的偏移量。

2 电子学设计

2.1 总体结构

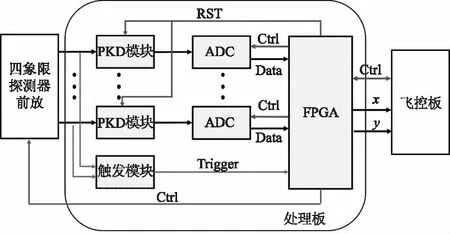

紧靠四象限探测器的前端板,其主要功能是对探测器输出信号进行预处理(电流信号转换成电压信号),且增益可调(两档增益)。针对前端板输出脉冲信号特点(有效周期为20 Hz,有效值为0.1~4 V,标称值为3.7 V,上升沿为200~300 ns,下降沿为2 μs)及导引头小型化需求设计信号处理板,设计指标为:峰值检测偏差<5 %,通道一致性>90 %。

信号处理板的作用是对前端板输出的四路信号进行模拟调理,获取信号峰值信息,解算出目标位置。为了精确获取某一时刻光斑位置,需同时获取四路峰值电压信号[10],即保证采样同步性和增益一致性,可通过“等长布线+四路ADC并行采样+同步触发”来实现。多通道ADC一般有内部同步机制,通道间共用一个采样时钟,因此优先选择双通道或四通道ADC;为了保证增益一致性,四路探测器信号须经过相同的模拟调理电路;ADC采用触发机制,当有触发信号到来时,ADC开始采样,因此需要四路同步触发。

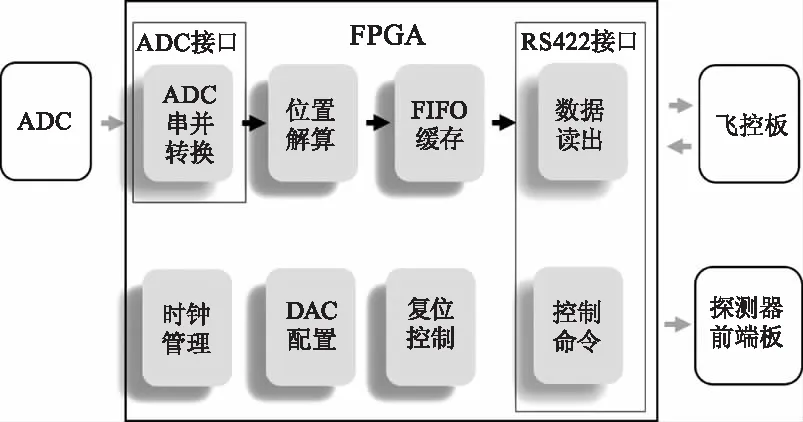

信号处理板整体设计框图如图1所示,以FPGA芯片为主控核心,四象限探测器前端板输出信号经滤波之后,分成两路,一路输入至PKD模块,一路输入至触发模块。PKD模块自动捕获峰值电压并保持。当探测器四路信号累加幅值大于阈值电压时,产生触发信号(Trigger)。触发信号经过FPGA同步、展宽之后,触发ADC开始采样、实现模数变换,取其中前八个采样点求均值作为峰值。最后,根据光斑位置解算算法,计算出光斑中心在x、y方向上的偏移量传输给飞控板。

图1 处理板整体设计框图Fig.1 Design framework of the processing board

当峰值保持时间达到50 μs(假设峰保时间是50 μs)之后,FPGA产生复位信号(RST),使PKD模块复位,形成泄放回路,保持电容放电,在下一个触发信号到来之前,复位信号失效,PKD模块进入自动寻峰模式。复位信号脉宽可根据探测器信号频率、幅值进行调整。在保证峰值保持时间足够的情况下,复位信号宽度越宽越好,最好在下一次脉冲到来之时失效,这样可避免干扰信号等非有效信号引起PKD模块误工作(保持电容充电),致使干扰信号等叠加在有效信号之上,影响测量结果。为了防止噪声等引起误触发,应以最小有效信号为基准设定触发模块阈值电压。

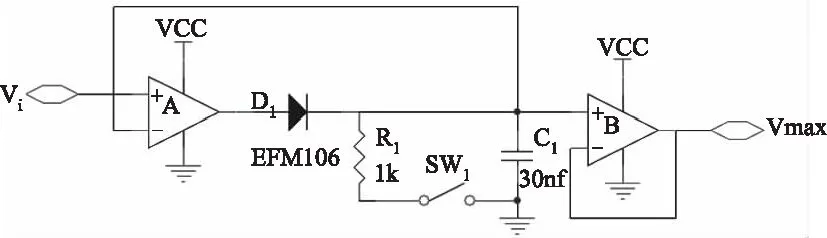

2.2 峰值检测模块(PKD)设计

峰值检测模块的作用是对输入信号的峰值进行提取并保持,主要有电压型和跨导型两种[11]。电压型主要由电压运放、检测二极管、保持电容和电压缓冲器组成[11]。本设计采用电压型方案来实现峰值检测及保持,电路原理如图2所示。经过PSpice仿真,运放选择ADI公司的ADA4891芯片(供电电压2.7 V~5.5 V,双通道、轨对轨),二极管选用EFM106。当输入电压值大于前一时刻输入电压值时,二极管导通,输出电压加在保持电容两端,保持电容迅速充电;当输入电压值小于前一时刻输入电压值时,二极管反向截止,此时保持电容两端电压基本保持不变。即峰值到来之前,二极管导通,保持电容电压跟随输入电压;峰值到来后,二极管截止,保持电容电压维持峰值电压[9,12]。峰值保持50 μs后,复位信号有效,触发模拟开关闭合,形成泄放回路,保持电容电荷完全泄放后变成零电位,等待下一个输入信号到来。模拟开关选择ADI公司的ADG801(0.25 Ω的导通电阻,35 ns导通时间,0.01 μW功耗)。

图2 峰值检测原理图Fig.2 Schematic diagram of peak detector

保持电容的选择至关重要。保持电容需要满足两点要求:绝缘电阻足够大,防止电荷泄漏;介质吸附效应小[11,13]。在高频电路中电容介质吸附效应会影响电容电压上升速度,所以须选择吸附效应小的电容,如聚丙烯薄膜电容(CBB)、聚苯乙烯电容(CB)等。通过PSpice仿真,确定保持电容容值为30 nF,峰值下垂速率约为8 mV/μs。在实际电路调试中,依次将保持电容替换为不同类型不同容值的电容,如1 nF、10 nF、20 nF、30 nF和40 nF的聚丙烯薄膜电容(CBB)、聚苯乙烯电容(CB)进行性能对比,测试结果表明保持电容取聚丙烯薄膜30 nF时保持性能和跟随性能最优,与仿真结果一致。

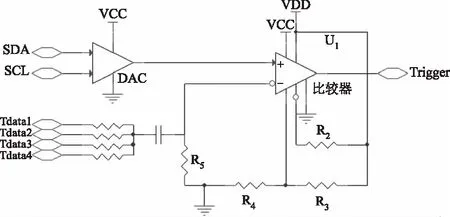

2.3 触发模块设计

在本设计中,利用“DAC+比较器”来产生触发信号,原理如图3所示。以最小信号为基准,通过FPGA配置DAC设定阈值。当四路信号累加幅值大于阈值电压,比较器输出跳变,作为脉冲信号出现的标志信号。DAC选择ADI公司的AD5321芯片(12 bit,2线接口,最高速率400 kHz),由基准电源提供输入参考电压。比较器选用ADI公司的ADCMP602芯片(轨到轨输出,迟滞特性,3.5 ns延迟,10 mW功耗)。在本设计中,不需要精确获取峰值出现时刻,待信号峰值稳定后ADC采样即可。峰值保持时间达到50 μs后,关闭模拟开关,保持电容开始泄放,大约10 ms之后断开模拟开关(脉冲周期为50 ms,因此在下一个脉冲到来之前模拟开关断开即可),等待下一个脉冲信号到来。

图3 触发模块原理图Fig.3 Schematic diagram of trigger module

2.4 FPGA逻辑设计

本设计中的逻辑由硬件语言Verilog HDL实现。在FPGA内,主要实现芯片配置、ADC串并转换、光斑位置解算及数据封装和传输,如图4所示。具体工作流程如下:(1)信号处理板上电后,完成系统初始化(复位、DAC配置、时钟扇出等),进入待机模式;(2)当处理板收到飞控板发来的握手指令后予以应答,进入就绪模式;(3)当处理板接收到飞控板发来的启动命令后进入工作模式对信号进行解码,产生OpenGate信号;(4)当处理板接收到Trigger信号后,触发ADC开始采样;(5)四路ADC数据经串并转换后,利用和差比幅算法解算出偏移量,最后将所有数据封装打包由RS422接口上传至飞控板。当峰值电压接近最大值时,预示着信号即将饱和,处理板经RS422接口发送增益控制信号至探测器前端板。前端板会进一步衰减探测器信号至合适的量程。

图4 FPGA数据处理逻辑框图Fig.4 Block diagram of FPGA data processing logic

3 主要性能测试与讨论

3.1 输入输出特性

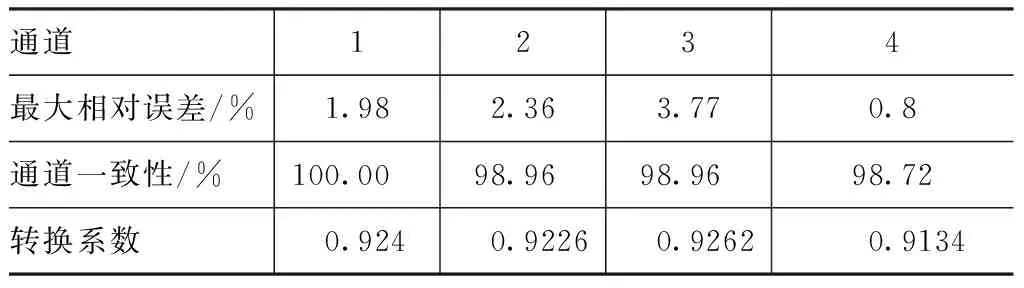

在测试时,信号源脉冲信号经慢成形模块整形为准高斯波形,用来模拟激光器信号,以作为处理板PKD模块的输入信号。PKD模块四通道输入输出特性曲线如图5所示,各通道的转换系数、最大相对误差及通道一致性列于表1。

图5 PKD模块输入输出特性曲线Fig.5 The input-output characteristic curve of PKD

表1 PKD 模块各通道的转换系数、最大相对误差及通道一致性

从测试结果可知,PKD模块四通道输出信号随输入信号呈线性变化,四通道最大相对误差小于4 %,可见各通道峰值保持输出与输入有极好的线性度,且各通道一致性(以通道一为基准)大于98 %。可通过后续标定和多次采样求平均值的方法修正峰值结果。

3.2 性能对比

3.2.1 PKD模块与AD684芯片性能对比

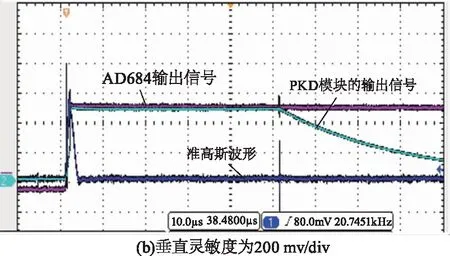

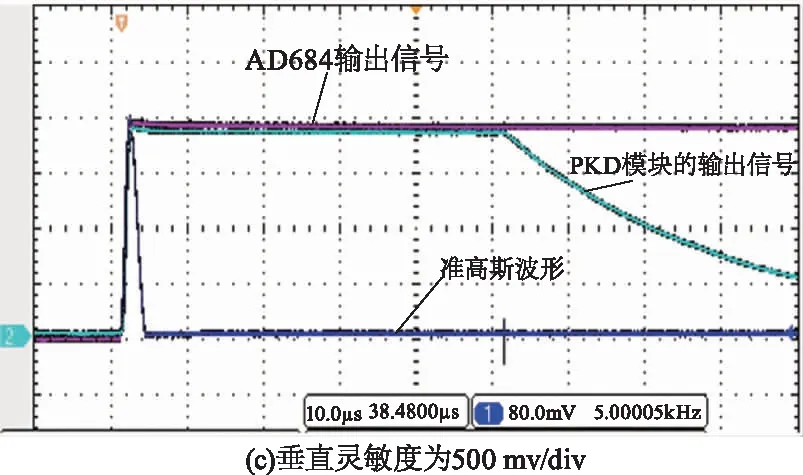

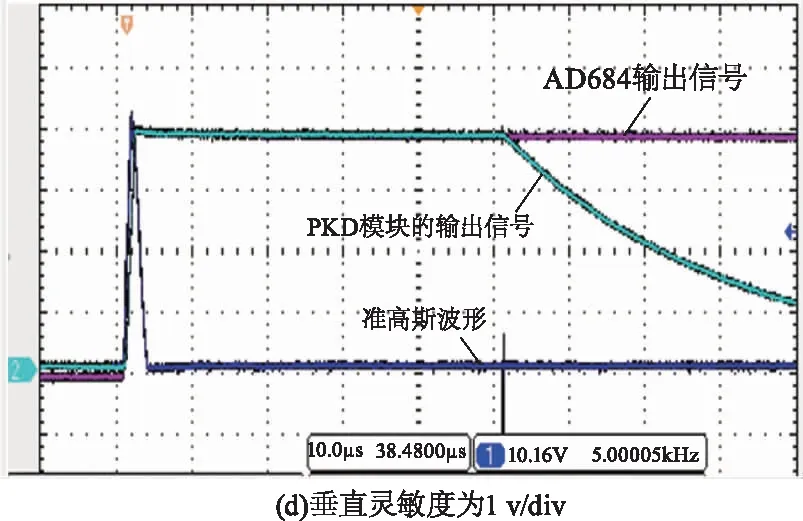

为了定性了解PKD模块性能,将其与ADI公司的采样保持放大器AD684芯片进行性能对比。测试时,信号源脉冲信号经慢成形模块,整形为准高斯波形信号模拟激光器信号,扇出两路分别引入至PKD模块和AD684芯片,观察两者输出的峰值信号。AD684芯片需要外部输入S/H(高电平采样,低电平保持)信号,测试时用信号源另一个通道产生。为了精确捕获峰值,S/H信号下降沿须与输入信号峰值时刻对齐,S/H低电平宽度设为100 μs(即峰值保持时间为100 μs)。图6为PKD模块与AD684芯片性能对比结果,从图中可知,PKD模块峰保持效果与AD684芯片相当,且PKD模块输出噪声更小。其它方面的性能对比如表2所示。

图6 PKD模块与AD684芯片性能对比Fig.6 Performance comparison between PKD and AD684 chip

表2 PKD模块与AD684芯片性能对比

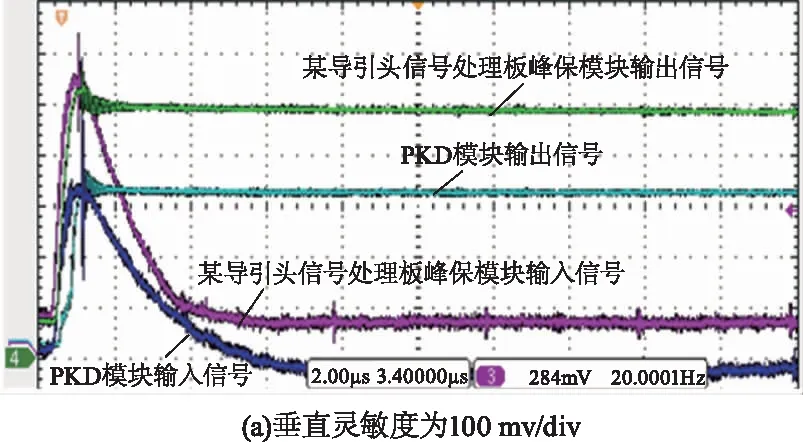

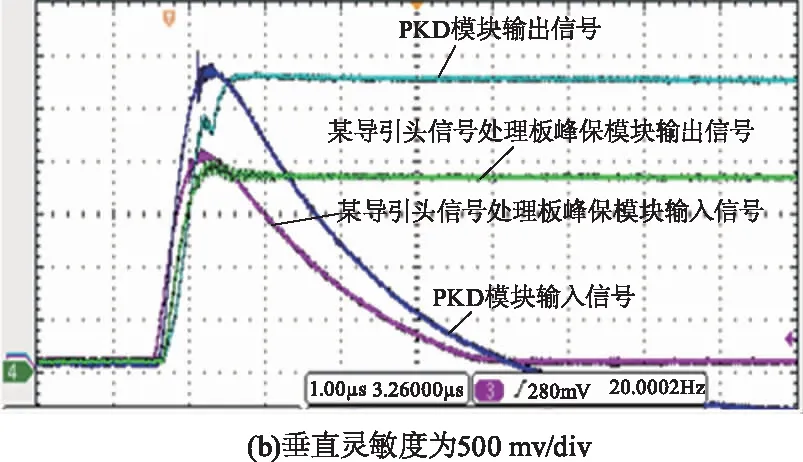

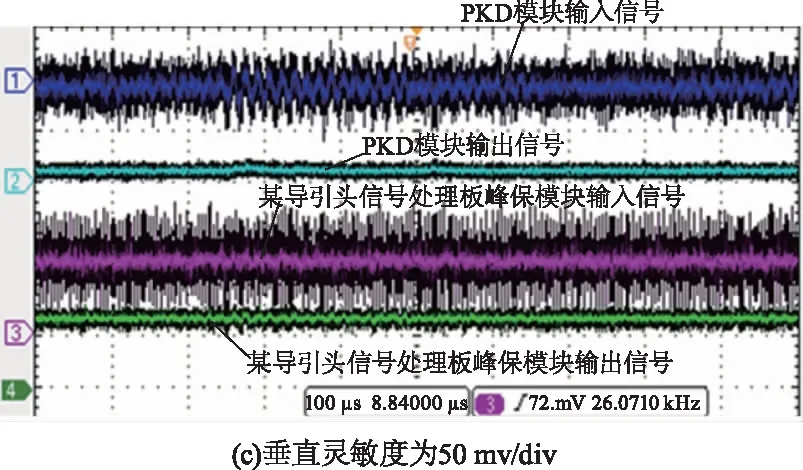

3.2.2 PKD模块与某导引头信号处理板峰检模块性能对比

为了进一步了解PKD模块的性能,将探测器两路输出信号分别引入至PKD模块和某导引头信号处理板峰检模块(峰保持时间为100 μs),观察两峰检模块保持性能。从图7(a)、(b)可知,两峰检测模块输出峰值信号相对于原始信号峰值都有一定下降,但PKD模块峰值信号下降值更少,即更接近于真实峰值;从图7(c)可知,两峰检测模块的噪声均小于原始输入噪声,表明两者均能有效滤除大部分高频噪声,改善系统电子学性能。

图7 PKD模块与某导引头信号处理板峰检测模块性能对比Fig.7 Performance comparison between the PKD and the peakdetector of the signal board of seeker

3.3 角分辨率测试

将探测器、前端板和处理板安装在导引头机械外壳中,固定在转台上。利用小型激光器做光源,将激光器在反射平板上的光点对准导引头中心点。由于导引头未进行光学联调,且光源到导引头的距离只有2~3 m,因此本次测试只能定性观察处理板的稳定性和角分辨能力。

首先,通过调整转台的俯仰、偏航和滚转三个角度,找到x、y方向偏移量为0的位置,即中心位置;继续调整转台角度,找到象限位置。接着,从中心位置开始以1°或0.5°为单位逐渐增加方位角,观察x、y方向的偏移量,一直增加至10°,再开始回退,以1°或0.5°为单位逐渐减小方位角。通过该测试,可同时观察处理板的角分辨能力和稳定性。从图8可知,处理板稳定性较好,最小可分辨0.5°的偏转。

图8 角分辨率定性测试Fig.8 The test of angular resolution

4 结 论

本文介绍了一款基于FPGA芯片自主设计的四象限探测器信号处理板,其核心是PKD模块。经电子学测试,四通道峰保持输出与输入具有极好的线性关系,最大相对误差小于4 %,通道一致性大于98 %,满足四象限探测器前端板读出电子学设计需求。与其它两款峰检测模块进行性能对比,发现本PKD模块性能良好:单电源供电(+5 V)、量程为100 mV~4 V、低噪声、低功耗、低成本、自动寻峰并保持、通道数可扩展、峰保持时间可调,初步测试角分辨率为0.5°,表明该设计合理。对于更窄的脉冲,一方面可以调整保持电容和泄放电阻的参数,另一方面也可在PKD模块前加一级慢成形电路。利用慢成形电路可将过窄的脉冲波形整形为百纳秒量级准高斯波形,降低后续电路的设计难度。为了简化设计,可用有源滤波器替换无源CR-(RC)n滤波成形电路,用较少的元件实现更多的积分,使输出波形更接近高斯波形;可获得共轭复数极点,改善滤波成形电路的性能[14]。