锁相红外热成像与FIB在失效分析中的联用

黎恩良,阮泳嘉,李洁森,夏星贤,陈选龙

(工业和信息化部电子第五研究所,广东 广州 511370)

0 引言

随着集成电路制造业的不断发展,器件特征尺寸进入纳米范围,芯片失效分析技术需要与时俱进,随着器件尺寸和芯片线宽的急剧减小,对这些失效的准确定位和机理分析变得越来越困难。失效分析需诊断出失效机理,集成电路失效机理有过电应力、静电放电、固有缺陷、栅氧化层击穿、金属桥连、通孔开路和PN结损伤等[1-2]。

集成电路失效有一部分会导致局部放热,例如:短路、高电阻开路、结击穿和介电泄漏等,针对这些以异常热区为特征的缺陷等[3],多种热成像技术已被开发,例如:红外热成像(IRT)、液晶热成像(LCT)和荧光热成像(FMT)等。这些技术都能够快捷地获取器件表面的温度分布图像,展现芯片质量的整体概况,并能清晰显示出热斑的分布位置。而失效点通常就在热斑部位附近,这样就可以准确定位失效点[2,4]。

传统红外热成像由于采取稳态的加热方式,热斑会扩大,使得定位精度偏低,而基于锁相红外测温原理的显微红外热成像技术因为采用锁相放大技术,大大地提高了信噪比,从而具备微米级的空间分辨力,可定位尺寸较小的热点。除了可以观察器件表面的温度分布情况,还能够得到更多的温度深度信息。另外,红外测温属于非接触测温,不会影响器件的工作状态,可以测量器件真实工作条件下的温度特性[5],因此通过观察、分析电路热像变化可以探测和定位电路故障。

根据锁相红外测温原理,锁相显微红外热成像技术可以定位热斑,从而定位失效点。要想直观观察失效点形貌,可以对芯片进行去层处理。去层是用氢氟酸缓冲液或者平面研磨技术对芯片介质层进行腐蚀,对于金属化层或多晶硅电阻等被介质层包裹的结构,介质层被腐蚀后,被包裹的结构会掉落,无法观察形貌,且化学处理也会腐蚀层间介质。而采用剖面分析不会破坏失效点形貌,这就需要采用聚焦离子束(FIB:Focus Ion Beam)系统进行制样。热点较小时,FIB可在纳米级分辨本领的图像中,对样品的热点进行精确剖切。

本文将介绍锁相显微红外热像技术的原理、思路,通过对引脚间阻值异常和漏电流偏大的集成电路进行失效分析,利用锁相显微红外热成像技术进行失效定位,并采用FIB系统观察剖面形貌,寻找失效点,研究联用方法对多晶硅烧毁或层间击穿引起功能故障的失效分析的有效性。

1 锁相显微红外热成像与FIB系统联用技术介绍

1.1 锁相显微红外热成像技术

显微红外热成像测温原理是普朗克黑体辐射定律。物体表面的红外辐射能,其强度峰值对应的波长与温度有关,用红外探头测量红外辐射能峰值的波长,得到物体表面各点的温度分布状况,并转换为直观的热分布图像[6-7]。

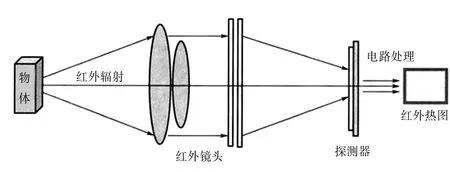

显微红外热像仪利用显微镜技术将物体表面各点的热辐射(远红外区)会聚至红外焦平面阵列检测器,并由计算机转换为伪彩色图像。根据图像的颜色分布来显示样品表面各点的温度分布,如图1所示[6]。

图1 工作原理图

显微红外热成像技术是对微小的电子元器件进行高精度,非接触的测温方法,能显示出器件的异常热区,暴露出芯片烧毁点和工艺缺陷等。集成电路中许多类型缺陷在特定电应力下产生漏电,并伴随电子跃迁而导致光辐射,这样发光点的位置或附近就是失效点[7]。通常高电场区(如栅氧化层和PN结)的漏电流会通过载流子的再结合引起光子发射;金属互连线间的漏电会发热引起红外光发射或等离子体发光;连线接触不良或短路会导致MOS晶体管的热电子发射。显微红外热像仪探测芯片表面缺陷或烧毁导致的光辐射并在图像中反映出来[8]。

热斑尺寸较大时,显微红外热成像技术可以很好地把温度信息提取出来;但如果热斑尺寸很小,对温度分布影响很微弱,则会被直流信号、噪声信号等干扰,信噪比很低,需采用锁相红外热成像。锁相红外热成像是一种对待测物体施加周期性调制热激励的热成像技术,通过运用各手段对噪声信号进行抑制,提取单频信号。锁相的目的是锁定样品红外辐射的幅值、相位信息,将这个微弱信号从众多干扰信号中提取出来[9-10]。

尽管热点很可能就意味着失效点,但不一定百分百就是失效点。例如:CMOS电路金属化之间的短路可能不会产生可见热点,但由于其短路会使某个晶体管产生额外的电流而出现热点,这时,热点部位并不是失效部位。另外,如果测试电路存在异常,也会使好的器件出现大电流区域而产生热点。因此,需要通过其他失效分析手段来验证热点是否是真正的失效点[2]。

1.2 FIB系统制样技术

FIB是利用电磁透镜将离子束聚焦成微小尺寸进行显微精细切割的仪器,它将液态金属离子源(LMIS) (大多数FIB采用镓Ga)产生的离子束通过离子枪加速聚焦后,对样品表面特定区域轰击,进行剖面切割,并采集照射于样品表面所产生的二次电子信号形成电子像,对局部区域进行放大成像。FIB主要类型有单束和双束两种,其中双束FIB既有离子束也有电子束,电子束成像的分辨本领为1 nm以下,可以边剖切边观察。FIB可用于分析芯片内部器件烧毁形貌,比如层间击穿或多晶硅电阻烧毁。定位到热点后,芯片结构导致无法通过化学方法去层进行观察时,需要使用FIB进行垂直剖面分析。

1.3 锁相显微红外热成像与FIB系统联用技术

集成电路的某些失效机理,比如静电击穿、过压击穿和高电阻开路等产生的热点空间尺寸很小,可达亚微米级的微小尺度。锁相红外热成像技术可进行微米级空间分辨本领的定位,分辨本领取决于采用的不同镜头,其中最高的可达2.7μm左右,但对于亚微米尺寸的热点,定位会有非常大的误差。

联用FIB可以弥补锁相红外热成像分辨本领不足的缺点,方法是先从离热点有一定距离的安全区域开始剖切,剖切后用小束流朝着热点出现方向边推进边观察,寻找热点呈现的失效形貌。寻找到失效点后,可用更小束流进行缓慢的推进,分析热点完整的失效形貌。FIB离子束推进的精度可达纳米级,用此联用技术可以把定位精度从微米级提高到纳米级,观察完整的失效点形貌,同时避免化学处理对结构的破坏。

2 失效分析案例研究

2.1 多晶硅电阻烧毁

失效样品为均衡器,其在使用较长的输入线缆连接时失效,检查发现其差分输入端与电源之间的电阻值异常增大。为了定位样品失效区域,开封样品后,用探针对芯片铝PAD进行阻抗测试,确认电阻增大与芯片相关。

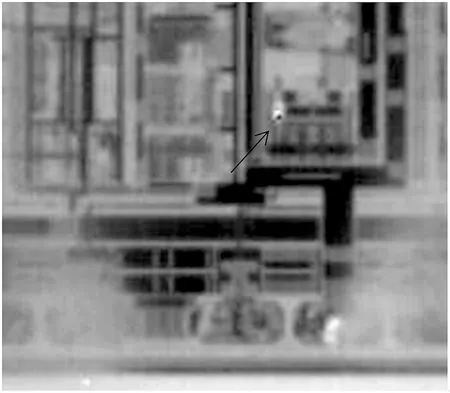

为了确定样品端口间电阻增大的相应位置,对失效样品芯片进行锁相红外热成像分析。当对阻值增大的端口加电压时,可见芯片输入端终端电阻位置存在热点,如图2-3所示。

图2 失效样品热点红外热成像叠加图(一)

图3 失效样品热点红外热成像叠加图(二)

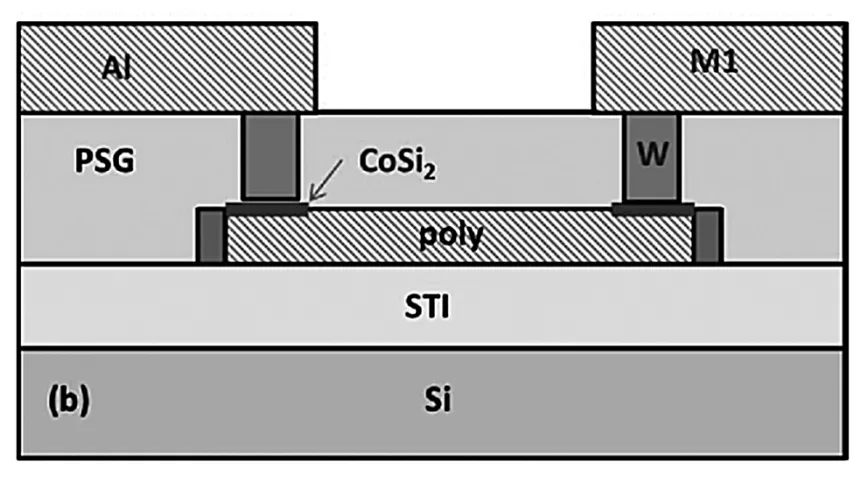

样品芯片结构示意图如图4所示[11],从图4中可见多晶硅电阻被磷硅玻璃(PSG)介质层包裹着,如果用氢氟酸进行去层处理,则介质层会被腐蚀掉,多晶硅电阻会掉落。因此选用FIB进行剖面观察。

图4 芯片结构示意图

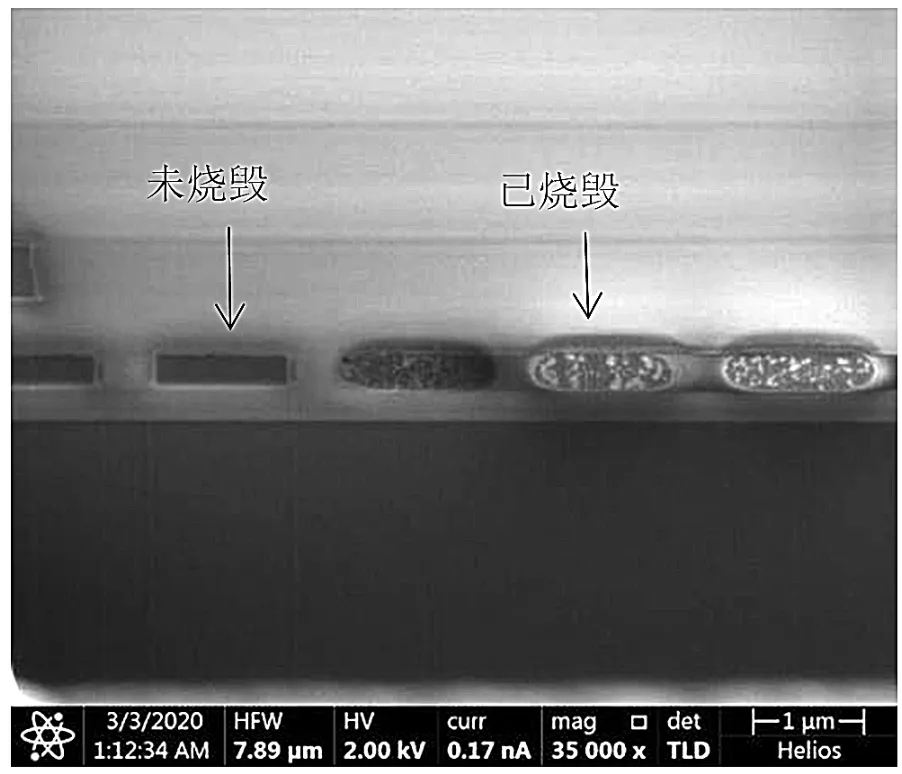

使用FIB从离电阻有一定距离的位置开始剖切,朝着热点方向推进。剖面观察发现多晶硅电阻中心部分的电阻条烧毁,膨胀为不规则形状,边缘部分的电阻条则未见明显烧毁,如图5-6所示。

图5 多晶硅电阻形貌

图6 多晶硅电阻烧毁形貌对比

综合失效形貌及背景信息分析结果得知,失效样品输入端终端电阻烧毁导致阻值增大而使其在长线缆输入时由于阻抗不匹配而失效,终端电阻烧毁的原因是输入端引入了过高的电压。

2.2 静电击穿

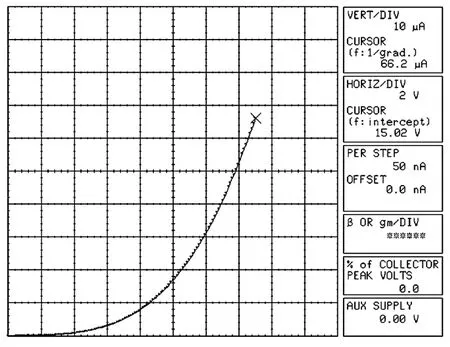

某型号塑料封装N沟道增强型MOSFET使用在BOOST电路中,MOSFET随整机进行40°C带载老化后出现失效,表现为G-S极之间阻抗异常。

为了确定失效样品的失效特性,鉴别失效模式,利用图示仪对失效样品的I-V特性进行测试,显示样品在G-S极之间表现为正、反向的漏电流IGSS值异常偏大,在15 V以内已远远超过规格书要求的最大值250 nA,如图7所示。D-S极之间的漏电流值和击穿电压值均满足规格书的要求。

图7 失效样品的IGSS+测试曲线

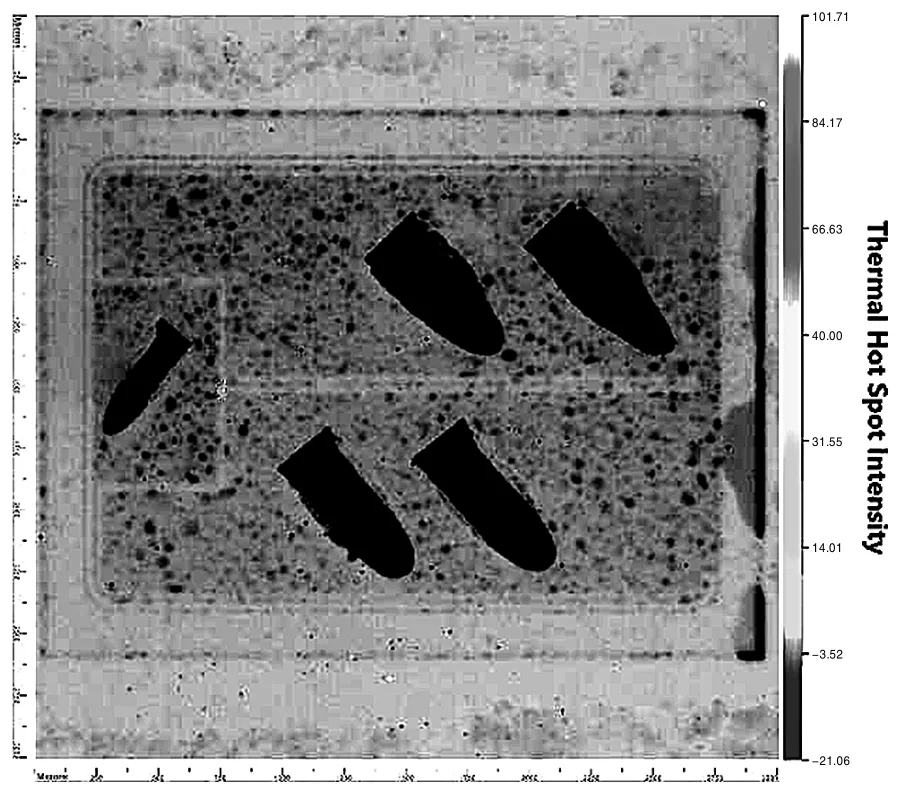

为了确认样品G-S极之间漏电的具体位置,采用锁相红外热成像方法对样品进行分析,给G-S极之间加15 V直流,探测芯片区域是否有集中热点。结果显示样品有热点,大致位于栅极PAD与源极金属化之间的绝缘凹槽拐角区域上,热点定位叠加图显示该位置漏电产生集中热点,如图8所示。

图8 热点定位叠加图

样品G-S极之间漏电,D-S之间不漏电,说明失效点很可能不在有源硅层上,而是在硅层上方的栅极多晶硅层和介质层上。热点位置也不在有源区域,更可能为层间击穿,而化学去层处理容易腐蚀层间介质,因此选用FIB进行剖面观察。

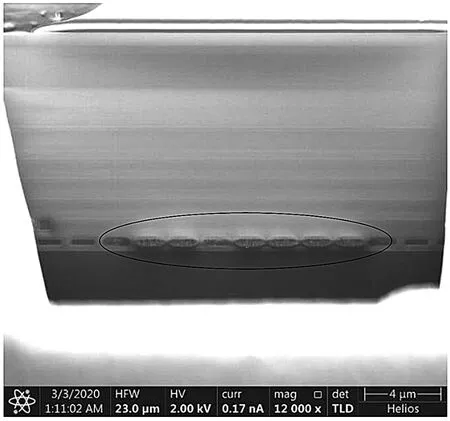

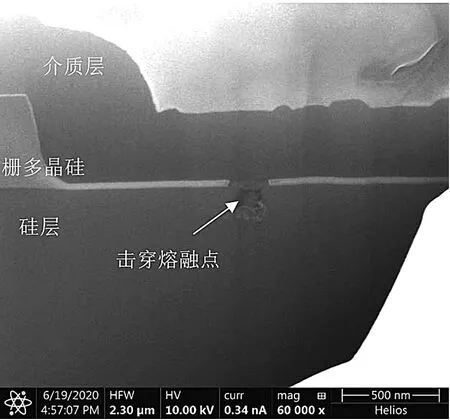

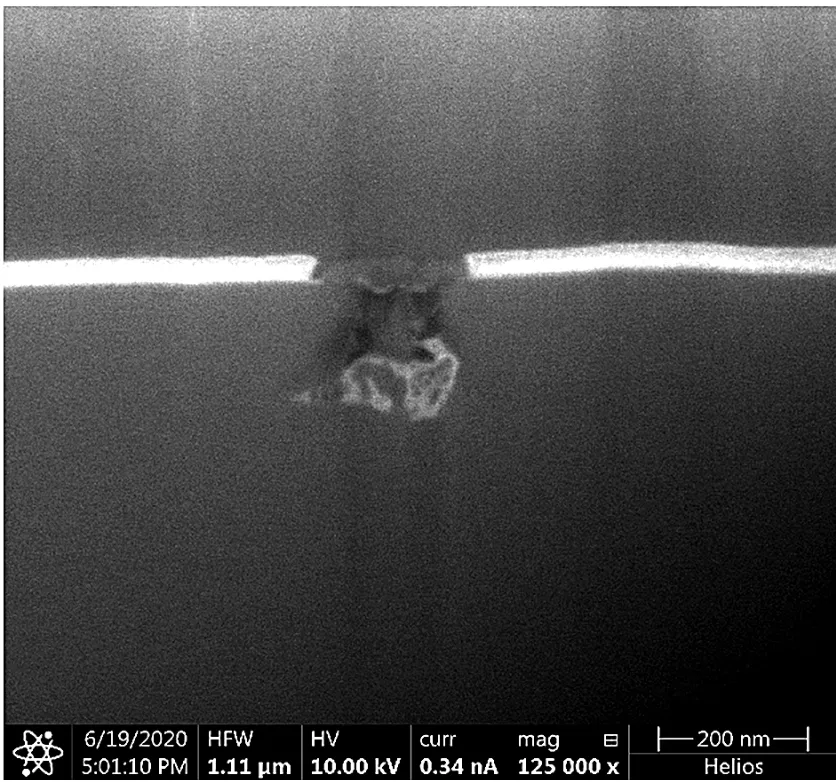

使用FIB从附近区域剖切朝着热点方向推进,观察定位点位置的芯片剖面形貌,结果显示栅极多晶硅与下方硅层结构之间有击穿熔融点,形貌尺寸很小,符合静电击穿的形貌特征,如图9-10所示。综合失效形貌及背景信息分析结果可得,样品是由于栅极静电击穿导致失效。

图9 热点位置的FIB剖面结构形貌

图10 栅极击穿熔融点形貌

3 结束语

锁相显微红外热成像是集成电路失效定位的一种有效方法,可用来定位集成电路的漏电、缺陷和烧毁点。定位到热点后,要用其他分析手段来验证热点是否是真正的失效点。对于去层处理会破坏失效点的芯片结构,要使用FIB系统,分析对比器件的烧毁形貌。热点较小时,锁相显微红外热成像定位有一定的误差,联用FIB系统剖切可精确地寻找到失效点。分析结果表明,锁相显微红外热成像与FIB的联用技术可用于集成电路多晶硅电阻烧毁或层间击穿引起功能故障的失效分析,解决热点定位误差和化学处理破坏结构的难题。