封装设计中辐射EMI产生机理及其抑制方法综述

孙明辉,王剑峰,王波

(中国电子科技集团公司第五十八研究所,江苏 无锡 214035)

0 引言

集成电路工艺进步和设计技术发展促使芯片功能日益复杂,集成度越来越高[1]。在高速数字系统中,电磁干扰(EMI:Electromagnetic Interference)和信号完整性及电源完整性密切相关,相互影响,如:信号过孔穿过参考平面时不仅会引起高速信号边沿的畸变和退化,而且有可能由于阻抗突变和回路面积增大向电源/地平面注入足够能量从而产生谐振[2],引起较大的EMI。在芯片封装时减小EMI噪声,可以极大地减轻后续PCB级和整机的电磁兼容(EMC:Electromagnetic Compatibility)设计压力,从而大幅度地缩短研发周期和降低成本,因此,EMI问题在封装设计中不可忽视。然而,随着芯片集成度越来越高,尺寸日益减小,功能越来越复杂,元器件数目越来越多,芯片封装设计面临着严峻的EMC挑战。

本文对在芯片封装设计中存在的辐射EMI问题和应对方法进行了分析与总结,对于今后在封装设计中减小辐射EMI,保证芯片信号完整性有一定的指导意义。

1 辐射EMI的产生机理

在电子系统中,所有引起电磁场变化的因素或电磁场未得到有效控制之处都会导致辐射EMI的产生,如:接插件、过孔和通信接口等。辐射EMI有电场辐射和磁场辐射两种形式,其中以电场辐射为主,而电场辐射按照辐射产生的原理不同又分为共模辐射和差模辐射。

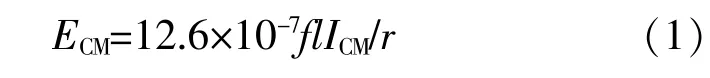

1.1 共模辐射原理

共模辐射产生的主要原因是导线接地不良和接地引起的反射电位[3]。共模辐射噪声在电路中是由导线两端不可控的电压降产生的。在图1中,高频传输电流ICM在流经接地阻抗时,在接地系统中产生了压降,当有导线与这个系统相连接时,会形成电磁场,产生共模辐射。

图1共模辐射示意图

图1 所示的是常见的辐射EMI共模形式。辐射频率仅与导线是否连接到系统有关,与导线本身无关,也与系统的原始信号频率无关。共模辐射可以理解为由地电压驱动的偶极或单极天线。

对于一个长度为l的短偶极子天线,离辐射源距离为r处的远场中测得电场强度的幅度为:

式(1)中:f——信号频率;

l——辐射导线长度;

r——测试距离。

由于噪声频率不能被预测和控制,并且系统的天线长度不能轻易地改变,因此,减小共模辐射噪声最基本的方法是限制共模电流ICM。

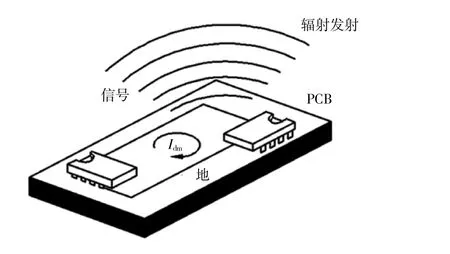

1.2 差模辐射

如图2所示,高频传输电流IDM及其回流构成了一对差分电流路径,而其物理传输路径形成了一个电流环,其面积为A。这种信号回路不能很好地控制干扰电流而形成了差模辐射[4]。

图2 差模辐射示意图

由此产生的差模辐射电场强度为:

式(2)中:f——差模辐射噪声频率;

r——天线在远场中的测试距离。

相对于共模辐射而言,差模辐射在能够明确来源的情况下,通过控制其信号回流环路的面积可以有效地控制差模辐射强度[5],而共模辐射不容易控制,因此,辐射EMI以共模辐射为主。

2 封装设计中辐射EMI的产生原因

在封装设计中,任何非理想互连结构(键合线、信号过孔和参考平面不完整等)在高速信号或噪声传输时都极易引起辐射EMI问题,例如:走线、接插件和键合线等在1/4波长的尺寸下可能产生天线效应,成为辐射源。

在封装设计中常见的EMI产生原因有以下几种。

2.1 差分信号转化为共模信号

在差分线的传输中,所有的信息都由差分信号来传送,因此保持差分信号的质量非常重要。而差分的对称性是保持差分信号质量的关键因素,任何不对称因素都会使差分信号转化为共模信号,从而产生EMI。

差分不对称的情况主要有以下3种。

a)差分驱动器跳变错位[6]

当两个差分驱动器跳变发生错位时,差分信号产生失真现象,对共模信号产生影响。如图3所示,当错位从上升边沿的20%跳变到两倍时,差分信号边沿变缓,上升时间明显地变长,差分信号传输产生时延差,破坏了差分信号的对称性,此时差分信号转化为了共模信号[7]。

图3 驱动器跳变错位时信号波形

b)差分线长度不对称

如果差分线走线长度不相等,差分线信号之间不对称,就会导致信号传输的时延差从而引起差分信号转化为共模信号。

根据经验法则,当走线长度偏差超过上升沿空间延伸的10%时[8],产生的共模噪声就会造成严重的信号完整性问题。因此,为了将时延差保持在上升时间的10%以内,要求长度偏差在上升沿空间延拓的10%以内,即:

式(3)中:ΔL——使时延差保持在上升时间的10%以内时,两条走线之间的最大长度偏差;

Rt——信号的上升时间;

v——差分信号的传播速度。

c)负载不对称

在高速信号中,当某些因素影响了差分对的一条走线而未影响另一条时,即出现负载不对称的情况,那么差分线也会产生失真,引起共模辐射。例如:一条走线遇到了一个测试焊盘而产生了容性负载,但另一条没有,那么差分信号就会失真,对共模信号造成显著的影响,产生辐射EMI[9]。

2.2 键合线引起串联谐振

在封装过程中,当键合引线较长时,其阻抗处处不连续,难以传输高速信号;然而,当其承担电源互连或地互连的作用时,容易引起串联谐振,产生EMI噪声。因此,键合引线作为一种阻抗不可控的互连结构,容易引起辐射EMI的产生。

图4 键合引线图

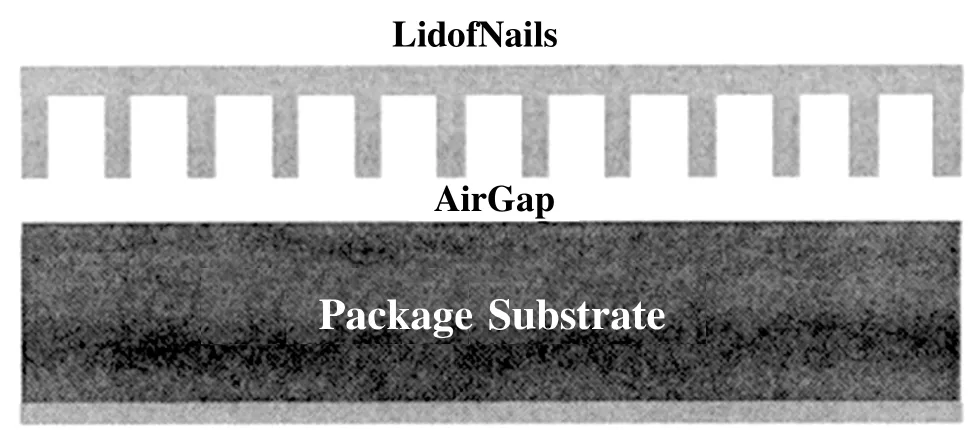

2.3 封装盖板引起的EMI

封装中的盖板起到散热和保护芯片的作用。但是,当盖板距离芯片很近时(目前封装模型中约为0.2 mm),部分共模噪声电流会耦合到盖板的内表面,成为新的辐射源,如图5所示。同时,封装盖板和封装基板之间会形成谐振腔,当噪声频率或它的倍频和固有谐振频率一致时,辐射电场就会大幅度地增强。

图5 封装盖板的辐射EMI模型

2.4 芯片的电磁耦合问题

随着封装技术的发展,三维堆叠封装已被广泛地使用,三维封装的一个重要意义就是缩小封装体积,增加集成度,为了控制整体封装的高度,芯片都被减得很薄,芯片间的电感性耦合问题更加严重。对于集成了数字电路和射频/模拟等敏感电路的混合信号三维堆叠封装来说,EMI的耦合途径除了从PDN中传播的传导性耦合外,芯片之间的近场辐射耦合也会很严重。如图6所示,芯片间的近场辐射耦合主要为芯片电流环路之间的电感性耦合。电感性耦合也被称为磁耦合,当干扰源是以电流形式出现时,此电流所产生的磁场会通过互感耦合对邻近信号形成干扰。噪声耦合幅度不仅与数字芯片、敏感芯片晶体管等效电流回路的相对位置,以及形状和大小有关,噪声源的幅度等因素也会影响噪声耦合幅度。

图6 传统三维芯片堆叠示意图

3 封装设计中辐射EMI抑制方法

对于封装设计中的辐射EMI问题,现有的抑制方法主要集中在屏蔽、滤波和结构改善等方面。针对上述分析的封装设计中常见的辐射EMI问题,国内外主要研究的抑制方案如下所述。

3.1 差分信号中共模电流抑制

针对差分信号转化为共模信号引起的辐射EMI问题,大量研究学者对其进行了探索,其中,研究的抑制方法主要有补偿电容和共模滤波器。

3.1.1 补偿电容

差分线的线长不对称造成的时延差,实质上就是两条走线拐角处的内部结构发生了改变,即电容和电感发生了变化。因此,可以在走线拐角处增加补偿电容[10]来减小差分信号间的时延差,模型如图7所示。

图7 补偿电容的模型

通过对差分线对拐角的模型分析,可推导得出补偿电容C0的表达式为:

式(4)中:Zodd——差分线的奇模阻抗;

L13、L24——45°拐角的差分传输线的近似集总等效电路模型[7]中的耦合电感;

C11、C22——45°拐角的差分传输线的近似集总等效电路模型中的对地电容。

3.1.2 共模滤波器

针对共模信号产生的共模辐射,可以运用共模滤波器将其抑制。共模滤波器不仅可以维持差分信号足够的完整性,而且对共模噪声呈现带阻特性。台湾交通大学吴宗霖科研团队曾提出一款基于缺陷地结构(DGS:Defected Ground Structure)的宽带共模滤波器,其结构示意图如图8所示,该共模滤波器通过在地平面刻蚀U型和H型图案,实现了3.1~9 GHz的共模抑制。然而,类似的共模滤波器的工作原理是基于反射共模信号,有可能造成源端的EMI问题。此外,DGS自身存在辐射增强的风险。为此,研究团队在2015年设计了一种无反射共模噪声吸收型电路,该电路在4~14 GHz频段内实现了80%的共模吸收[10]。

图8 基于缺陷地结构的共模滤波器结构示意图

除此之外,抑制共模辐射还可以采用以下方法:1)使差分线尽量地对称;2)使用可控差分阻抗;3)使差分对的突变最小化;4)在远端端接差分信号等。

3.2 键合线引起的EMI抑制方案

针对键合线引起的EMI,现有的国内外研究主要集中于异质系统集成的全新键合互连结构和新型同轴芯片互连系统这两种方法。

3.2.1 异质系统集成的全新键合互连结构

如图9所示,这是我国台湾新竹交通大学研究的一种应用于异质系统集成的全新键合互连结构,该结构基于史密斯圆图和阻抗匹配理论,有效地减小了键合线的寄生电感,实现了从直流到84 GHz内插入损耗大于-3 dB,反射小于-13.5 dB的信号传输。

图9 异质系统集成的全新键合线互连结构示意图

3.2.2 新型同轴芯片互连系统

除了设计匹配的互连结构之外,部分研究学者着手研究了新型互连方式用于取代传统的键合线互连。2010年,美国蒙大拿州立大学的研究人员设计了新型同轴型芯片互连系统[11]。该互连系统消除了阻抗不连续性,提供了带屏蔽的信号路径和开关信号的回流路径,解决了高速芯片封装的EMI问题。新型同轴型芯片互连系统的一种连接方式如图10所示。

图10 新型同轴型芯片互连系统的一种连接方式

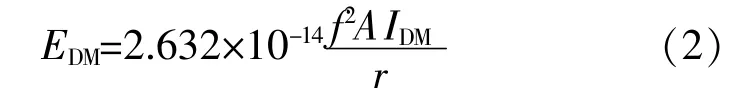

3.3 基于电磁带隙结构设计新型封装盖板

针对封装盖板引起的EMI问题,运用电磁带隙(EBG:Electromagnetic Band Gap)结构可以有效地减少封装盖板引起的EMI,EBG结构的概念最初来源于光子晶体研究,目前被广泛地应用于微波领域,用于抑制谐波和提高噪声隔离度。其设计的基本原理[12-13]如下。

a)电磁波无法在间距小于λ/4的PEC(PerfectE)和完美磁导体(PMC:Perfect Magnetic Conductor)之间传播。

b)当PEC和EBG结构的间距小于特定的高度时,电磁波在任意方向都无法传播。而且,该高度通常小于λ/4;EBG结构对于TM波而言通常相当于人造PMC。

c)当PMC和PEC间距小于λ/4时,TM波在任意方向均无法传播;当PMC和间距小于λ/2时,TE波在任意方向均无法传播。

根据上述设计原理,一种基于周期性钉状结构的新型盖板被应用在封装中,结构示意图如图11所示,封装基板上方一定距离放置所设计的盖板,钉的高度是阻带带宽的决定因素;同时,带宽可以通过空气缝隙、钉的周期和宽度的优化来提升。

图11 带有周期性钉状结构的新型盖板

3.4 辐射EMI屏蔽

对于芯片封装中的电磁耦合问题,可以采用屏蔽的方法,一种新型三维混合信号芯片屏蔽堆叠结构可有效地抑制其产生的辐射EMI[14],如图12所示。在新型堆叠结构中,模拟射频芯片可以放置在芯片堆叠的下层,可以采用键合线或者倒装焊封装方式与基板连接,将模拟射频芯片塑封并减薄后外层涂覆一层“屏蔽胶”与基板的接地过孔相连,再装配外层的数字芯片,最后整体塑封。内层的塑封起到保护底层芯片、支撑外层芯片和涂覆“屏蔽胶”载体的作用。表面涂覆的“屏蔽胶”可以采用普通的高电导率的导电银胶,也可以是掺杂铁、钴、镍或相应的合金等高导磁率、高导电率微颗粒的胶体。 “屏蔽胶”与基板的导热孔和基板接地金属层相连形成屏蔽结构,起到屏蔽信号噪声和散热的作用。为了保证屏蔽结构的屏蔽效能,基板上的导热孔间隔小于屏蔽电磁波最小波长的1/4甚至小于波长的1/20。新型的三维屏蔽结构中的内层塑封可以通过减薄工艺降低塑封高度, “屏蔽胶”的厚度可以控制在10~20μm左右。

图12 新型三维混合信号芯片屏蔽堆叠结构

4 结束语

在芯片封装设计中,必需考虑其EMC,尤其是辐射EMI问题,以确保信号完整性,保证芯片功能的正常实现。通过分析封装设计中存在的EMI隐患问题,针对不同的辐射EMI问题而有针对性地提出抑制方法,降低EMI对芯片电路的影响,确保芯片的可靠性和质量。