电解铜箔在印制电路板端的评估方法研究

周文木 胡智宏

(江南计算技术研究所,江苏 无锡 214083)

电子铜箔构成了PCB(印制电路板)的“神经网络”,当前PCB用铜箔的品种与性能正走向“多元化”,市场走向“细分化”[1],不同类型覆铜板(CCL)在性能要求向个性化、差异化的演变,对铜箔性能的专用匹配要求进一步提高。铜箔除了形成线路图形,在提高阻抗控制精度、降低高频高速信号传输损耗、降低无源互调(Passive Inter-Modulation,PIM)等介电特性及确保印制板可靠性等方面,都发挥了重要作用。

1 电子铜箔的分类

电子铜箔分为电解(ED)铜箔和压延(RA)铜箔两大类,覆箔叠构PCB层压时使用ED铜箔,刚性CCL本身为ED铜箔,部分挠性覆铜板(FCCL)也使用低粗糙度、高耐折性的ED铜箔。ED铜箔比例占据电子铜箔的绝对优势,本文主要探讨ED铜箔。

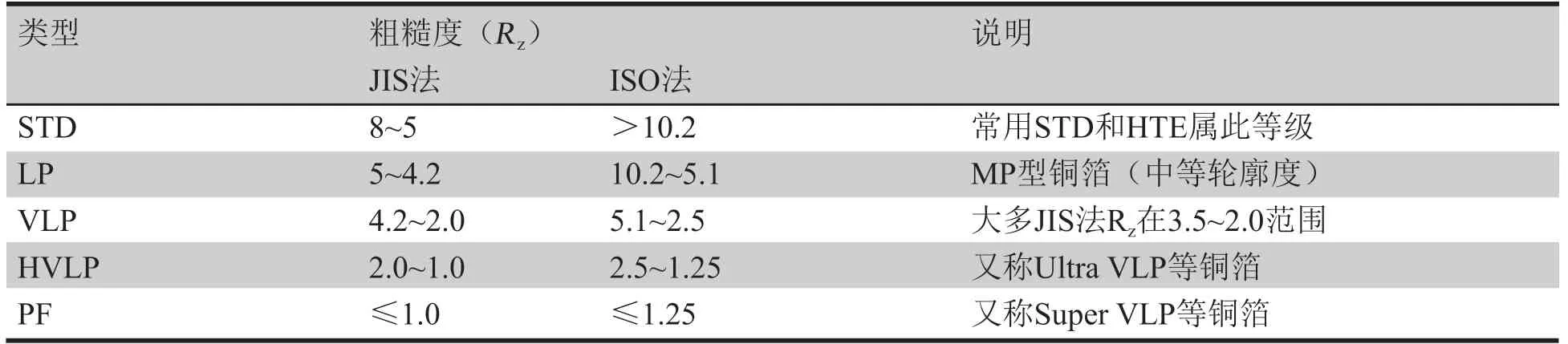

随着铜箔表面粗糙度处理技术的发展,ED铜箔按照表面粗糙度划分,有常规轮廓(STD型)、低轮廓(LP型)、超低轮廓(VLP型)、极低轮廓(HVLP型)和无轮廓(Profile Free,PF型)[1][2]。HVLP型进一步可细分为HVLP1、HVLP2、HVLP3;PF型强调无铜瘤、平滑,具体见表1所示。反转铜箔(RTF)的Rz值同属于VLP范围,而Rq值又与 HVLP的接近,RTF具有一般铜箔之晶粒形态与机械性质,在本质上仍是一般铜箔。HVLP铜箔处理技术在2010年左右问世,采用全新微细结晶结构毛箔+微细瘤化特殊表面处理技术,毛箔呈现片层状结晶构造(类似RA铜箔),区别于常规电解铜箔的树枝状结晶构造,瘤化颗粒直径小、峰谷之间距离短,瘤化颗粒层将毛箔轮廓的峰与谷全部覆盖。覆箔叠构表层主要采用STD型HTE(高温延展电解铜箔)铜箔,较少采用RTF或VLP、HVLP铜箔;当表层有高频高速线路布设、传输损耗降低等需求时,通常直接采用覆板叠构。需要特别说明的是,PCB表层流程复杂,阻焊前粗糙化处理、阻焊油墨类型、最终表面处理等均对传输损耗有较大影响,高频高速板通常不推荐表层布设精细线路并走高频信号。PCB端在评估CCL内铜箔或PCB用铜箔性能时,需要掌握铜箔本身设计细分性、表面处理工艺流程、相关规范标准以及待评估的CCL或铜箔对树脂和PCB工艺的匹配性,这样才能更好指导PCB端选用最合适的产品,优化工艺和制造过程,提高PCB的可靠性。

表1 PCB端评价铜箔性能的层级及涉及的主要标准项目表

表1 ED铜箔按表面粗糙度(Rz)分类表

2 电解铜箔的表面处理

电子铜箔在完成原箔(毛箔)制造后都要进行表面处理,使铜箔与绝缘树脂压合后具有一定的结合力,并具有一定的耐化学药品性、耐热性、耐离子迁移性和防氧化性等性能,进而才能满足PCB制造要求。

ED铜箔的粗糙面(Matte Side,M面)表面处理流程包括:预处理(除油、酸洗)、粗化固化、镀阻挡层(又称障壁层或耐热层)、表面钝化(又称防锈或防氧化)、涂硅烷偶联剂及烘干等流程[3][4]。粗化固化用于形成瘤状的微观粗糙面,并增加粗糙面与毛箔的结合力。为克服PCB生产过程中铜箔易氧化变色、耐腐蚀性、耐离子迁移性较差等问题,并提高产品的耐热性和高温抗剥强度,在固化层上再镀覆一层其他单金属、两元甚至三元合金的阻挡层,如锌、镍、钴、锌-镍合金、镍-磷合金、镍-硫合金、锌-钴-砷合金、锌-镍-铅合金、镍-钼-钴合金等。阻挡层厚度通常为几纳米至几十纳米,其厚度不会破坏前道工序形成的微观粗糙面,大量专利开发了许多具有特殊性能和用途的高端铜箔的生产方法和表面处理技术。镀阻挡层后的铜箔用铬酸盐(或铬酸盐和锌盐)溶液进行表面钝化,使铜箔表面形成以铬(或铬锌)为主体的结构复杂的膜层,使铜箔不会因直接与空气接触而氧化变色,同时也提高了铜箔的耐热性、可焊性及对油墨的亲合性。为进一步提高铜箔防氧化能力、提高铜箔与树脂的浸润性和黏结强度,钝化后的铜箔还需均匀喷涂硅烷偶联剂等有机试剂而形成一层有机膜。电解铜箔的光面(Shiny Side,S面),一般只有一层电析出附着的锌铬盐防氧化膜。

3 相关标准对铜箔性能的评价

对电子铜箔性能的评价从产业链角度有多个层级,包括CCL组分(铜箔)级、CCL级、PCB级、部件级、分系统级、整机系统级等,构成了上下游的关系。对于PCB端,直接与铜箔性能相关的评价包括前3个层级,相关标准包括国际电工委员会标准(IEC)、国家标准(GB、GB/T)、行业标准(SJ、GJB、QJ)、国外标准(IPC、JIS、MIL)等不同类型。

铜箔级标准,IPC4562A-2008《印制线路板用铜箔》涉及19个测试项目,在IPC-TM-650《试验方法手册》中规定。GB/T 29847-2013《印制板用铜箔试验方法》主要参考了IPC4562A-2008和IPC TM-650,对PCB用铜箔外观、尺寸、物理性能、工艺性能、特殊性能涉及20项检验做出了具体规定[5][6]。

CCL级标准,GB/T 4722-2017《印制电路用刚性覆铜箔层压板试验方法》标准主要参考了IEC 61189-2:2006《电气材料、互联结构和装联试验方法第2部分:材料互联结构的试验方法》及其他先进标准。与铜箔相关测试项目概括为:外观、物理和化学性能、机械性能、电性能等[7][8]。

PCB级标准,常用的包括IPC 6012E-2020《刚性印制板鉴定与性能规范》、GB/T 4588.4-2017《刚性多层印制板分规范》、GJB 362B-2009《刚性印制板通用规范》、QJ 831B-2011《航天用多层印电路板通用规范》、QJ 832B-2011《航天用多层印制电路板试验方法》等,从PCB物理性能、电气性能角度评价。

4 PCB端对刚性PCB用铜箔评估

山东金宝电子股份公司的杨祥魁等[9]从铜箔制造端角度,以铜箔生产制成控制原理、方法和实际管控等方面,讨论电解铜箔在厚度控制、抗剥强度、粗糙度、耐化性如何应对CCL和PCB的要求。PCB端评估电子铜箔除了依据GB/T 29847-2013等标准对铜箔本身进行外,应覆盖材料服役环境并充分考虑材料实现功能的层级,遵循自上而下的需求分析以及自下而上的评估验证。以下结合PCB行业及笔者工作中遇到的相关问题,针对性提出几类重点关注的评测项目及方法。

4.1 外观、规格尺寸和表面粗糙度

4.1.1 影响因素分析

铜箔的外观检验包括表面及边缘平整性、颜色均一性、铜粒、皱褶、针孔、清洁度、异物等,外观一致性侧面反映了铜箔制造过程的稳定控制。规格尺寸检验包括长宽尺寸、厚度等;铜箔的厚度有标称厚度和机械厚度两种,标称厚度又称标重指铜箔的单位面积质量,机械厚度指截面切片厚度。铜箔制造过程一般通过控制毛箔的标重和表面处理沉积量来控制厚度,表面处理对铜箔厚度的调节主要是粗化固化流程。标重相同的铜箔,表面粗糙度越大其机械厚度也偏大。铜箔标重的控制难点在于厚度一致性,其性能对PCB线宽一致性至关重要。业内惯用的铜箔表面粗糙度(轮廓度)是采用接触式粗糙度测量仪测定,表征粗糙度参数一般有Rz、Ra、Rq、Rsar4种,其中前3种为线粗糙度,具体如图1所示。目前表面工程领域,越来越多采用非接触法获得面粗糙度,表征更为准确。PCB的插入损耗与铜箔粗糙度、PCB制程表面处理的关系已经成为铜箔、CCL、PCB上下游非常热门的研究课题。业界近年来铜箔研究、应用的新成果表明,插入损耗与铜箔的Rq、Rsar线性回归相关性最好。

图1 几种表征铜箔粗糙度的参数的定义及特点图

4.1.2 测试项目及方法

通常采用测量不同生产批次、不同取样位置的单位面积质量获得铜箔标重,并在对应位置进行显微切片以进一步获得机械厚度。采用接触式粗糙度测量仪、激光共聚焦显微镜、SEM(扫描电子显微镜)、AFM(原子粒显微镜)等多种方法来测试不同取样位置铜箔M面的微观形态,获得粗糙度参数。依据GB/T 29847-2013,可采用胶带转移法或滤纸法评估铜箔是否有铜粉,将铜箔放在坚硬平坦的台面上,使一定长度3M胶带粘在铜箔M面上,用干净的碎布使之粘固,再瞬间扯下胶带,目视检查胶带上有无铜粉;也可采用中性中速滤纸沿铜箔M面纵向轻拭或在滤纸顶部放上固定重量的砝码拖拉,用肉眼观察滤纸表面,并与清洁滤纸比较,通常要求无铜粉转移。

4.2 剥离强度

4.2.1 影响因素分析

剥离强度测试包括CCL本身和PCB两种,影响因素主要有:(1)表面粗糙度、比表面积和均匀性;(2)粗化层的形状与大小;(3)树脂类型;(4)硅烷偶联剂的种类和涂覆量;(5)层压工艺状况等。

一般铜箔依靠“锚定”效果使铜箔和树脂间有较好的黏结力,低轮廓铜箔“锚定”效果有限,更注重于化学黏结力,通常铜箔粗糙度越大,剥强度越大。相同粗糙度条件下,表面采用微细粗化技术的比普通粗化的抗剥强度要大,具有微细粗化技术的铜箔比面积相对更大。铜箔阻挡层合金成分不同对剥强度也有一定影响,这是不同合金元素与硅烷偶联剂的成键有差异造成的[10]。

CCL正向高Tg、低CTE、无卤素、高速化发展,总体上黏结力在逐渐降低,在FR-4上35 µm铜箔的剥强度能达到2.0 N/mm以上,常规无卤板上只能达到1.4 N/mm左右,而高速PPE(聚苯醚)树脂上采用HTE、RTF、HVLP铜箔压合后的剥离强度仅能达到1.0 N/mm、0.7 N/mm和0.6 N/mm左右,甚至更小。

硅烷偶联剂的种类和涂覆量,与树脂的匹配很关键,特别是低轮廓铜箔。硅烷包含了能与有机及无机反应的两种类型的官能团,因此既能在铜箔的铬处理层形成化学键,也能与树脂形成化学键。硅烷的一般化学式为(RO)3-Si (CH2)n-Y,式中RO为水解性基团,如甲氧基、乙酰氧基等,对无机物具有反应性,水解后能与铜箔表面羟基发生缩合反应;Y为有机官能团,如氨基、环氧基等,对有机物具有反应性或相容性。硅烷与树脂间的反应较为复杂,但一般认为树脂聚合物的化学反应基团与硅烷偶联剂的相匹配可以产生较强的化学键,提高铜箔与树脂的结合力[11]。当然,层压时的压力、温度、时间等参数对树脂的交联效果影响很大,会直接影响到剥离强度的高低。通常要求控制∆Tg≤3 ℃。

4.2.2 测试项目及方法

首先,采用标准图形测试剥强度,包括常态下的剥强度(a)、各类劣化处理后剥强度(b),如高温储存后、回流焊后、煮沸处理后、HCl浸渍后、液碱浸渍后等,并计算劣化率。测试时包括MD(Machine Direction)和TD(Transversal Direction)两个方向。

劣化率=100%×(a-b)/a

其次,采用CCL本身或铜箔压制成PCB进行钻孔披锋测试和印制插头铣板、斜边测试,试验板经过正常钻孔、去毛刺、电镀后放大镜检查+微切片观察孔口有无异常;依据潜在PCB特征,设计实验观察试验板铣切后印制插头引线有无扯起,印制插头斜边后引线有无翘起等异常。最后,模拟PCB及后续电装焊接,依据潜在PCB的设计极限,设计不同尺寸的圆盘、方形盘、长条形盘,分别进行热风整平、化金等表面处理,然后多次过再流焊,最后进行模拟返工或热应力试验,观察是否有焊盘脱落或浮起,并进行非支撑元器件孔焊盘拉脱强度测试。

4.3 抗氧化性及微蚀性评估

4.3.1 影响因素分析

抗氧化性是复合镀层和有机硅烷的共同贡献,包括常温和高温抗氧化两个方面。常规抗氧化又称常温储存性能,一般是铜箔的耐候性,是铜箔在存放过程中不会氧化。

高温抗氧化性能是保证铜箔与树脂压合或PCB制造过程中不会因高温而氧化变色,一般指200 ℃左右的抗氧化能力,特殊使用场合要求260 ℃以上的抗氧化能力。为使铜箔在260 ℃以上的高温不氧化,应采用高沸点金属(如铟、钨、钒等)合金阻挡层,如PTFE(聚四氟乙烯)、PI(聚酰亚胺)、LCP(液晶聚合物)等需要高温高压合的特殊材质CCL。铜箔的S面有一层电析出附着的锌铬盐防氧化膜,其成分及厚度会对内层单片微蚀、贴膜效果有一定的影响,薄膜增厚,耐腐蚀性增强,但易出现H2SO4-H2O2微蚀条纹状或贴膜不牢;减少膜厚会影响S面的抗氧化性。通常在钝化盐膜中锌量越高,铜箔的抗高温氧化性越强,铬量越高,常温存放能力越强。

4.3.2 微蚀性及贴膜不良案例

珠海杰赛科技的谢国荣等[12]发现,干膜在RTF铜箔表面显影后容易残留余胶,进而造成内层单片蚀刻后板面残铜,采用降低影速度的方式可进行残铜改善。笔者所在单位曾经使用一种双面厚铜箔105 μm/105 μm CCL,经过正常的H2SO4-H2O2微蚀前处理、贴膜、LDI(激光直接成像)曝光、酸性CuCl2蚀刻后,发现严重的线路表面弱蚀现象,放大镜下观察显影后单片,发现干膜图形与铜箔结合的界面出现不连续浮离,蚀刻过程中界面被酸性蚀刻液侵蚀攻击造成线路表面弱蚀,更换该CCL的铜箔厂家后再无类似问题发生。因此,PCB端应与上游CCL供方签订质量协议,明确CCL组分的技术状态,发生变化时必须及时通知甲方验证确认。

4.3.3 测试项目及方法

采用高温储存试验评估抗氧化能力,如将铜箔样品卷起,M面朝外,放入200 ℃烤炉2 h后,取出冷却后目视检查有无氧化变色或其他异常。CCL本身或铜箔与FR-4半固化片压制成CCL,采用GB/T29847-2013规定的化学清洗性、可焊性(边浸法)测试,并采用PCB端常用的水破试验评估CCL与贴膜前处理制程的匹配性。

4.4 蚀刻性及绝缘性评估

4.4.1 影响因素分析

蚀刻性与铜箔结晶特性、M面粗糙度及耐化性关系密切。层间绝缘性与铜箔M面粗糙度Rz值相关,特别是局部异常峰高,铜牙扎入过深会产生严重影响;同层绝缘性与铜箔M面粗糙度、阻挡层、钝化层有关。结晶越疏松蚀刻速度越快,如DBC陶瓷板的烧结铜非常容易蚀刻,ED铜箔与Ra铜箔蚀刻速度也有差异。M面Rz值过大容易导致PCB蚀刻残铜,若有铜牙脱落,易造成PCB线间间距变小、甚至短路。M面粗糙度越低,蚀刻后越有利于获得光滑的线路,且小间距图形表面处理(如化镀金)后越不易出现镍脚、短路问题。铜箔阻挡层的金属成分及厚度影响蚀刻化学反应速率,进而影响线路侧面光滑性。耐腐蚀性过强,蚀刻后线条边缘向外延伸,蚀刻因子降低,精细线路制作性变差,严重时可能出现同层线路间耐压不足、绝缘不良等问题;耐腐蚀性过低,蚀刻因子高,但线条侧壁与绝缘介质接触界面向内凹陷,剥强度下降,铜箔的耐腐蚀性能需平衡。

4.4.2 蚀刻性及绝缘性不良案例

博敏电子的陈世金等[13]探究了某款HDI(高密度互连)产品成品阻抗超差(偏大)的原因,发现该HDI芯板L13层蚀刻后部分单片的线宽不一致,通过表面颜色、光亮度的差异,排查发现同一CCL供方使用了两种不同上游厂家的铜箔,虽铜厚等规格一致,但由于结晶致密性差异造成同样蚀刻参数蚀刻后线宽不同,最终影响到阻抗的控制。一方面说明上游CCL供方技术状态管控出现问题,另一方面说明不同品牌规格的内层单片蚀刻参数应当做首件确定,不可混用、完全并用。

笔者近期牵头开发多款高多层高速PCB,内层差分阻抗控制公差均要求≤5%,其中某款使用A品牌CCL(搭配某日系HVLP铜箔)的高速PCB成品内层阻抗中值虽能控制在目标范围内,但详细分析阻抗测试数据发现,数据较为离散,Cpk偏低,且有少量超出公差范围;而其他多款使用相同损耗等级B品牌CCL(HVLP铜箔)的高速PCB成品内层阻抗数据集中度非常好,Cpk较大,完全符合目标要求。笔者单位与PCB供方合作排查发现,内层单片蚀刻后线路不平滑、局部区域有毛边,正常区与毛边区线宽有近10µm差异,通过调整贴膜前微蚀量、贴膜速度、显影速度和蚀刻放板方向等因素进行试验,线路不平滑的状况无明显改善,判定该状况由CCL的铜箔本身特性所造成。CCL供方协助进一步采用扫描电镜(SEM)、能谱分析和微切片等手段分析表明,毛边产生于铜箔M面,表现为线路底部蚀刻不净,而顶部正常,毛边位置线路结合面铜牙良好。而将该CCL的HVLP铜箔更换为规格接近的某台系铜箔后,进行同等条件内层蚀刻,无上述毛边、线路不平滑等问题(见图2所示)。经笔者分析,大概率为该CCL使用的日系品牌铜箔耐腐蚀性过强导致。

图2 线路蚀刻铜箔底部毛边状况图

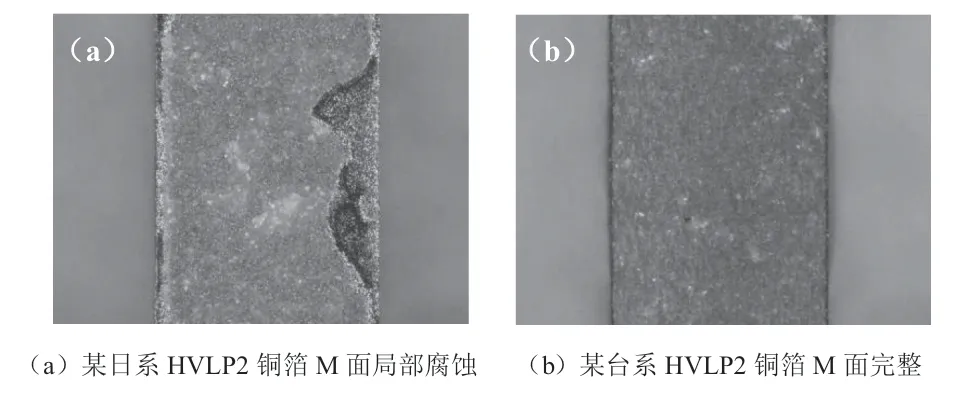

笔者所在单位曾批产某超高层高速背板,该产品使用B品牌CCL(搭配某日系HVLP2铜箔),内层布设密集阻抗线。该产品外层蚀刻后开短路测试发现有约10%比例的产品有绝缘不良问题,不良点从1个至数十个,经分析不良点多位于内层密集差分线位置,分布无固定规律,切片发现在异常点位置铜箔与树脂结合界面有局部点状发黑现象。CCL供方协助采用同样树脂体系搭配该日系HVLP2和另一台系HVLP2铜箔压制成CCL后进行了耐酸、耐碱、两遍棕化处理(Multi Bond、CZ和Flat Bond 3种不同的棕化液分别处理)等耐化性试验,分别剥离铜箔后观察M面状况,发现该日系铜箔两遍Multi Bond棕化处理后有局部腐蚀现象,见图3所示。目前针对此树脂体系,CCL供方已彻底改用某台系HVLP2铜箔搭配。

图3 不同品牌HVLP2铜箔在Multi Bond处理2遍后M面状况图

4.4.3 测试项目及方法

CCL本身或铜箔压制成CCL,采用CuCl2蚀刻法测试,依据潜在PCB的设计极限,设计不同方向、不同尺寸的密集焊盘、密集平行线以及孤立线,样品分别采用酸性CuCl2、碱性CuCl2溶液进行蚀刻试验,通过体视放大镜、线宽测量仪等观测蚀刻后精细线路图形精度及线路边缘品质。

可采用湿热后绝缘电阻、抗电强度(介质耐电压)试验评估同规格介质、不同铜箔搭配的绝缘性能差异,依据潜在PCB的设计极限,设计同层和层间测试图形,依据QJ 832B-2011、GJB 7548-2012测试方法实施。

5 结论

铜箔的可靠性由固有可靠性和使用可靠性组成,PCB端在评估其性能时,应掌握铜箔本身设计细分性、表面处理工艺流程、相关标准以及工艺的匹配性。铜箔固有的加工过程影响其外观、表面微观形态、抗剥强度、抗氧化性、微蚀性、蚀刻性及绝缘性等性能,而这些性能又与CCL或PCB的树脂种类、工艺制程、PCB产品规格相关,需设计跨越产品规格指标的实验来充分评估其对PCB的适用性、使用可靠性。