一种新型高速低功耗可重构流水线乘法器设计

姚 英,田心宇,韩晓聪

(1.西安邮电大学电子工程学院,陕西西安 710121;2.西北工业大学第365 研究所,陕西西安 710065)

当今科技发展日新月异,数字信号处理应用日益广泛,处理速度的要求越来越高,由此带来的功耗问题日益突出,常常成为限制电路性能进一步提高的“瓶颈”。通常在电路设计过程中,以最高频率作为电路处理的标准频率,但其日常处理需求一般都远远低于最高频率,故造成严重的资源浪费。乘法运算是数字信号处理的核心,乘法器电路的设计直接影响了整个系统性能。文中提出了一种新型的高速低功耗电压可重构流水线乘法器,该乘法电路通过“流水”结构保证了高的运算速度,还根据输入信号的速率调整电源电压,在输入信号的速率较高时使用正常的电源电压,当输入信号速率较低时将电源电压调整为低电压,以保证高速信号正常处理,在处理低速信号时显著降低了功耗[1],并以二进制无符号乘法为例对新型高速低功耗电压可重构流水线乘法器的设计理论及方法进行了阐述,对其速度和功耗等性能进行了Spice 仿真与分析[1-10]。

1 乘法器基本理论

通常的无符号数乘法以二进制数的形式进行。

两个无符号数A、B为:

乘法运算定义如下:

在现代数字信号处理电路的设计中,由于处理的数据量越来越大,所以应尽可能提高电路的频率,以保证其单位时间的数据处理能力,所以多采用“流水”结构。

2 高速低功耗电压可重构流水线乘法器设计

2.1 电路时延分析

一个电路为了保证最后结果正确性的最小延时如式(3)所示:

其中,tc、td分别为电路中寄存器的传播延时和建立延时,tmax为电路的最大传播延时。

在乘法电路设计中,“流水”结构由于其高速、高效及低输入电压的特点被广泛应用[11-14]。

“流水”结构即将一个时钟周期内的工作可分成N个时钟完成,以达到成倍提高电路频率的目的,其最小延时如式(4)所示:

其中,max(t1,t2,…,tn)为N个电路部分中的最大延时。

式(3)中tmax明显大于式(4)中max(t1,t2,…,tn),所以采用流水结构有效降低了乘法器的时延,大大提高了运算速度[15]。

2.2 逻辑设计

“流水”结构显著提高电路频率的同时显著增加了寄存器数量,流水级数越多寄存器数量增加越多,电路功耗显著提高。在电路处理信号频率远远低于电路最高速率时带来了巨大的资源浪费[16]。

基于此,文中设计了一种比例降低电源电压的乘法器设计方法,在输入数据速率低于电路最高处理频率时降低电源电压,以达到有效降低电路功耗的目的。对提高电路性能而言,使用该技术的代价相对较小,性价比较高。

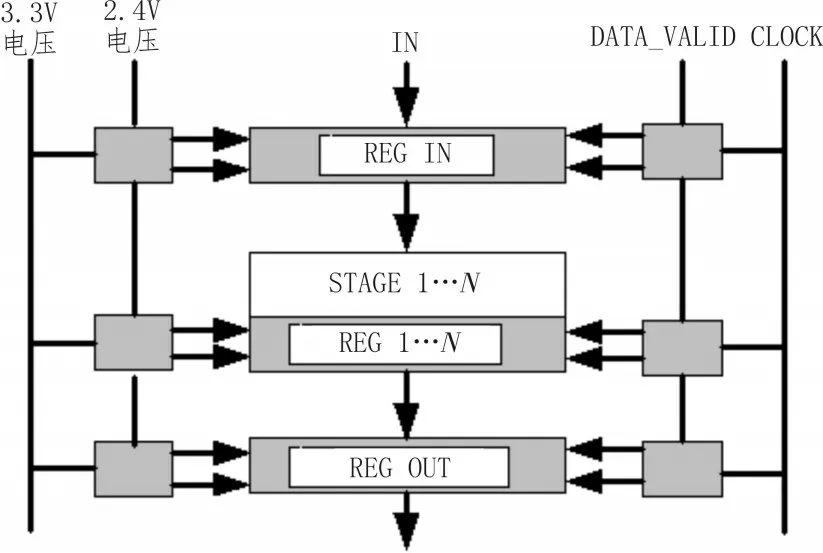

电压可重构流水线乘法器结构如图1 所示,采用3.3 V 和2.4 V 两种电压供电,在处理高速率信号时使用3.3 V 电压供电,在处理低速信号时使用2.4 V 电压供电。

图1 电压可重构流水线乘法器

2.3 电路设计

通常乘法器由3 个部分构成:部分积计算、部分积累加及两比特乘法器最终实现电路。文中以两比特乘法器为例进行设计。

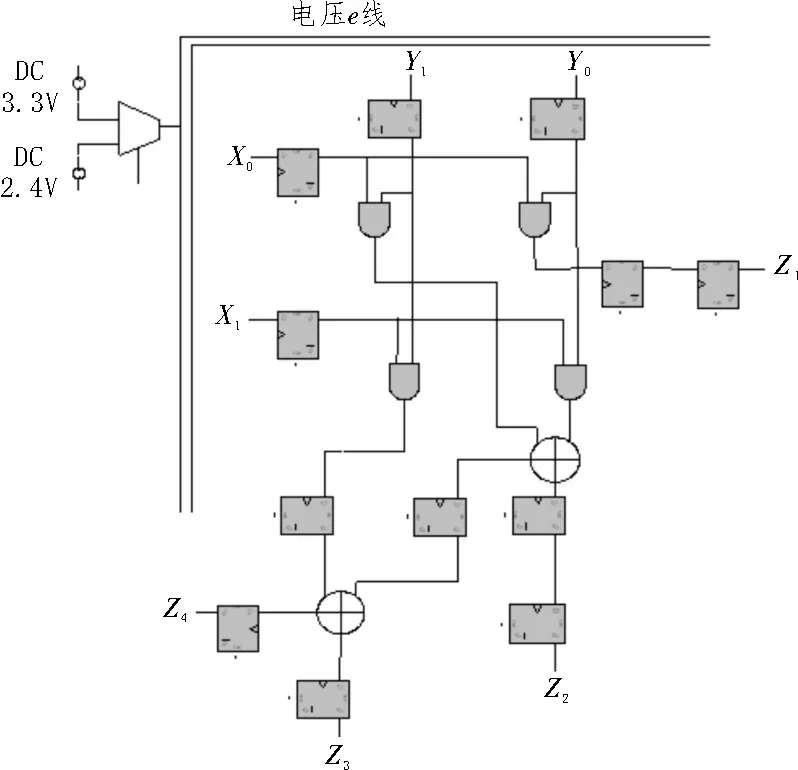

1)部分积计算。通常部分积的产生是由被乘数Xi与乘数Yj进行逻辑与计算的。图2 所示电路会产生4 个部分积:PP0、PP1、PP2、PP3,如式(5)~(8)所示,并对其做加法运算得到累加和。

部分积实现逻辑电路如图2 所示。

图2 部分积实现逻辑电路

2)部分积累加。部分积产生后,必须将它们相加求和。这种累加是一种多操作数的加法,故选取一种高效的加法器至关重要。但是多操作数的加法器实现电路比较复杂,延迟较大,所以使用两操作数的加法器。

3)两比特乘法器最终实现电路。两比特电压可重构流水线乘法器实现电路如图3 所示。

图3 两比特电压可重构流水线乘法器电路

图3 为一个高速两级流水电压可重构两比特乘法器的电路图。在该电路中使用上升沿有效的D 触发器作为输入输出寄存器[4-5]。它采用多级流水的方式并使用3.3 V 和2.4 V 两种电压供电,在处理高速率信号时使用3.3 V 电压供电,在输入信号速率远远低于最高速率时使用2.4 V 电压供电,显著降低功耗的同时保证了较高的处理速率。

3 模拟仿真

对图3 所示的高速两级流水电压可重构两比特乘法器进行仿真。该电路在两级流水的情况下,使用Spectre 在基于0.25 μm 的标准CMOS 工艺下(3.3 V电源电压)进行模拟仿真,其输出波形如图4 所示。图中前3 个时钟周期为准备时钟,从第四个时钟周期开始为有效输出,可实现的最高频率为1.8 GHz。利用Hspice 进行仿真,该高速流水线乘法器的频率为1.8 GHz 时,电路功耗为26.1 mW。

图4 电源电压为3.3 V的两比特流水线乘法器仿真波形

当需处理信号的频率低于1.2 GHz 时,为降低功耗,可采用低电源电压。高速流水线两比特乘法器电路频率为1.2 GHz 时,使用Spectre 在基于0.25 μm的标准CMOS 工艺下进行模拟仿真,其电源电压最低可降至2.4 V,输入信号电压最低可降至1.5 V,其仿真输出波形如图5所示。此时功耗可降为9.3 mW,相比于3.3 V 电源电压电路处理低速信号时功耗降低约60%。

图5 电源电压为2.4 V 的可重构两级流水线两比特乘法器仿真波形

电压可重构流水线乘法器可根据输入信号的频率不同,调整电路的电源电压,极大地降低了电路的功耗。以文中的两比特流水线乘法器为例,当输入数据不超过1.2 GHz 时选择2.4 V 的电源电压,当输入数据大于1.2 GHz 小于1.8 GHz 时,选择3.3 V 的电源电压。用该方法构建多位流水线乘法器频率范围选择性更大,电路速度与输入信号速率更匹配,可节省更多的电路资源。而且,在处理不同数据速率信号时,使用不同的流水级数也可以更好地降低功耗,提高电路的性能。

4 结论

文中设计的电压可重构流水线乘法器具有结构灵活、频率高、功耗低、电路结构紧凑等优点。可根据输入信号的频率不同,调整电路的电源电压,极大且有效地节省了电路功耗。以文中的两比特流水乘法器为例,输入数据小于1.2 GHz 时选择2.4 V 的电源电压,当输入数据大于1.2 GHz 小于1.8 GHz 时,选择3.3 V 的电源电压,可降低功耗约60%。