高速大容量TLK2711接口卫星数传基带模拟源的研制

何品权,耿晨曦,张力丹,郑婉迅,夏巧桥

(华中师范大学物理科学与技术学院,武汉 430079)

随着航天科技的高速发展,卫星有效载荷的数据率也在日益提升,这给卫星数传分系统带来了巨大压力[1]。在整个卫星系统中,卫星数传分系统[2]占据着十分重要的位置,但其技术相对复杂且更新周期短,因此在每套数传分系统投入使用之前都要经历十分严格的测试。而考虑到现实情况与经济成本,卫星前端的有效载荷很难在数传分系统研制测试期间直接投入测试[3],故需要数传基带数据模拟源代替前端载荷为数传分系统提供测试激励[4]。

传统的基带数据模拟源一般采用单板卡的形式,在板卡上集成控制器、存储器、大容量缓存及接口电路,通过总线由主机发送控制指令到控制器,控制器在接收到相应指令后从储存器中将数据读取到大容量缓存中,缓存的数据以一定的时序通过接口电路发送出去。杨兆君[5]研制的高速载荷数据加载器,采用现场可编程逻辑门阵列(field programmable gate array,FPGA)作为核心控制器件,单路数据储存容量可以达到32 GB,使用FLASH阵列使板上容量达到了128 GB,低电压差分讯号(low-voltage differential signaling,LVDS)接口发送速率最高可达300 Mbps。但是该系统设计较为复杂,需要对16片的Flash芯片进行管理,可靠性较低,还需要额外使用一块EEPROM做坏块记录[5]。张卓等[6]研制的基带数据模拟源,采用XC2C1000芯片作为主控制器,选用NAND FLASH 芯片作为存储模块,输出接口为RS422与LVDS,速率最高可达250 Mbps。计算机通过USB接口将数据传给FPGA,由FPGA将数据写入16 GB NAND FLASH中,在数据发送的过程中对数据进行读取,整个过程涉及对FLASH的读、写、擦除操作以及坏块管理操作。鲁琴等[7]设计的卫星图像模拟源、张贵祥等[8]设计的星载光学遥感相机图像模拟源以及文献[9-15]也采取了上述设计方案。这些方案在当时的卫星数传分系统测试中发挥了十分重要的作用,但随着科技的不断发展也逐渐显露出了一些弊端。现今,模拟源的数据传输带宽低,数据存储容量小,已经无法满足对数传分系统高速率大容量的测试数据需求,对于数据处理速度较高的部件也无法检测其性能。随着技术的发展进步,当前大多数传分系统数据接口采用TLK2711接口,大量的学者进行相关的研究,蒋志胜等[16]提出了一种基于高速并串行与串并行转换器(serializer/deserializer,SERDES)接口芯片TLK2711应用设计的星载多通道高速串行数据路由系统,为卫星数传分系统数据路由提供了可行方案,并同时介绍了TLK2711的工作原理。对于数据的大容量存储,也有学者进行相关研究。白雪等[17]提出了一种基于FPGA的SATA 3.0存储阵列控制器,实现的阵列控制器,存储容量达4 TB,写入带宽达3.3 GB/s,读出带宽达3.4 GB/s。李晋涛等[18]优化了一种基于FPGA的控制存储系统,系统以SATA3.0作为传输总线,固态硬盘阵列作为存储介质,对存储逻辑进行了设计,并对硬件电路和带外(out of band,OOB)状态机进行了优化。最终实现了一种高速率,高稳定性的存储系统,解决了大容量存储系统的传输稳定性问题。

在参考中外相关研究以及现有技术的基础上提出了一种高速率、大容量的卫星数传基带模拟源。该模拟源采用Xilinx公司的xc7k480tffv1156-2芯片作为主控制器,采用自主设计的SATA3.0控制器作为数据源接口,为模拟源提供数据,可解决模拟源高输出带宽、大容量存储等瓶颈。采用FPGA自带的高速收发器实现TLK2711接口,节省FPGA的输入输出(input output,IO)资源,可实现16路TLK2711接口并行输出,同时接口线速率可动态调整,可解决模拟源的多通道高带宽输出问题。

1 系统硬件设计

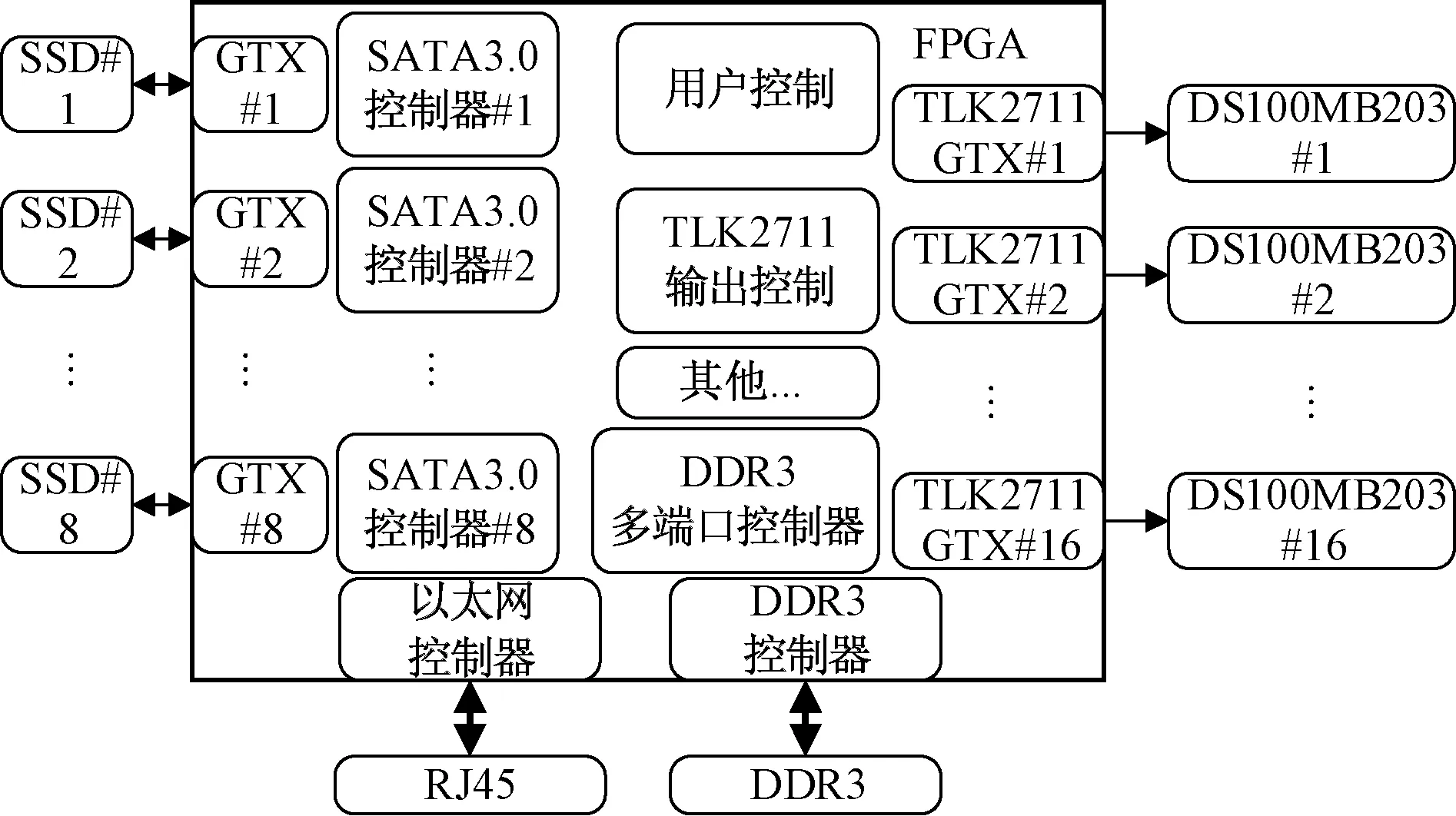

本系统的主控制器芯片为Xilinx公司的xc7k480tffv1156-2,支持48个全双工收发器通道;外挂一片8 GB(第三代双倍数据率同步动态随机存取存储器(double-data-rate three synchronous dynamic random access memory,DDR3)提供大容量缓存;并行挂载8路SSD硬盘提供模拟源数据,总带宽可达36.2 Gbps;采用FPGA内置高速收发器与DS100MB230芯片实现TLK2711接口时序;采用200 MHz恒温晶振为FPGA提供时钟信号。系统硬件结构如图1所示,其通过SSD硬盘或内部自检数据源提供有效载荷数据,由FPGA预处理后送入外部DDR3中缓存。输出控制模块从DDR3中获取数据送入高速收发器中,转换为TLK2711接口时序,高速收发器信号经DS100MB230芯片进行预加重与隔离处理后由超小型连接器(subminiature version A,SMA)接口输出。

SSD为固态硬盘;GTX为G比特收发器,常称为Serdes、高速收发器图1 系统硬件结构框图Fig.1 Structure diagram of the system hardware

2 模拟源FPGA程序设计

2.1 FPGA设计框架

上位机通过千兆以太网与模拟源设备进行交互,更新模拟数据,配置数据源模式、数据发送的正逆程、线速率等参数。本系统包含两种数据源:第一种数据源为自定义格式数据源,可以生成计数器、棋盘格、伪随机数等数据内容;第二种为固态硬盘(solid state disk,SSD)数据源,SSD中的数据可以预先写入,也可以通过千兆以太网将数据进行上载。两种数据源经过数据选择器将数据传输给DDR3多端口控制器模块,输出控制模块从DDR3多端口控制器模块读取缓存的数据进行处理,输出控制模块将处理后数据送入高速收发器,经高速收发器转换为TLK2711接口时序输出到相对应的物理管脚上。FPGA设计框图如图2所示。

图2 FPGA设计框图Fig.2 Structure diagram of FPGA

2.2 基于DDR3的多端口控制器

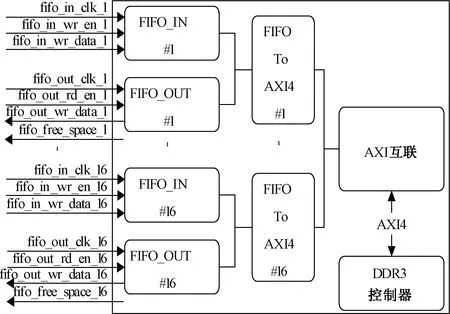

大容量DDR3高速缓存可使TLK2711接口稳定平滑地输出数据。本模拟源中DDR3的传输带宽为12.8 GB/s(DDR3-1600),储存容量高达8 GB。考虑单个用户逻辑无须使用如此高的数据带宽以及存储容量,而在本系统中存在多个用户侧逻辑同时缓存数据的需求,于是设计多端口控制器,提供多个先进先出(first input first output,FIFO)型接口,供多个用户侧逻辑同时读写数据。

DDR3控制器使用高性能扩展总线接口(advanced eXtensible interface,AXI4)总线进行访问,为实现多个AXI4主机接口对从机接口的访问,使用AXI-Interconnect进行AXI4总线扩展,可响应多个主机接口发起的访问请求。FIFO型端口由FIFO To AXI4模块完成地址更新,作为AXI4主机接口向从机DDR3控制器发起读写访问请求,其数据仅可读出一次,对外表现为大容量FIFO。其内部由AXI-Interconnect IP对多个AXI4主机接口发起的突发访问进行仲裁,按优先级响应多个FIFO的读写数据操作,其多个端口的读写总带宽小于DDR3的实际带宽。考虑到输入数据与多端口控制器工作时钟域不匹配的情况,在大容量FIFO外接一个异步FIFO对数据进行跨时钟处理。由16个FIFO型端口组成的多端口控制器如图3所示。

2.3 SATA3.0控制器

传统卫星数传基带模拟源储存容量较小,在对卫星数传分系统进行测试时数据码型通常无法进行完整的码型遍历测试。为解决其储存容量较小的问题,提出了一种基于SATA3.0控制器的卫星数传基带模拟源。SATA3.0控制器挂载SSD硬盘为卫星数传基带模拟源提供大容量的数据存储。实际储存大小可根据需求选择不同容量的SSD硬盘,单块SSD硬盘无法满足需求也可在FPGA上并行多路挂载扩充容量。SATA3.0硬盘控制器设计框图如图4所示。

fifo_in_clk_x为先入先出型数据缓存器缓存写入方向时钟;fifo_in_wr_en_x为先入先出型数据缓存器缓存写入方向数据写使能信号;fifo_in_data_x为先入先出型数据缓存器缓存写入方向数据接口;fifo_out_clk_x为先入先出型数据缓存器缓存读取方向时钟;fifo_out_wr_en_x为先入先出型数据缓存器缓存读取方向数据写使能信号;fifo_out_data_x为先入先出型数据缓存器缓存读取方向数据接口;fifo_free_space_x为先入先出型数据缓存器剩余空间大小图3 多端口控制器结构框图Fig.3 Structure diagram of the multi-port controller

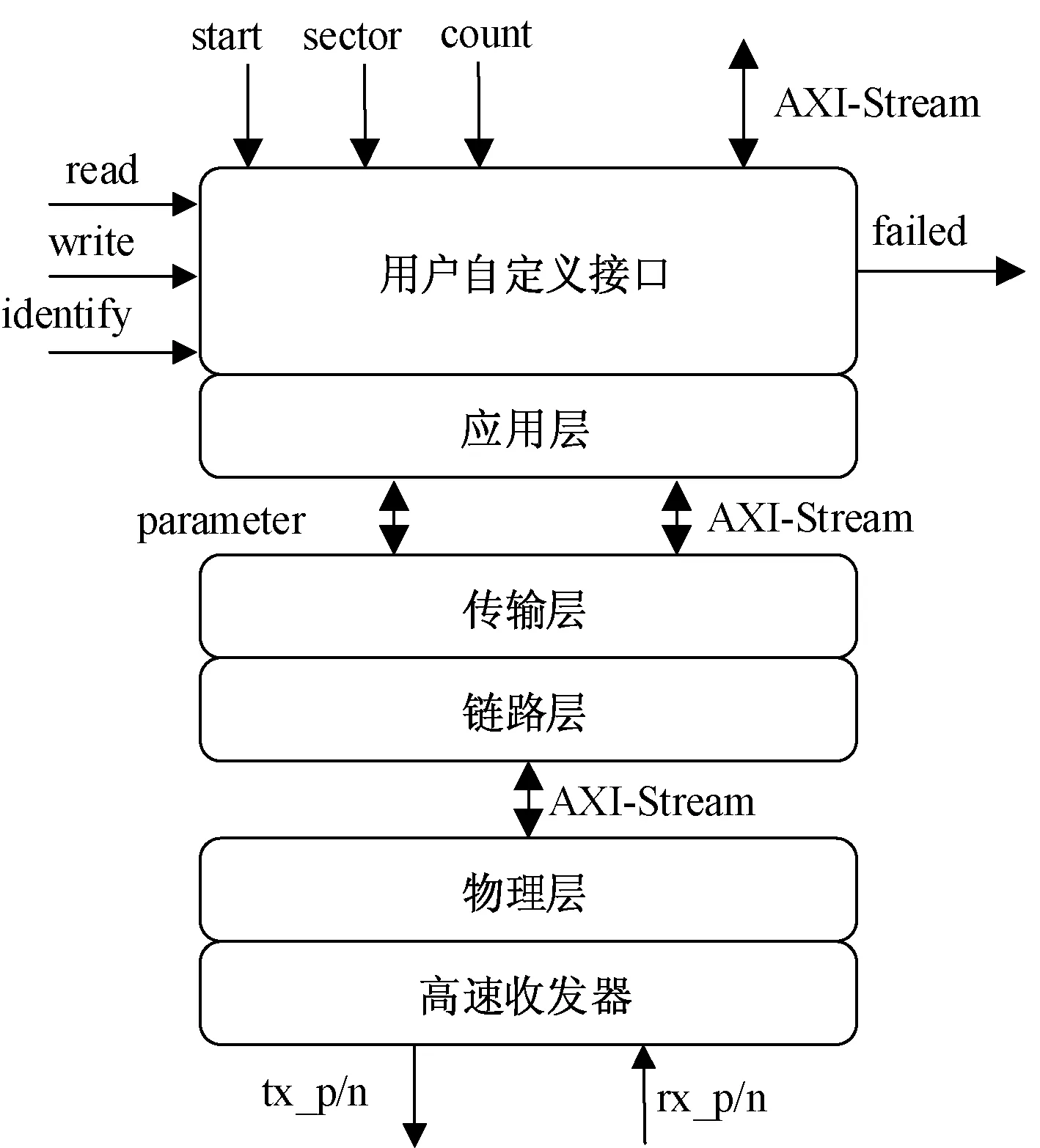

start为开始;sector为扇区;count为计数;read为读;write为写;identify为识别;parameter为参数;failed为失败;tx_p/n、rx_p/n分别为对外输出的物理管脚和差分管脚;tx为发送方向;rx为接收方向;p/n为差分管脚的正负极性图4 SATA3.0功能框图Fig.4 Structure diagram of SATA3.0

按照SATA3.0协议,整个控制器设计分为物理层、链路层、传输层、应用层以及用户自定义接口。每层之间数据交互采用标准的AXI-Stream接口进行设计,AXI-Stream接口基于数据流概念,包含数据交互握手信号,可以保障数据传输的可靠性,同时可以减少层次之间信号的耦合程度,确保每个层之间相互独立,为后期开发调试减少干扰。

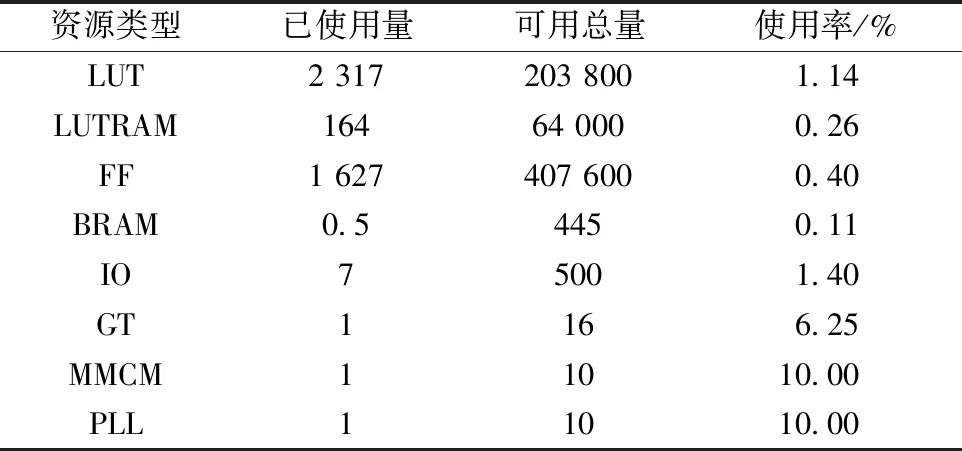

基于FPGA并行处理的特性,SATA3.0控制器实现了对数据的实时处理,节省了在数据处理期间缓存数据所占用的资源。整个控制器仅在数据的跨时钟域处理与链路层接收数据处设计缓冲区,使得整个控制器资源占用极低。在Xilinx公司 xc7k325t片上资源占用如表1所示。

表1 SATA3.0控制器资源使用Table 1 Resource use of SATA3.0 controller

2.3.1 物理层设计

物理层是整个协议的底层。主要实现以下功能:①SSD硬盘上电初始化;②硬盘状态监控;③高速收发器数据跨时钟域处理。高速收发器知识产权(intellectual property,IP)核、锁相环(channel phase-locked loop,CPLL)、混合模式时钟管理器(mixed-mode clock manager,MMCM)等硬件资源在系统上电后需要进行复位以保证其正常运行,因此设计了一种硬件资源复位模块保证相关硬件资源上电正常初始化。为防止由物理原因导致物理链路出现问题,同时提升整个控制器物理层链接的健壮性,采用逻辑清晰的状态机设计了物理层的控制模块,该模块可对硬件资源初始化状态以及工作状态进行监控,在出现异常后由该模块发出复位信号尝试对硬件资源进行重置,直到恢复正常链路通信。Xilinx高速收发器 IP核的数据位宽为16 bit,而整个控制器设计采用都是32 bit位宽,因此,在数据接收过程中需要存储来自收发器的两个完整的16 bit数据,并从中检测包含传输协议的字节,使用传输协议信息选择输出数据完成数据的重新对齐。在控制器中对数据操作通常需要在同一时钟域下,为了保证数据处理在同一时钟域下,采用异步FIFO的方式对系统时钟、SATA接收时钟、SATA发送时钟这3个时钟域下的数据进行跨时钟域处理。

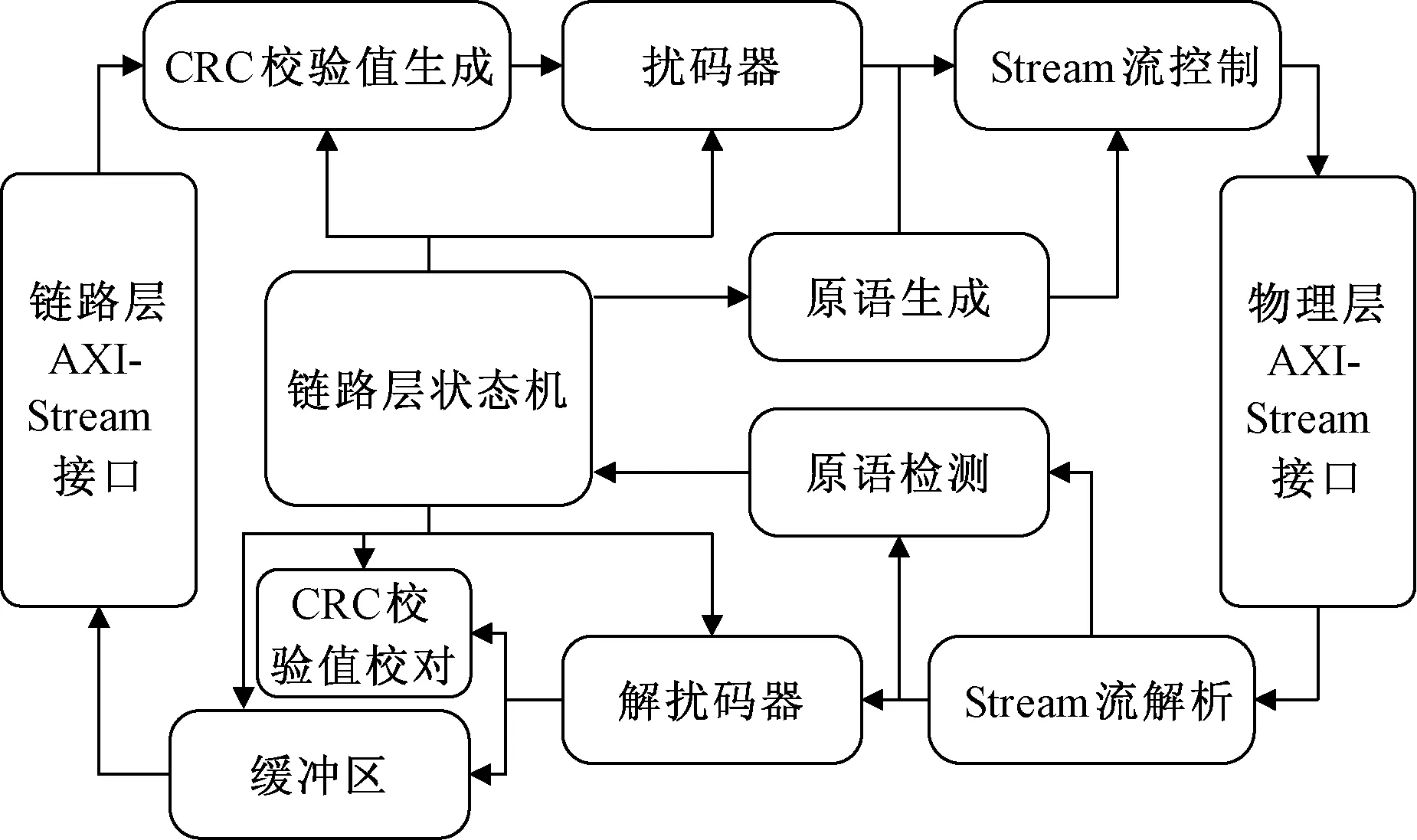

2.3.2 链路层设计

链路层与物理层和传输层接口采用AXI-Stream总线相连,在链路层中需要对数据进行加解扰、CRC校验以及原语通信,整个链路层设计需要考虑到数据能够可靠的由每个模块处理并输出,CRC校验模块与加扰解扰模块数据输入、输出接口也采用AXI-Stream总线接口,输入数据位宽为32 bit。FPGA具有数据并行处理的特性,在数据有效的情况下,一个时钟周期即可完成一次输入数据的CRC校验与加扰解扰,可实现对输入数据的实时处理,无须在数据输入时进行数据缓冲,降低了对硬件资源的占用。原语通信可以保障控制器与设备之间进行可靠的数据传输,在数据传输的过程中通过原语指令相互发送控制器与设备各自状态,协商传输数据。但原语通信具有一定的延时,因此,当控制器无法正常接收数据时,控制器链路层需要保证在控制器发出HOLD原语与设备接收到HOLD原语之间传输的数据不被丢失。因此在此处由一个FIFO对接收到的数据进行缓存,且FIFO深度为两次原语通信之间传输数据量的两倍。模块工作流程如图5所示。

图5 链路层工作流程图Fig.5 Workflow diagram of the link layer

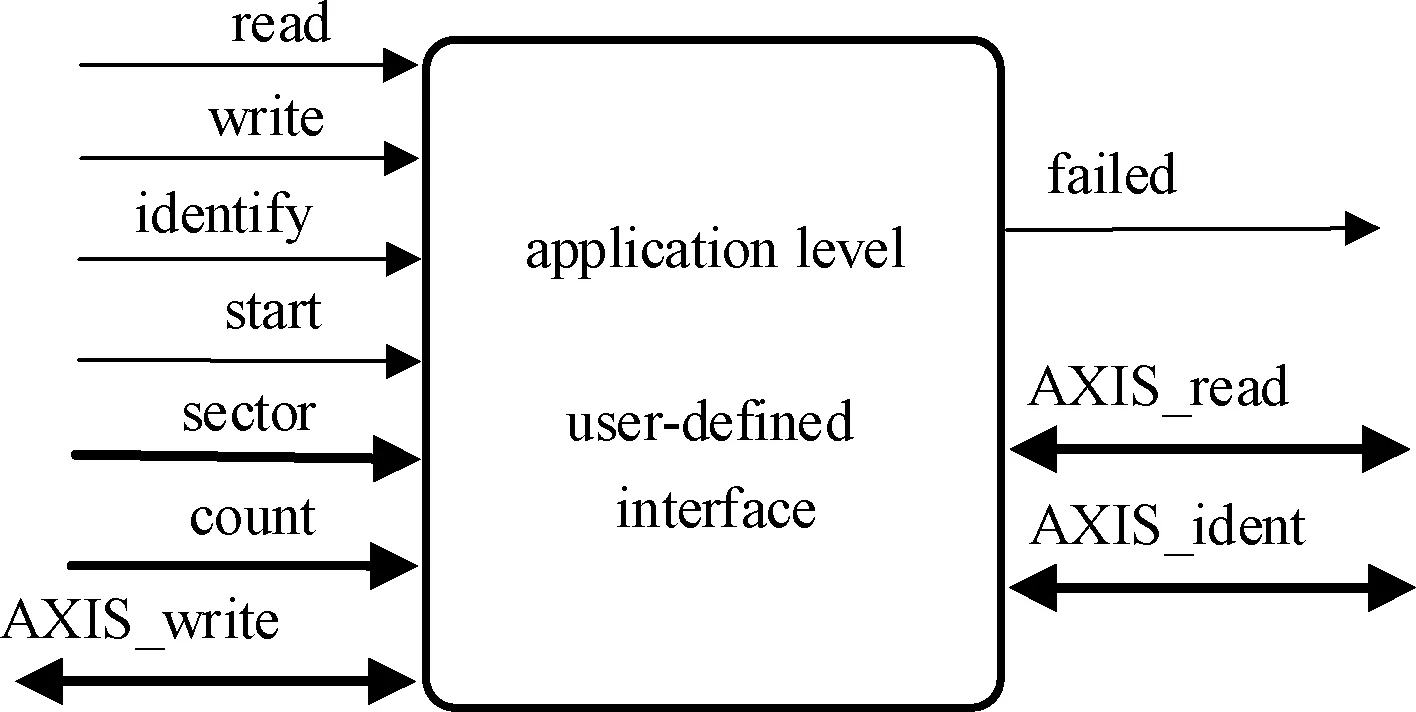

2.3.3 应用层与自定义用户接口设计

应用层为SATA3.0协议中的顶层,通过高级附加技术(advanced technology attachment,ATA)指令协商与设备间数据传输的方式。传输方式分为两种,一种为直接存储器访问(direct memory access,DMA)传输,适合大量数据传输;另一种为可编程输入输出(programmed input-output,PIO)传输,适合少量信息读取,如识别硬盘信息。应用层通过与传输层相连的参数接口发起与接收传输方式信息,数据由AXI-Stream总线进行传输。应用层另一端则是面向用户的接口,为方便用户控制,数据的输入与输出采用AXI-Stream总线,分别为写数据通道AXIS_write、读数据通道AXIS_read、读硬盘信息通道AXIS_ident。提供写数据、读数据、硬盘识别3种控制方式分别对应write、read、identify这3个控制信号,写数据与读数据共用48 bit数据位宽的起始扇区值接口sector、16 bit位宽的操作扇区数接口count以及1 bit的传输失败标志位failed。应用层自定义接口如图6所示。应用层start接口接收到用户发起的控制请求后在状态机中跳转到相对应的处理状态,与设备应用层协商数据的传输方式,待数据传输完成,将从设备接收到的传输状态信息返回到用户接口,完成一次控制请求。

start为开始;sector为扇区;count为计数;read为读;write为写;identify为识别;parameter为参数;failed为失败;application level为应用层;user-defined interface为用户自定义接口图6 用户接口框图Fig.6 Structure diagram of the user interface

2.4 TLK2711接口设计

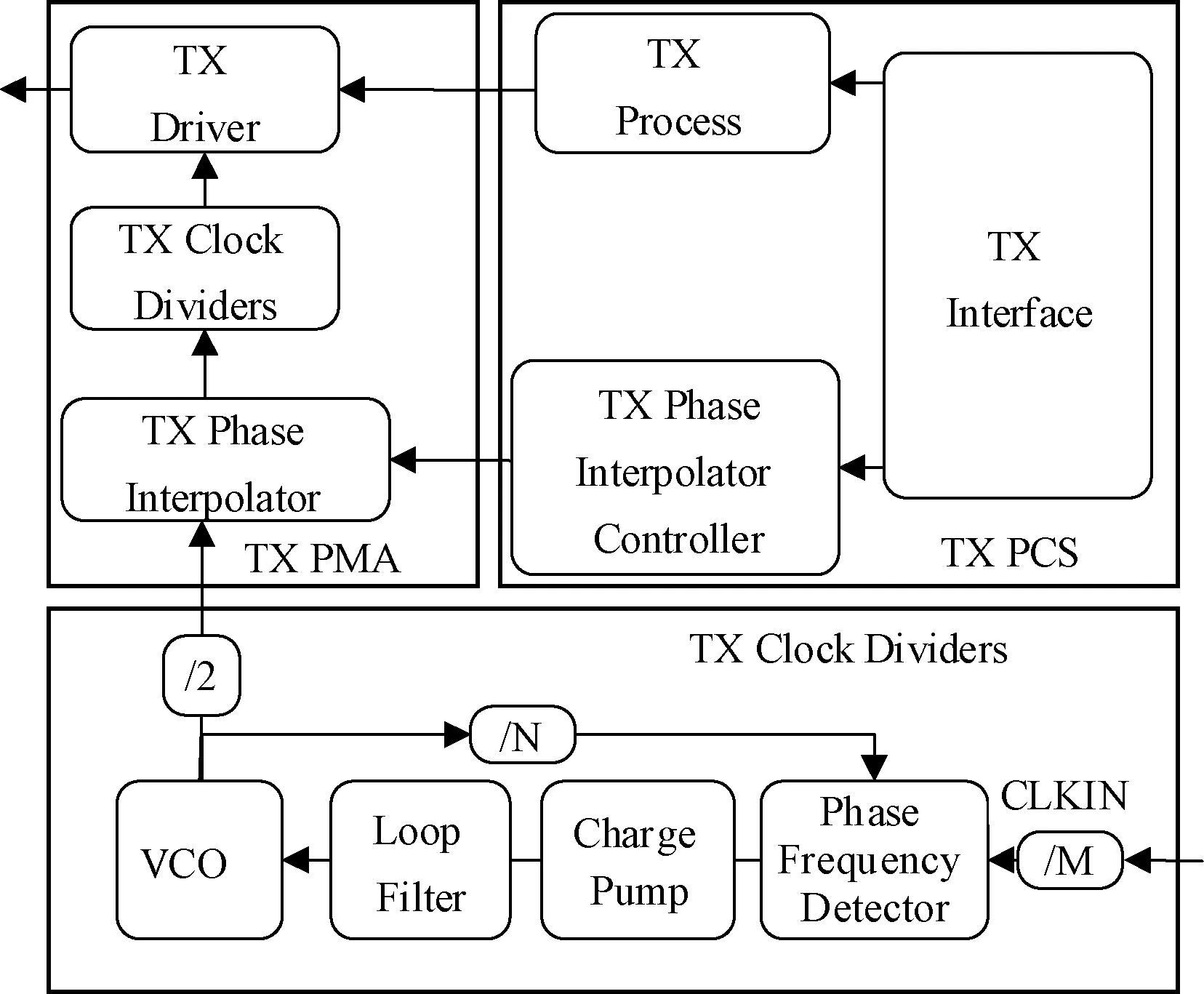

目前,大多TLK2711接口卫星模拟源均采用了TLK2711芯片来实现TLK2711接口,TLK2711芯片为并行数据输入,输出单路需要占用控制器19个IO管脚,而随着有效载荷的不断增加,所需TLK2711接口通道数也在不断增加,主控制器IO资源无法满足需求。为减少主控制器IO资源的使用,提出了使用Xilinx高速收发器来实现TLK2711接口,单通道TLK2711接口仅占用一对差分IO管脚。

TX Driver为发送驱动;TX Process为发送程序;TX Clock Dividers为发送时钟分频;TX Phase Interpolator为发送相位插值;TX Phase Interpolator Controller为发送相位插值控制器;TX Interface为发送接口;Loop Filter为环路滤波;Charge Pump为激励;Phase Frequency Detector为相位频率检测器;VCO为电压控制振荡器(voltage controlled oscillator);CLKIN为输入时钟;TX PCS为发送物理编码子层(physical coding sublayer);TX PMA为发送物理媒介适配层(physical media attachment)图7 高速收发器发送框图Fig.7 Transmission diagram of the high-speed transceiver

TLK2711接口需支持接口线速率为1.6~2.5 Gbps在线调整,高速收发器IP核配置界面也提供了线速率1.6~2.5 Gbps可选,但对IP配置后只能使用设定的固定线速率,而需要更改接口线速率则需要更改IP配置界面相应设置并对工程重新进行编译固化程序,在设备的使用过程则需要通过不断地更新固件来实现,给设备的使用带来了极大的不便。现提出一种对接口线速率在线配置的方法,在设备无须掉电更新固件的情况下对TLK2711接口线速率进行调整。高速收发器数据发送框图如图7所示。高速收发器线速率由Clock Dividers、物理媒介适配层(physical media attachment,PMA)、物理编码子层(physical coding sublayer,PCS)进行配置。Clock Dividers按照线速率需求产生时钟信号;PCS根据输入数据控制调整输出数据时钟相位;PMA对经过PCS调整后的时钟信号进行分频后驱动串行数据输出。在线调整线速率需要修改上述模块寄存器的值,以输出相对应的时钟信号驱动串行数据输出。

Xilinx官方高速收发器IP提供动态配置接口(dynamic reconfiguration port,DRP)接口可选,该接口可对高速收发器内部寄存器进行动态重配置,因此可以通过该接口对上述介绍模块的寄存器进行重配置,以实现线速率的调整。但用户与模拟源设备交互采用以太网方式进行通信,无法直接对DRP接口进行控制。因此,依据DRP接口控制时序设计出了一种指令信息转DRP接口配置模块,由该模块接收指令信息后完成对寄存器值的修改,实现TLK2711接口线速率1.6~2.5 Gbps在线调整。

3 系统测试与实验结果

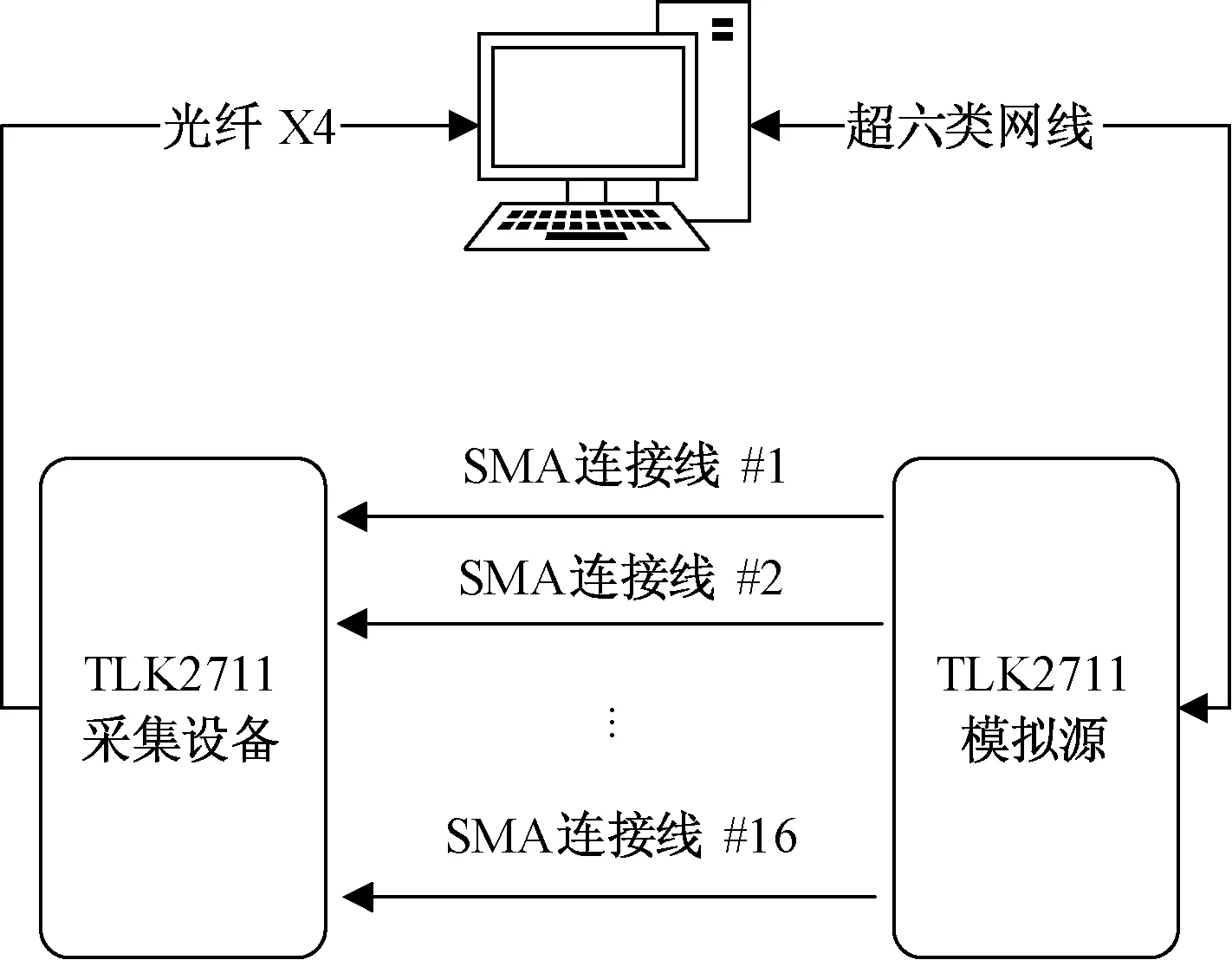

为了对高速大容量TLK2711卫星数传基带模拟源进行测试,采用本实验室自研TLK2711采集设备,该设备可将数据传输至上位机。上位机处理器为I7-9800K,内存为16 GB DDR4,操作系统采用Windows10 x64,内置一块PCIE3.0 光纤采集卡。测试框图如图8所示。TLK2711模拟源主要的性能指标分别为:SATA3.0控制器传输速率,数据连续传输性能,TLK2711接口传输性能,数据传输误码率。对该系统的上述功能指标分别进行实验验证与分析。

图8 速率测试连接框图Fig.8 Structure diagram of the rate test connection

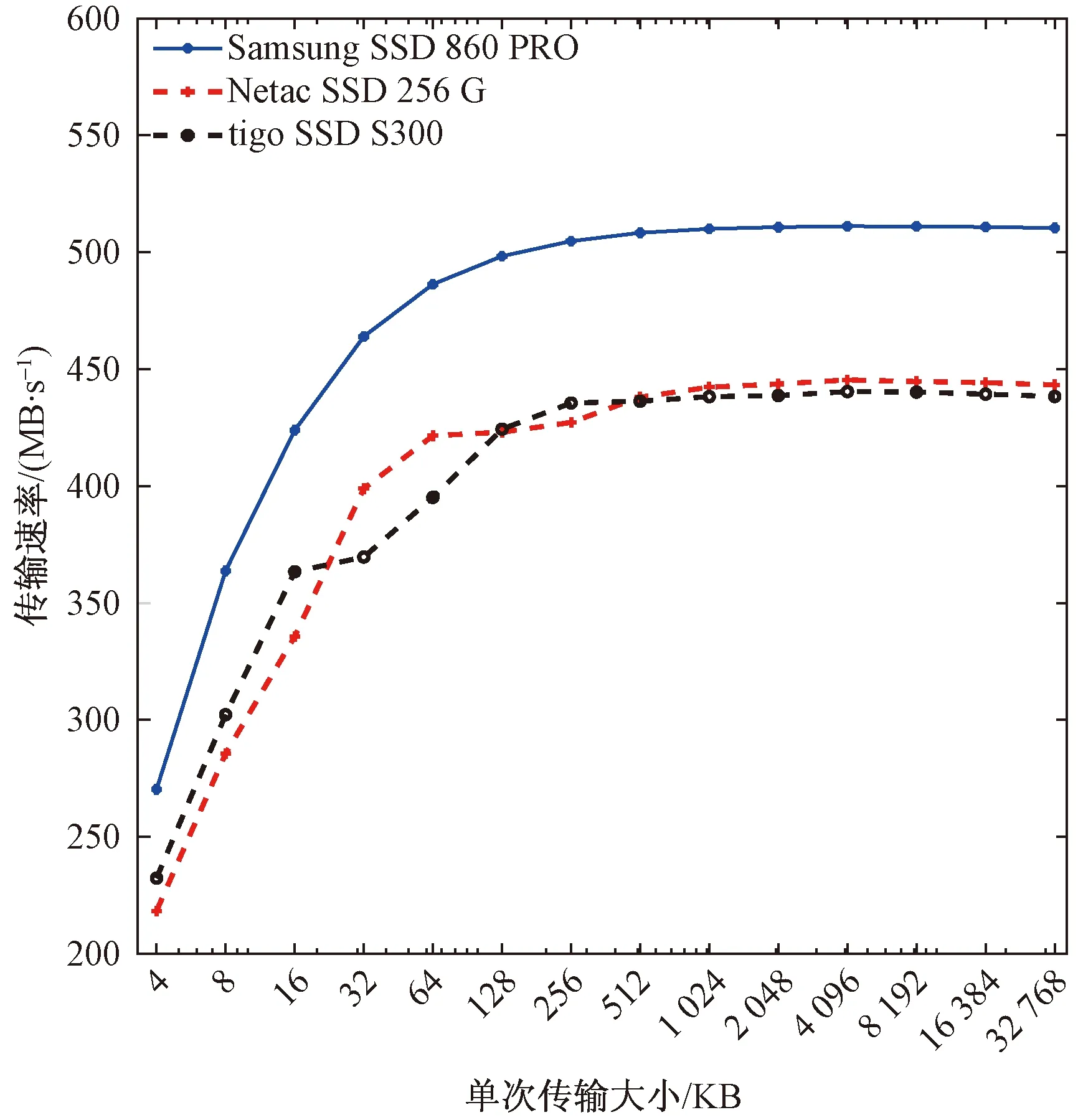

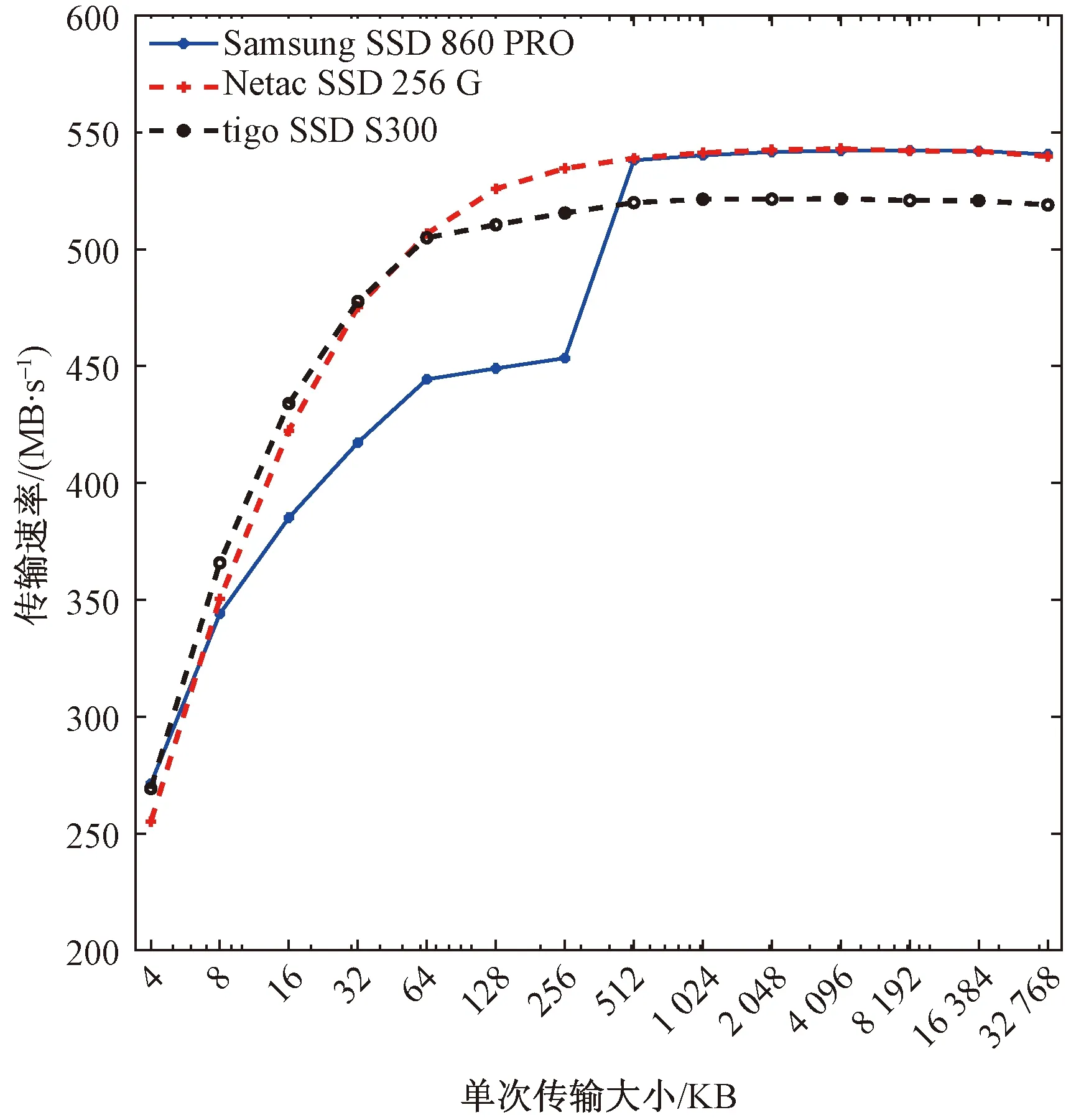

3.1 SATA3.0控制器性能测试

采用Samsung SSD 860 PRO、Netac SSD 256 G与tigo SSD S300等硬盘测试SATA3.0控制器性能。硬盘写入速率测试情况如图9所示,读取测试情况如图10所示,从测试情况可以看出,当单次数据操作在512 kB以上时,测试所用的三块硬盘读取速率均在520 MB/s以上,Samsung SSD 860 PRO的写入速率在500 MB/s以上,另外两块固态硬盘速率约为425 MB/s。实际使用时单路TLK2711接口最大线速率为2.5 Gbps,单路SATA3.0控制器为两路TLK2711接口提供数据,所需最大带宽为500 MB/s。因此,该控制器传输性能符合设计需求。在单次数据操作为32 MB时,Samsung SSD 860 PRO的平均读取速率高达540 MB/s,平均写入速度高达510 MB/s。因此,选用Samsung SSD 860 PRO固态硬盘作为SSD源载体,配合大容量DDR缓冲区,SSD源数据可以持续稳定的由TLK2711接口输出。数传基带模拟源采用8路SATA3.0控制器并行挂载,储存总容量达16 TB,读取总速率高达4.2 GB/s,写入总速率高达4.0 GB/s。相比文献[17]的方案,在存储容量与传输性能上均有显著提升。

图9 SATA3.0控制器写速率测试图Fig.9 Test graph of SATA3.0 controller write rate

图10 SATA3.0控制器读速率测试图Fig.10 Test graph of SATA3.0 controller read rate

3.2 数据连续性能测试

数据连续输出是基带模拟源的一个基本要求。在数据连续性能测试中,由一路SATA3.0控制器为两路输出接口提供数据,分别测试了两者在数据传输过程中,添加不同容量的多端口控制器模块时输出接口数据连续输出的性能。测试结果如图11所示。多端口控制器容量小于64 KB时,输出接口最大传输速率低于238 MB/s,小于TLK2711接口最大速率,不符合需求。多端口控制器容量大于1 MB时,TLK2711接口数据输出性能可达270 MB/s,满足使用需求。实验结果表明,多端口控制器容量大于96 KB时,使用SATA3.0控制器与多端口控制器相结合可使TLK2711接口连续数据传输速率符合需求,同时降低了16路TLK2711接口数据缓冲对FPGA 片上随机存储内存(random access memory,RAM)资源的占用。

图11 数据连续性能测试图Fig.11 Test graph of the continuous performance of data

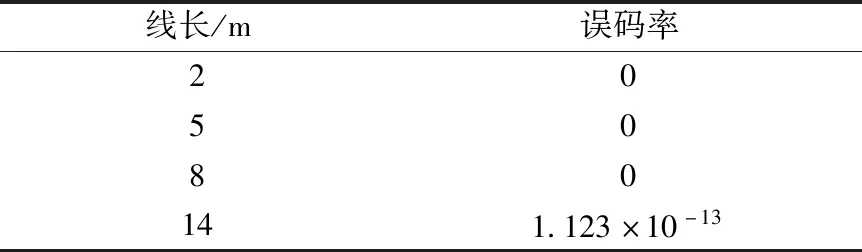

3.3 误码率测试

误码率是整个系统传输可靠性的一个重要指标。在误码率测试中,数据源模式配置为SSD源,SSD中的数据为预先写入的数据,TLK2711接口线速率设置为2 Gbps。测试时长为24 h时,不同长度SMA连接线的误码率情况如表2所示。由测试情况可知,SMA线缆在8 m以下时传输无误码;SMA线缆在14 m时传输出现误码。而在实际使用过程中SMA线缆最长只需4 m,符合设计要求。

表2 不同长度SMA线缆误码率Table 2 Bit error rate for SMA cables of different lengths

3.4 数据完整性测试

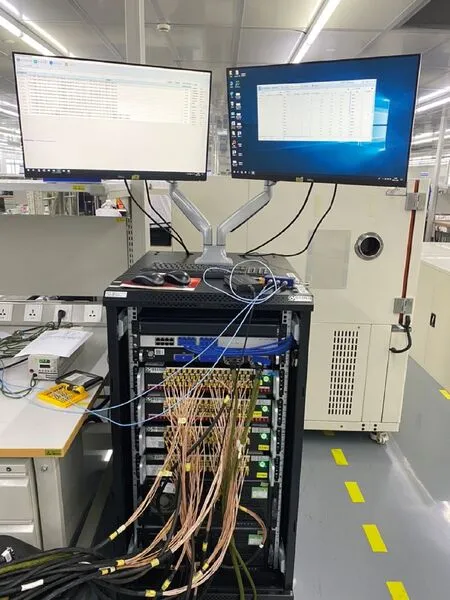

TLK2711模拟源可以采用以下方法测试数据完整性:①可以发送内部规律计数器由采集设备采集后在FPGA内部进行数据校验,判断数据是否连续;②数据源生成数据时打上了特定的帧头,上位机接收到数据之后可以通过对帧头的解析进行判断数据传输是否准确无误,并可对数据区数据进行校验测试误码率;③采用SSD缓存真实图像数据,上位机收到数据后进行图片显示,可以直观地查看图像是否失真。结合以上3种方法对数据传输进行校验,确保其传输可靠无误码。该系统在连续测试24 h中数据完整且无误码,目前已应用到多个型号数传分系统测试中,如图12所示,系统稳定可靠,为数传分系统的研制测试提供了保障。

图12 模拟源工作实物图Fig.12 Physical picture of the working generator

4 结论

针对现在卫星数传基带模拟源数据容量小、传输速率低的问题,提出了一种基于SATA3.0控制器与高速收发器的TLK2711接口卫星数传基带模拟源。SATA3.0控制器资源占用低,实现了8路SSD并行挂载并支持更多扩展,容量高达16 TB,并行速率高达33.75 Gbps。该系统基于SATA3.0硬盘控制器可以实现模拟源数据的大容量存储以及数据快速加载,在模拟数据预先写入的情况下可以做到设备开机即用,无须由上位机下载数据再进行数据发送,在测试过程中可节省大量时间。高速收发器实现的TLK2711接口极大地降低了IO资源的占用,使得系统高度集成,同时基于高速收发器的重配置实现了TLK2711接口线速率1.6~2.5 Gbps调整,能更好地适配不同线速率的数传分系统。目前该设备已应用到多个型号数传分系统测试中,系统稳定可靠,为数传分系统的研制测试提供了保障。