大尺寸高分辨率TFT-LCD垂直串扰的机理研究与改善

盛子沫,高玉杰,刘 信,冯 俊,朱 宁,陈晓晓,郭会斌,江 鹏

(武汉京东方光电科技有限公司,湖北 武汉 430040)

1 引 言

随着人们生活水平与消费水平的日渐提高,对于视听体验的要求也在逐渐攀升,这也促使了显示产业的不断发展。近年来,大尺寸、高分辨率、高刷新频率、窄边框等高性能显示器逐渐占领市场[1-4]。8 K超高清显示器因此应运而生,8 K与4 K显示器对比,在画质上有着质的提升,同时也能与5 G相结合,从而带来更多的感官体验[5]。

然而,高规格产品同时也会伴随更多的显示问题,垂直串扰就是其中一种,其现象为垂直方向某一区域的显示受到另一区域的影响,导致画面失真。垂直串扰由数据线与像素电极之间的耦合电容Cpd以及薄膜晶体管(TFT)关闭时的漏电流Ioff使像素电压发生偏移导致。8 K与4 K显示器相比,像素数量增大4倍,存储电容减小约80%,这就导致像素电压微小的变化会带来显示上的差异[6-7]。同时,由于8 K产品分辨率的提高,像素尺寸减小,布线越来越精细紧密,线宽间距越来越小[8],当线上有电流通过时,线间感应磁场的干扰变得尤为突出,像素自身以及像素之间的耦合作用会加剧。依上所述,像素电极与数据线之间的耦合电容是无法消除的,对于8 K产品,这样的耦合电容值较大,对垂直串扰影响显著。

本文主要研究了大尺寸高分辨率ADS列反转产品(8 K 60 Hz)垂直串扰产生的机理及改善措施。显示基板在彩膜侧接触背光源时,阵列基板上TFT沟道所受光照会被黑矩阵(BM)基本遮挡住,与阵列基板接触背光源相比,漏电流大幅减少[9]。本文通过彩膜侧与阵列侧基板朝向背光源时的不同现象,研究了漏电流和像素电极与数据线之间的耦合电容对垂直串扰的影响。再通过调整面板工艺参数,使漏电流与耦合电容达到抵消中和,为垂直串扰的改善提供了解决对策,对后续大尺寸高分辨率的工艺及产品设计具有重要的指导意义。

2 垂直串扰机理

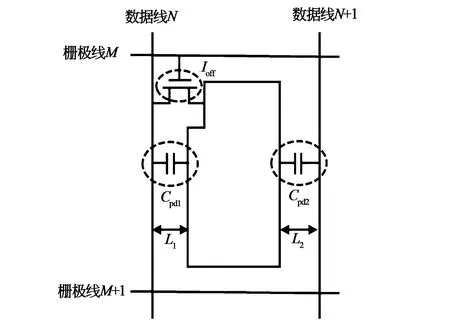

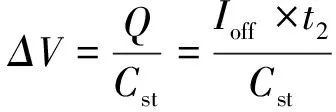

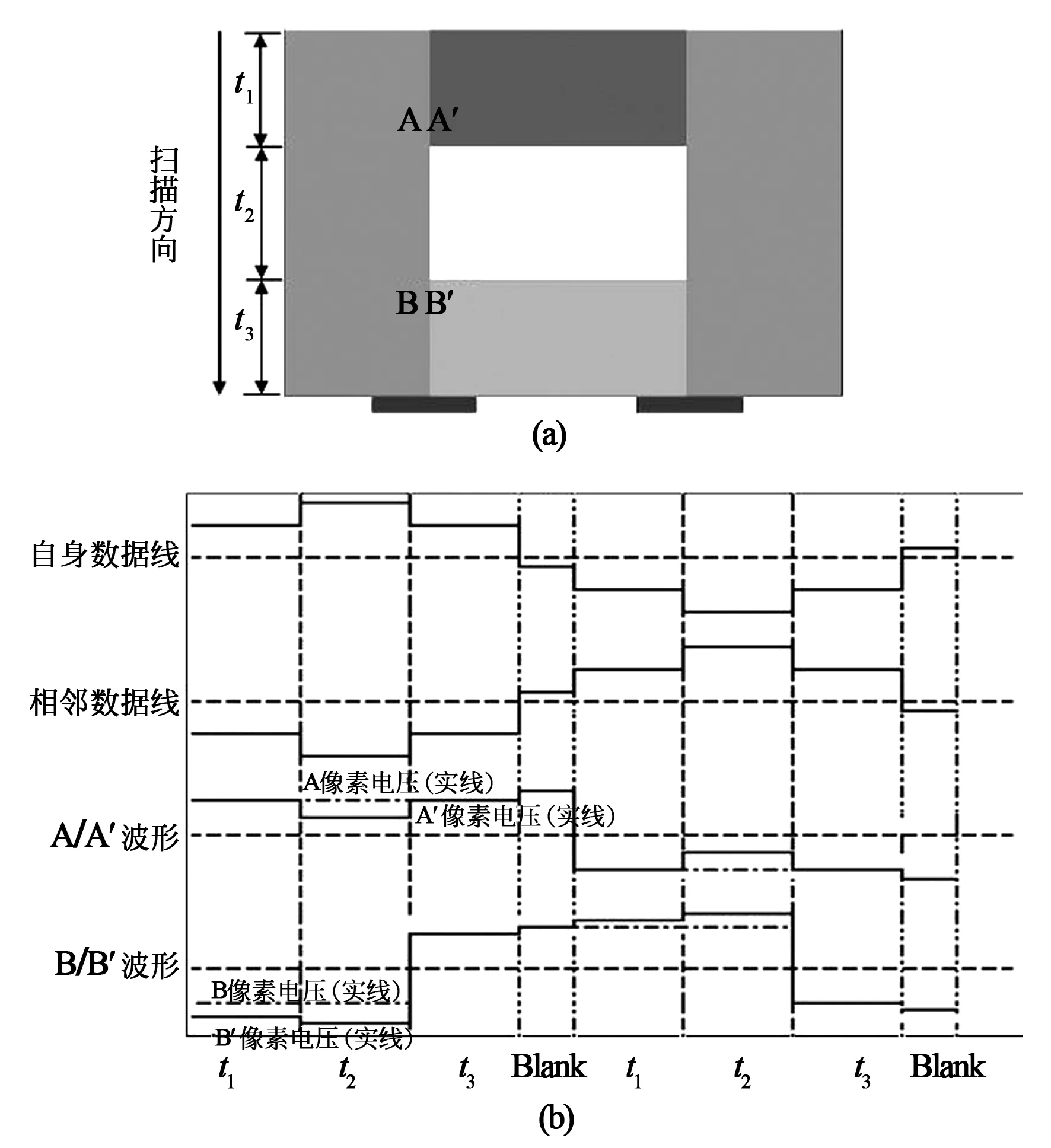

图1为TFT-LCD像素结构示意图。在像素充电完成后,TFT关闭,数据线与像素电极之间本该处于完全断开的状态,然而由于TFT存在漏电流(Ioff),当数据线与像素电极存在压差时,会通过漏电的方式使像素电压发生变化。另外,由于像素电极(2ITO)与数据线之间存在电容Cpd,当给其他行充电时,数据线信号会发生变化。2ITO与自身数据线N的距离为L1,与相邻数据线N+1的距离为L2,定义2ITO与数据线的交叠面积为L2ITO Overlay(L2ITO OVL),则:

图1 TFT-LCD像素结构示意图

(1)

自身数据线电压发生变化引起的像素电压变化,称为自耦合,记为Cpd1;反之,相邻数据线带来的像素电压变化称为互耦合,记为Cpd2。因此,垂直串扰主要有两种发生机理,一是漏电流机理,另一种是电容耦合机理。下面以ADS列反转产品来说明垂直串扰的产生机理。

2.1 漏电流机理

图2为基于TFT漏电流的中间白窗口垂直串扰的现象及波形。沿栅极线的扫描方向,前端发白,后端发黑。对于A-A′,t1阶段为像素充电,t2阶段为中间白块的充电时间,数据线电压处于高电平。由于TFT漏电流的存在,同极性的数据线会向像素电极漏电,导致A′区域像素电压升高,与A相比发白;同理对于B′区域,在t2阶段,像素电极会向反极性的数据线漏电,导致B′像素电压低于B,表现为发黑。

图2 TFT漏电垂直串扰的现象(a)及波形(b)

假定白块电压下的漏电流为Ioff,白块的扫描时间为t2,则在高电平的作用下,流进A′和B′的电量:

Q=Ioff×t2,

(2)

假定TFT-LCD的存储电容为Cst,像素电极2ITO的面积为S,栅绝缘层GI厚度为d1,绝缘保护层PVX厚度为d2,则有

(3)

在高电平阶段,A′和B′像素电压的变化:

(4)

由上式可见,Ioff越小,Cst越大,ΔV越小,垂直串扰的现象越轻。

2.2 电容耦合机理

像素电极与数据线耦合电容的影响作用与2ITO与数据线的交叠面积有关,当2ITO与数据线的交叠面积为负值时,自身数据线的电压变化对像素电压的耦合拉动作用较大(Cpd1>Cpd2);反之相邻数据线电压变化的耦合作用大(Cpd2>Cpd1),两种耦合作用现象不同。

2.2.1 自耦合

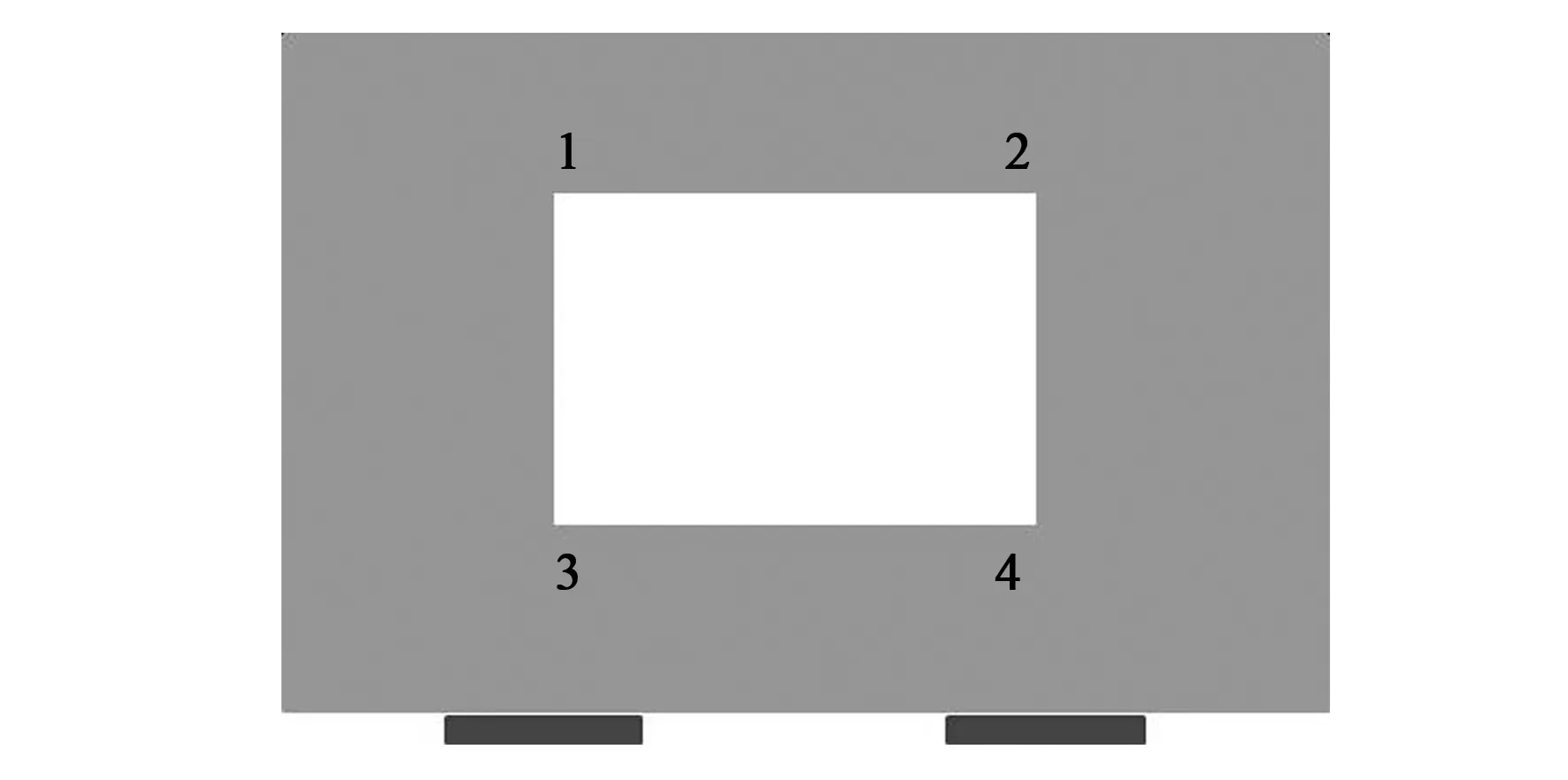

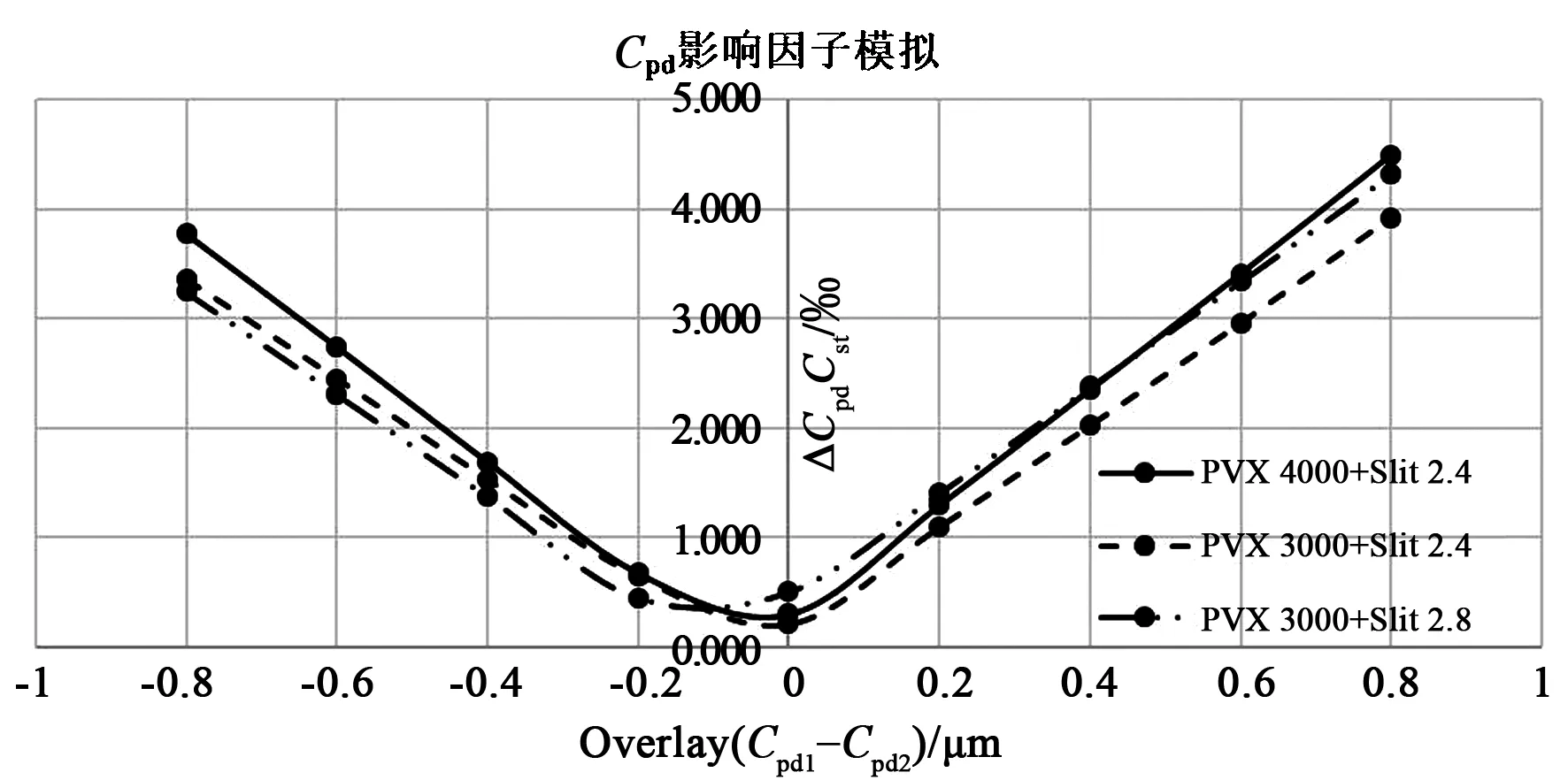

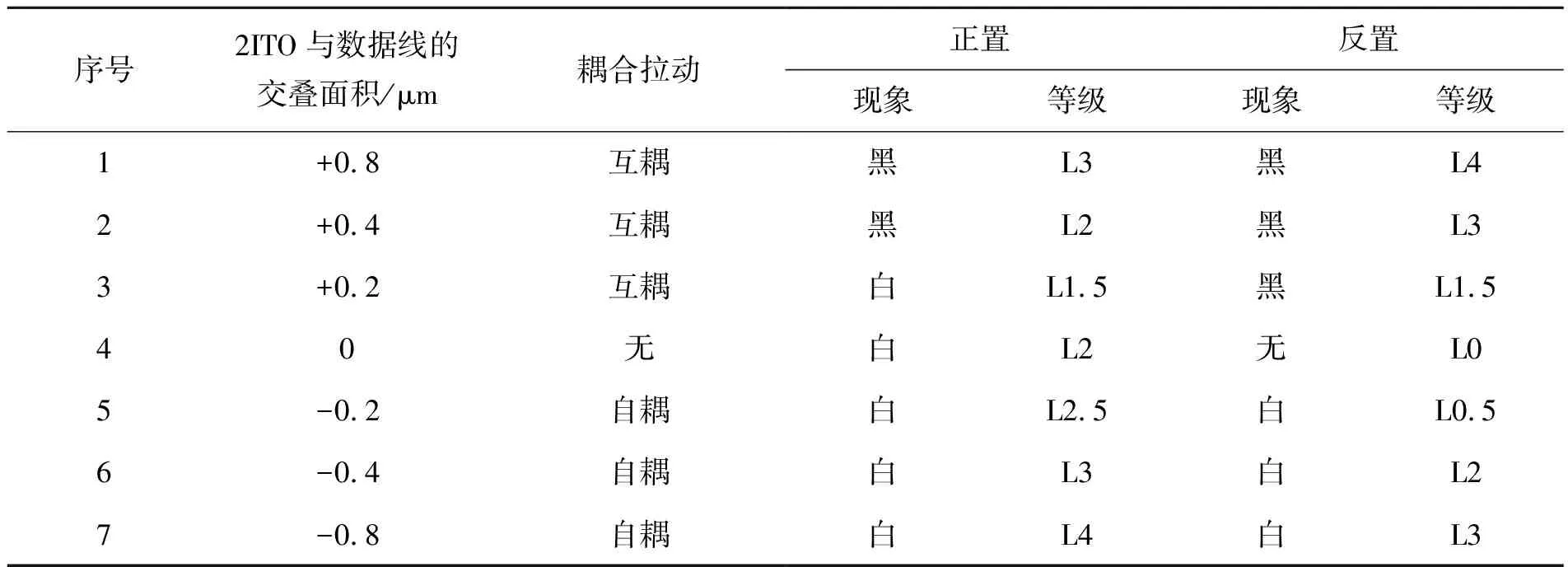

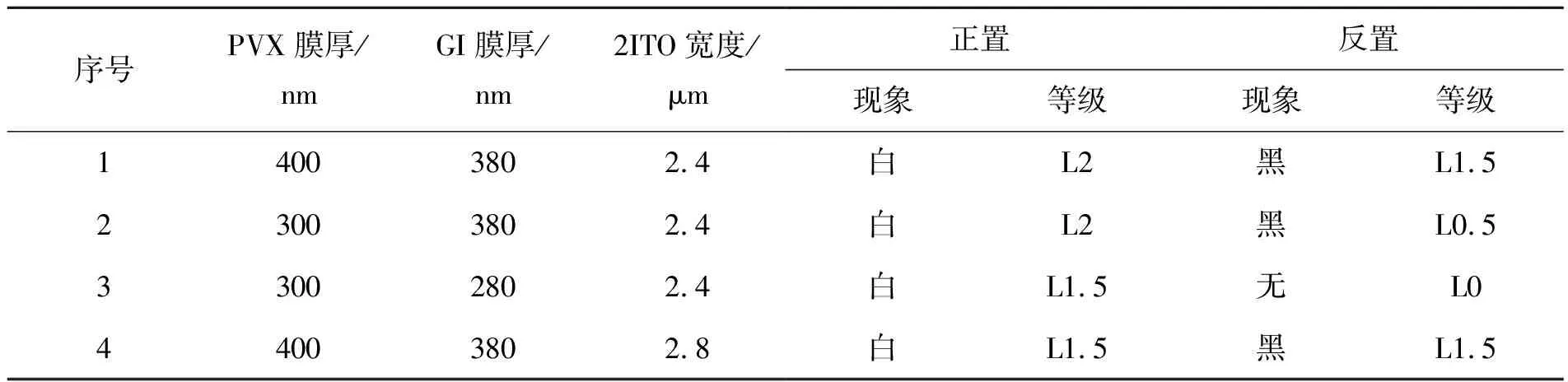

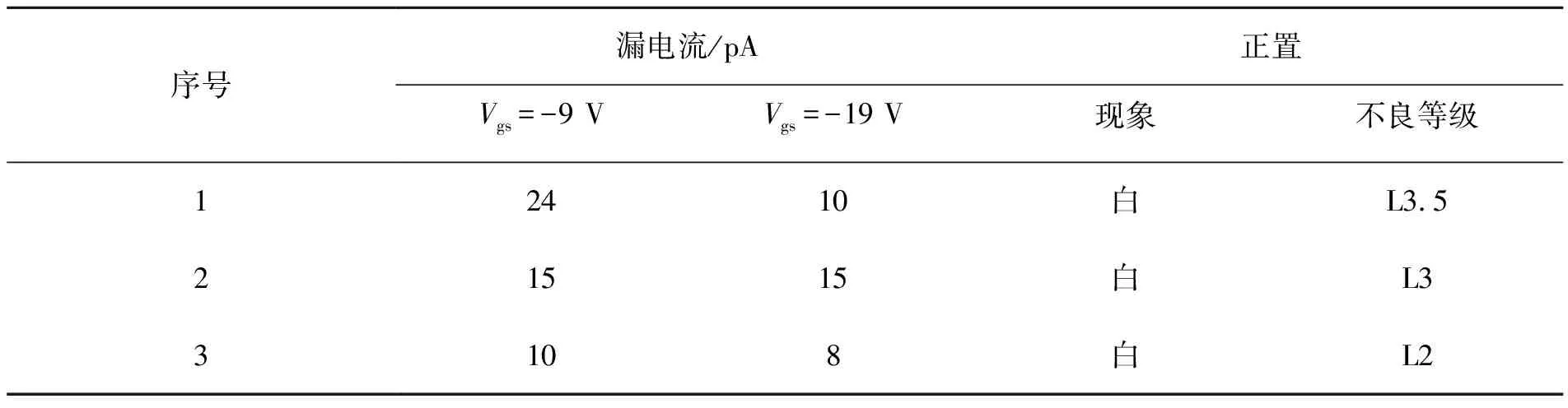

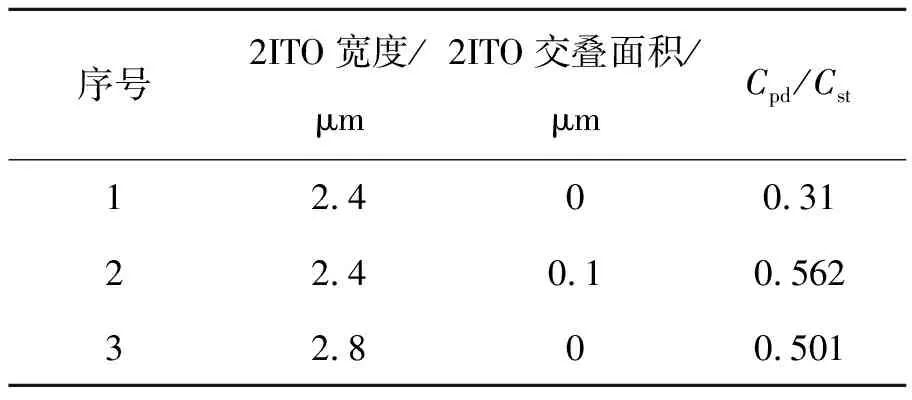

图3为基于自耦合的垂直串扰及波形。此时,L1 图3 基于自耦合的垂直串扰的现象(a)及波形(b) 2.2.2 互耦合 图4为基于互耦合的垂直串扰及波形。此时,L1>L2,2ITO与数据线的交叠面积为正值。对于A′区域,t1阶段像素充电结束后,TFT关闭,由于相邻数据线为相反极性,t2阶段时,相邻数据线给白块区域充电时,电压瞬间跳变到相反极性的高电平,在电容耦合的作用下,A′区域的像素电压向靠近Vcom方向耦合跳变,与A区域相比表现为发黑;同理,对于B′区域,在t1和t2阶段,受相邻数据线相同极性的电压跳变影响,像素电压被拉高,导致B′区域与B相比整体表现为发白。 图4 基于互耦合的垂直串扰的现象(a)及波形(b) 无论自耦合或互耦合占主导,其本质均为数据线电压跳变带来的耦合电容Cpd的影响,其影响程度为: (5) Cpd1与Cpd2差值和2ITO与数据线的交叠面积相关,2ITO与数据线的交叠面积越小,PVX和GI厚度越小,2ITO宽度越大,耦合电容的影响程度越小。 实验样品为大尺寸8 K 60 Hz的模组产品若干,均为GOA(Gate Driver on Array)产品。 使用Techwiz软件进行Cpd仿真模拟。Cpd影响因子有Cst、2ITO与数据线的交叠面积,模拟时输入产品的相关参数,可得到在Cst相关参数改变时,Cpd大小和2ITO与数据线的交叠面积变化的关系曲线。 将试验样品的彩膜侧和阵列侧分别朝向背光源,并规定阵列侧朝向背光源为正置,彩膜侧朝向背光源为反置,同时规定中间白框的4个角为1~4号点位,如图5所示。反置时,TFT不受光照影响,漏电流基本可忽略,观察并记录正反置各点位垂直串扰的现象和等级。 图5 垂直串扰的点位 4.1.1Cpd影响因子模拟 图6模拟了PVX厚度以及2ITO宽度变化时,Cpd影响程度随2ITO与数据线的交叠面积变化的关系曲线。OVL为负值时,2ITO离自身数据线较近,表现为自耦;反之为互耦。由图中可以看出,互耦方向的斜率较自耦大,即,互耦的影响程度大于自耦;而随着PVX厚度的减小以及2ITO宽度的增大,Cst也不断增大,正向与负向的斜率均减小,这说明互耦及自耦的影响程度均下降;同时,当2ITO宽度由2.4 μm增大到2.8 μm时,像素电极的宽度也在增大,其距离数据线的宽度减小,这就导致曲线的顶点向左平移,最低点为-0.2,即当2ITO与数据线的交叠面积为0时,整体表现为互耦。 图6 Cpd影响因子模拟 4.1.2Cpd对垂直串扰的影响 如上文所述,样品反置在背光源点灯时,基本可排除漏电流的影响,像素电压仅受Cpd的拉动。表1为不同2ITO与数据线的交叠面积样品,正反置点灯时,点位1垂直串扰的现象和等级。由表1反置现象可见,互耦现象表现为上黑下白,而自耦表现为上白下黑;当耦合拉动方向一致时,随着2ITO与数据线的交叠面积的不断增大,垂直串扰的等级不断加重;同时,当自耦与互耦方向均偏移相同的量时,互耦现象的不良等级高于自耦,与仿真模拟结果一致。 表1 不同2ITO交叠面积垂直串扰的现象 正置现象受漏电流的影响,由于漏电流拉动下的垂直串扰表现为上白下黑,现象与互耦的上黑下白可中和,相反的,会与自耦现象叠加,加重垂直串扰的不良等级。在保持该漏电流的水平下,交叠面积+0.2表现最优。然而,由于大尺寸产品漏电流与2ITO与数据线的交叠面积基板分布均一性难以控制,为增大工艺波动的允许范围,漏电流需进一步优化,同时需同步评估与漏电流水平相匹配的2ITO与数据线的交叠面积。 4.1.3Cst对垂直串扰的影响 由Cst的计算公式可知,Cst主要受栅极绝缘层(GI)、绝缘保护层(PVX)的厚度以及像素电极的宽度影响。本文研究了不同GI、PVX以及2ITO宽度时,垂直串扰的现象及等级,同时,为探究Cst增大时对于Cpd及Ioff的影响,表2中的样品并未刻意管控2ITO交叠面积。由表2可知,由于反置时的现象发黑,与Ioff的影响相抵消,因此Ioff的影响程度为二者加和。当PVX及GI的总厚度为780 nm时,漏电流的影响等级为L3.5,而Cpd的占比为L1.5;当PVX及GI的总厚度不断下降至580 nm时,漏电流的等级下降为L1.5,同时反置现象完全消失,Cpd的影响完全消除。当2ITO的宽度由2.4 μm增大到2.8 μm时,Cst也会同步增大,此时漏电流的影响等级为L3,而Cpd导致的串扰等级依然为L1.5。这是由于当2ITO宽度增大时,像素电极与数据线的整体距离也会发生改变,导致模拟曲线整体左移,互耦合的影响增大,因此Cpd导致的串扰等级不变。因此,当Cst增大时,Cpd与Ioff的影响程度均会降低。 表2 不同存储电容时垂直串扰的现象 当PVX厚度为300 nm,GI厚度为280 nm时,样品无论是正置和反置,垂直串扰的严重程度都最低。然而,由于GI厚度280 nm,会增大源漏极与栅极的静电击穿风险,且PVX减薄时,样品光学特性也会随之改变,因此选择4#条件PVX厚度400 nm,GI厚度380 nm,2ITO宽度2.8 μm作为存储电容的最佳工艺。 4.1.4Ioff对垂直串扰的影响 为探究Ioff大小对于垂直串扰的影响,本文在适当调整半导体层镀膜工艺条件的基础上,制备不同漏电流的样品,并严格控制2ITO的交叠面积,将Cpd的影响降至最低。观察样品正置时,垂直串扰的现象及等级。 TFT的漏电流由栅极关态电压和源极电压共同决定[10]。在本实验样品中,栅极关态电压为-8.5 V,灰阶255的正负帧数据电压分别为0.5 V和15.1 V,灰阶63的正负帧像素电压分别为5.22 V和10.38 V。由上文机理可知,点位1的漏电流主要受t2阶段灰阶255的影响,因此漏电流Ioff主要受Vgs为-9 V和-19 V的影响。由表3可知,当-9 V漏电流减小,而-19 V漏电流增大时,不良等级下降幅度较小;只有当第三组试样中,-9 V和-19 V的漏电流同时减小时,垂直串扰的不良等级才会明显降低。因此,选择3#工艺参数作为漏电流的最佳条件。 表3 不同漏电流时垂直串扰的现象 由于大尺寸产品2ITO交叠面积以及漏电流等各项参数在基板上的分布无法做到完全一致,因此需尽可能减小漏电流、增大存储电容Cst,以增大工艺的波动范围。由上文的分析可知,Cst条件选择PVX厚度400 nm,GI厚度380 nm,2ITO宽度2.8 μm;漏电流条件选择第三组试样中的工艺参数。由于a-Si产品漏电流继续下降的空间较小,因此需在最佳Cst与Ioff的条件下选择较优的2ITO与数据线交叠面积,以期尽量降低正置时漏电流的影响。 由上文Cpd的影响分析可知,当2ITO交叠面积为负值时,会与漏电流现象有叠加作用,当交叠面积大于+0.4时,现象以Cpd拉动为主。表4为在最佳Cst与漏电流的条件下不同2ITO交叠面积中心值样品的不良率,其中,正置串扰等级为L2.5时,判定为不良。由表4可知,当交叠面积由+1逐渐增大到+4时,正置发黑现象逐渐加重,不良比率不断增大;而交叠面积0和+1相比,不良比率差异不大,但现象有差异。交叠面积为0时,正置垂直串扰现象多为发白,而交叠面积增大到+1时,现象多为发黑。这是由于2ITO宽度为2.8 μm,交叠面积为0时,与2ITO宽度2.4 μm,交叠面积为+1时的Cpd影响程度一致(表5),因此,2ITO宽度增大所带来的Cpd影响程度即可有效改善漏电流带来的垂直串扰。受大尺寸基板膜层分布均一性所限,垂直串扰现象不可能完全消除,但在最佳漏电流、存储电容与2ITO交叠面积条件下,垂直串扰不良比率可由55.6%下降到4.2%。 表4 最佳漏电流及存储电容条件下不同2ITO交叠面积时的垂直串扰不良率 表5 不同2ITO宽度和交叠面积时的Cpd/Cst的模拟值 垂直串扰的产生,受漏电流和耦合电容Cpd的影响。对于大尺寸高分辨率产品,其存储电容小,布线密,像素电压更易受到拉动而产生串扰。本文通过软件模拟了Cpd的影响因子,再结合不同2ITO交叠面积样品的反置现象确定Cpd的影响程度,同时通过改变各项工艺参数确定最佳存储电容及漏电流条件,最后在最佳存储电容及漏电流条件下探讨与之匹配的2ITO交叠面积。在PVX厚度400 nm,GI厚度380 nm,2ITO宽度2.8 μm,2ITO与数据线交叠面积为0,漏电流为3#条件时,不良比率由最初的55.6%下降至4.2%,画质大幅改善。本文研究成果对于后续大尺寸高分辨率产品的工艺、设计思路及解决问题的方式有重要的指导作用。

3 实 验

3.1 模拟分析

3.2 正反置实验

4 结果与讨论

4.1 垂直串扰的影响因素

4.2 垂直串扰的改善对策

5 结 论