FPGA下的数字中频信号处理平台设计与实现研究

李 娜 徐思武 吴嘉欢

(同方电子科技有限公司,江西 九江 332000)

0 引言

FPGA(Field-Programmable Gate Array),即现场可编程门阵列,其集成度高、可靠性强且便于设计,是数字信号处理和数字电路设计的第一选择。FPGA作为数字中频系统的连接桥梁,依靠DSP管理系统实现统一管理,由于它的可编程性,可以通过加载不同的软件来实现不同的功能,因此在进行中频信号的数字化处理时,可以降低对射频前端滤波器及放大器的性能要求,使数字信号处理变得更简单、快速。然而该处理方式却对ADC、DAC和时钟性能有更高要求[1]。该文中处理系统的高精度载波信号通过DAC芯片来发送,采用ADC直接采样来接收信号,同时使用双核ARM来处理和控制数据流,以此保证系统的高度集成和运行可靠,相关研究陈述如下。

1 总体设计方案

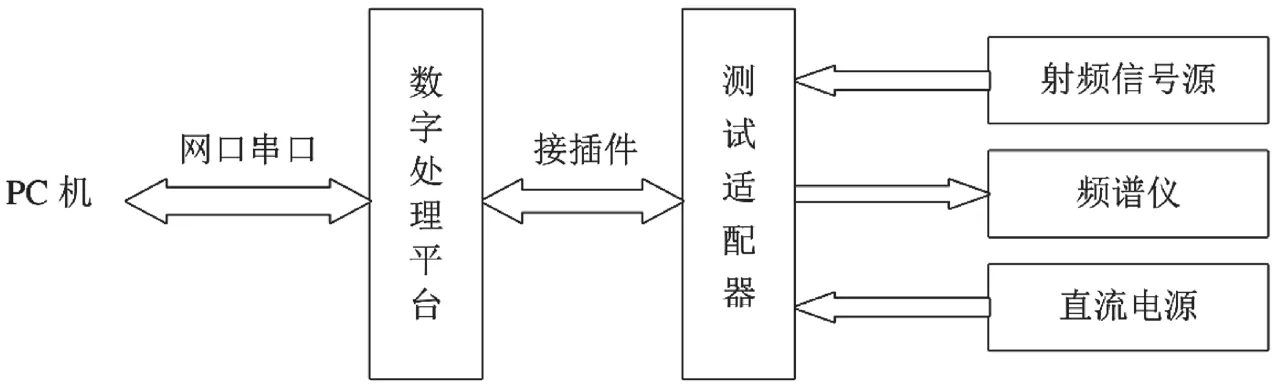

该处理平台在设计方向上要求能够支持高效率、高质量的数字变频、数字采样以及数据信号、接口处理等功能。系统电路的主要构成部分包括电源和音频电路、中频发射和信号采样电路、时钟综合电路以及数字处理电路。其中,中频发射电路使用的是数字基带上变频方式,440 MHz载波信号通过DAC芯片进行发射,以ADC直接采样实现信号接收。数字处理电路主要包括PPC、SOC和DSP1及DSP2共4种。这些电路中的双核ARM主要功能是控制、搬运及处理数据流,FPGA主要负责对中频数字信号进行处理,其总体设计框架如图1所示。

图1 总体设计框架

2 主要功能模块设计

本该系统的核心功能为FIR滤波器、中频信号发射、采用和数据处理,相关电路设计具体如下。

2.1 FIR滤波器系数设计

利用MATLAB,通过输入fdatool来打开滤波器设计工具,然后按实际需要合理设置滤波器的类型、采样频率和截止频率等关键参数。滤波器的实现过程其实就是卷积的实现过程,如果以x(n)表示待滤波信号,h(n)表示滤波器系数,那么卷积过程可以用下面的关系式来表示,即。基于FPGA技术的FIR滤波器实现一般需要经过三级流水线,在第一级中对输入信号进行延时处理,以此保证信号和滤波器系数相乘;在第二级中将滤波系数与输入信号进行相乘;在第三级中则将前面得到的乘积进行累加,最后得到结果。

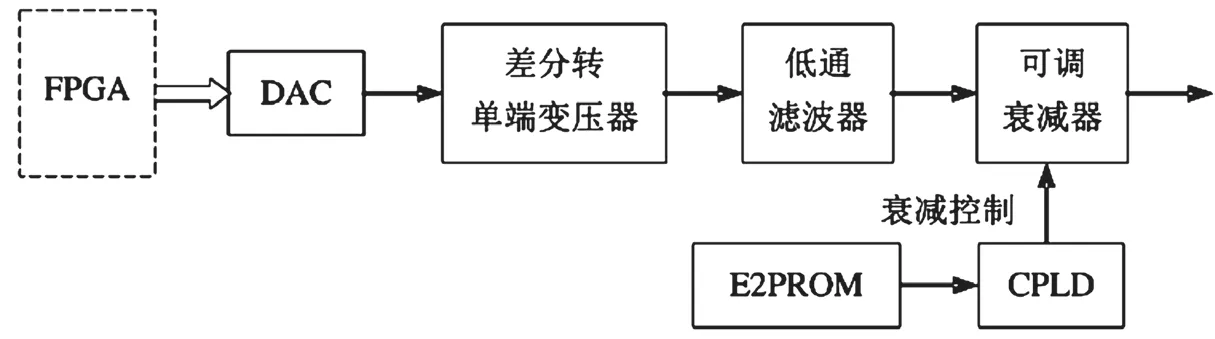

2.2 中频发射电路设计

中频发射电路框架如图2所示。该系统的中频信号发射电路中包括射频变压器、抗混叠滤波器和PI型衰减器、高速DAC等核心部件,其中射频变压器具有阻抗匹配、直流隔离、共态抑制等功能;看混叠滤波器主要对无用的信号进行衰减和滤除,消除混叠对数据采集的影响;PI型衰减器利用电压来调整控制负载功率,抑制信号反射;高速DAC即直接电缆,它采用线对屏蔽及总屏蔽的方式实现信号的高速传输[2]。该设计中DAC使用AD9142,16 bit,采样率为1 280 MHz,工作模式为正交上变频。FPGA工作中,160 Msps信号中内插了原采样率为40 Msps的基带信号并且传送给AD9142。在8倍插值下,AD9142将基带信号转化为1 280 Msps,然后再与440 MHz频率的NCO进行先乘后加,最后搬移至440 MHz载波中。

图2 中频发射电路框图

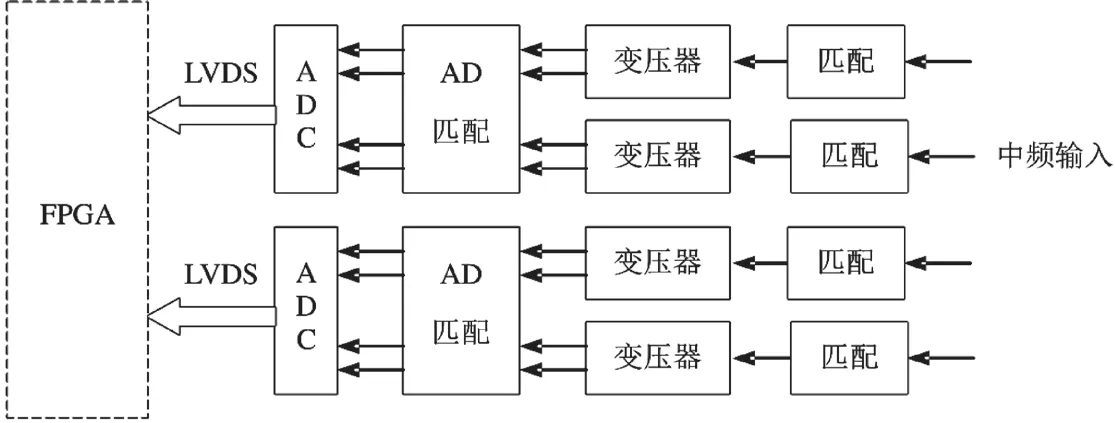

2.3 中频采样电路设计

该设计的中频采样电路中主要包括ADI高速模数转换器、单端转差分射频变压器以及与这些部件相匹配的前端电路。实际工作期间,前端匹配电路主要负责信号的交流耦合和匹配,以此确保输入电压的驻波比性能[3]。高速ADC设计为双通道14 bit,采样率为160 Msps,对载波信号采样后生成强度为40 MHz的信号,通过FPGA下变频到基带,同时滤除带外信号(约5 MHz),最后按4倍方式进行抽取并生成采样率为40 Msps的基带信号。数字中频信号的接收采样电路设计框架如图3所示。

图3 数字中频信号接收采样电路框架示意图

2.4 数字处理电路设计

该中频信号处理平台的数字处理电路中使用了集成电路芯片SOC,它同时内置FPGA以及ARM双核处理器。双核ARM与DSP1之间存在替代关系,其中一个ARM核心以裸跑形式替换DSP1,而另一个ARM核心独立支持VxWorks操作系统的正常运行,以此替代PPC[4]。该设计的数字处理电路用到了P1010芯片,含P1010芯片的处理器的频率可以达到800 MHz,而其运行功率仅1.1 W,具有极大的经济性,同时电路中还包括DDR2、DDR3、DSP1、DSP2及FPGA。DSP1使用TI公司的新型高性能单核定点DSP-TMS320C6455,它通过并行总线EMIF与FPGA实现实时通信。以SOC芯片为主的数字中频信号处理电路在实际使用时应按照图4所示的流程来进行。

图4 SOC芯片的数字中频信号处理电路流程图

从图4可以看出,该SOC数字处理电路中使用了ARM双核处理器对P1010和C6455进行了替代。ARM中包括容量为512 MB、位宽为32 bit的DDR3,ARM由SPI FLASH开始启动,同时加载FPGA与DPS2。在SOC数字处理电路中,FPGA和ARM经SOC内置的双口RAM以及硬件中断实现数据通信。ARM的2个核心ARM1和ARM2共同享有DDR3的外置存储器,它们之间的通信也通过双口RAM来进行[5]。

3 系统模块及功能设计

3.1 系统核心模块

该设计平台的PPC软件运行在P1010中。SOC中的其中一个ARM核心支持运行VxWorks6.9操作系统。DSP1与DPS2都属于裸跑状态,无须操作系统支持[6]。中频信号处理系统主要包括启动模块、加载模块、驱动模块和应用模块。

其中启动模块中的bootrom启动信息使用Flash来读取,以此导引VxWorks6.9系统;系统加载模块通过读取到的相关启动数据信息推进系统运行;驱动模块以操作系统内核中的处理模块为基础,经以太网将串口与外部进行连接,实现对外部数据信息的顺利加载和收发;应用模块由各类不同功能的软件构成,可按需配置软件。

3.2 系统模块主要功能

系统模块主要功能包括模块初始化、上电自检和软件升级,具体内容如下。1)模块初始化功能:PPC启动之后,DSP1、DSP2和FPGA等相关程序相继加载,此时开始对时钟芯片AD9517进行初始化,时钟芯片锁定之后,PPC继续对ADC和DAC芯片进行初始化处理[7]。2)上电自检功能:指的是PPC在通电运行过程中可以对自身的外置存储器运行状态、性能等进行自我检查和测试。PPC通过读取并核对时钟芯片寄存器的值数和锁相环状态,进而准确判断时钟有无失锁问题;通过对ADC、DAC芯片寄存器值进行读取并核对,如果发现不匹配则自动进行重新配置,同时做好相关信息记录,如果多次匹配无效则做出预警反馈。系统运行中ADC芯片可以实现自行检测,FPGA在读取到PN码序列测试码后进行校验,以判断FPGA和ADC芯片之间的接口有无故障存在[8-9]。PPC可以数据文件的形式将所有判定后的告警信息上传记录到系统中的FLASH芯片中,有助于今后的随时读取和分析。3)软件升级功能:软件需要定期升级、更新,以保证最佳的使用性能,这个功能主要通过PPC小系统来实现,常见的处理方法为以测试接口为程序写入网口,将FPGA、DSP等主要软件存放在容量较大的FLASH芯片中,当PC与PPC通过网口进行连接后,检测软件是否有升级版本,按需进行升级。软件升级完成后,利用PC内置的FTP协议将软件文件由PPC直接写入FLASH中,然后再下发复位命令,重启后相关应用功能得到更新。

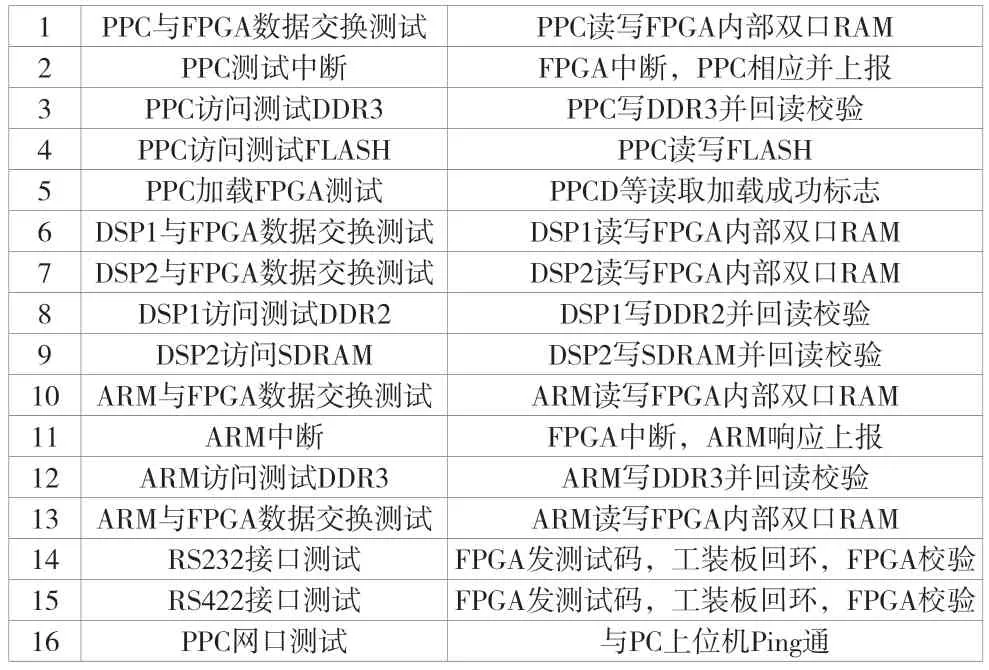

4 测试系统设计

为验证该系统平台各模块的实际性能,该文在模块测试前专门设计了测试适配器,同时满足对相关对外接口的适配性测试。模块内部各种芯片利用自身的自检测功能进行测试。芯片的外部接口功能测试可使用测试工装和频谱分析仪配合信号源进行检测[10-11]。系统测试的流程图如图5所示,所有的测试项目及采用的具体测试方法见表1。测试结果证实了该设计能够有效适用于对数字中频信号的处理。

表1 测试系统

图5 模块测试框图

5 结论

综上所述,该文所设计的数字中频信号处理平台以高性能FPGA为关键支持,它具有嵌入式SOC的主要功能和高速率、高质量的数字信号处理能力,并可支持系统的稳定运行,还可以通过加载各种软件实现功能扩展。通过实际的运行测试,可见该设计结构合理、各模块功能可靠,不仅可以满足在线升级需要,还能够准确、快速地进行故障检测和定位,适用于各类数字通信工程的实际需要。