电磁兼容接地分析与设计

袁胜军, 阳川, 李博识, 贺伟, 廖啟龙

(重庆赛宝工业技术研究院有限公司, 重庆 401332)

0 引言

EMC设计的复杂性主要体现在干扰源抑制、 切断耦合路径和增强敏感对象的抗干扰能力3 个方面[1]。 好的接地设计对于以上3 个方面均起到良好的效果, 如振荡器下局域化地平面设计可以为来自振荡器的杂散电容(电场) 提供终止平面, 从而降低振荡器作为骚扰源向外发射RF 能量, 完整的平面设计能够降低电流回路面积和公共地阻抗耦合,从而降低电磁发射、 提高敏感电路的抗干扰能力。本文从PCB 地平面设计、 底盘接地、 电缆屏蔽层搭接和滤波器搭接设计4 个方面分析不良搭接方式的等效天线模型, 对电磁兼容接地设计进行探讨。

1 电子产品中的电磁骚扰等效天线

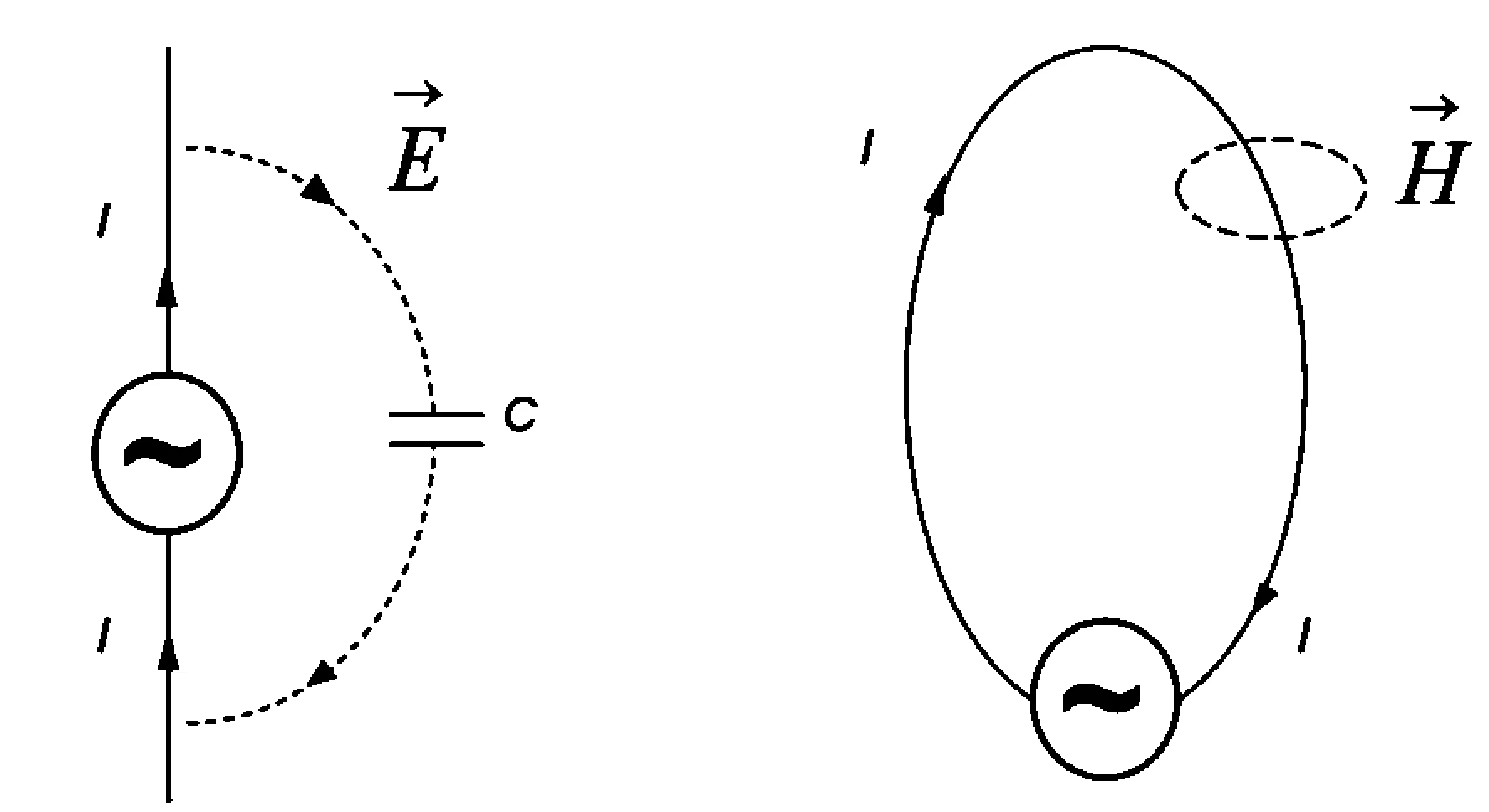

天线具有两种转换功能, 即将电压和电流转换成电磁波并传输到空间中, 或者将空间中的电磁波转换为电压和电流信号。 在电子产品设计生产过程中, 电路板和线缆线束必然存在许多等效天线, 如图1 所示。 等效天线不仅具有发射特性, 也具有接收特性, 在EMI 测试中作为发射天线会导致辐射发射超标; 在EMS 测试中充当接收天线, 导致产品出现功能性能问题。

图1 偶极子天线与环形天线

电子产品电磁兼容测试一般为3 m 法远场测试, 偶极子天线的电磁辐射大小由公式(1) 模型表达, 环形天线的电磁辐射大小由公式(2) 模型表达[2]。

式 (1) - (2) 中: Z0——波阻抗, 其值近似为120 π;

I——被测样品等效天线中电流大小;

L——等效偶极子天线长度;

A——等效环形天线面积;

D——等效天线距离测试天线距离;

λ——等效天线中电流信号的波长。

从公式中不难发现, 降低天线长度/面积、 信号频率可有效地降低电磁发射水平。

2 电磁兼容接地设计不当及其等效天线

2.1 接地分类

接地设计通常可分为3 类, 即安全接地、 信号接地与电磁兼容接地。 安全接地通过低阻抗通路将产品机壳或底盘与大地或代替大地的船体、 机体相连, 通常没有电流流过; 信号接地则是信号电流返回其源的低阻抗通道, 可细分为信号返回和电源返回, 与产品的电磁兼容性息息相关; 电磁兼容接地是出于电磁兼容设计而要求的接地, 包括屏蔽接地、 滤波器接地[3]。 由于安全接地线载流的唯一时刻是设备故障时使设备安全, 通常没有电流, 本文主要讨论信号接地与电磁兼容接地。

2.2 PCB 接地设计不当的等效天线分析

随着电路板集成度越来越高, 速度越来越快,对PCB 布局走线提出了更高的要求。 常见的电磁兼容问题主要是因为元器件布局、 地平面设计和高速信号走线不合理导致[4]。

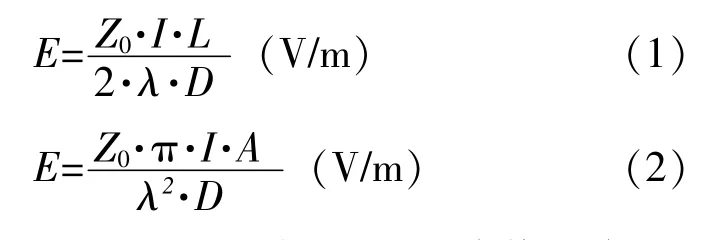

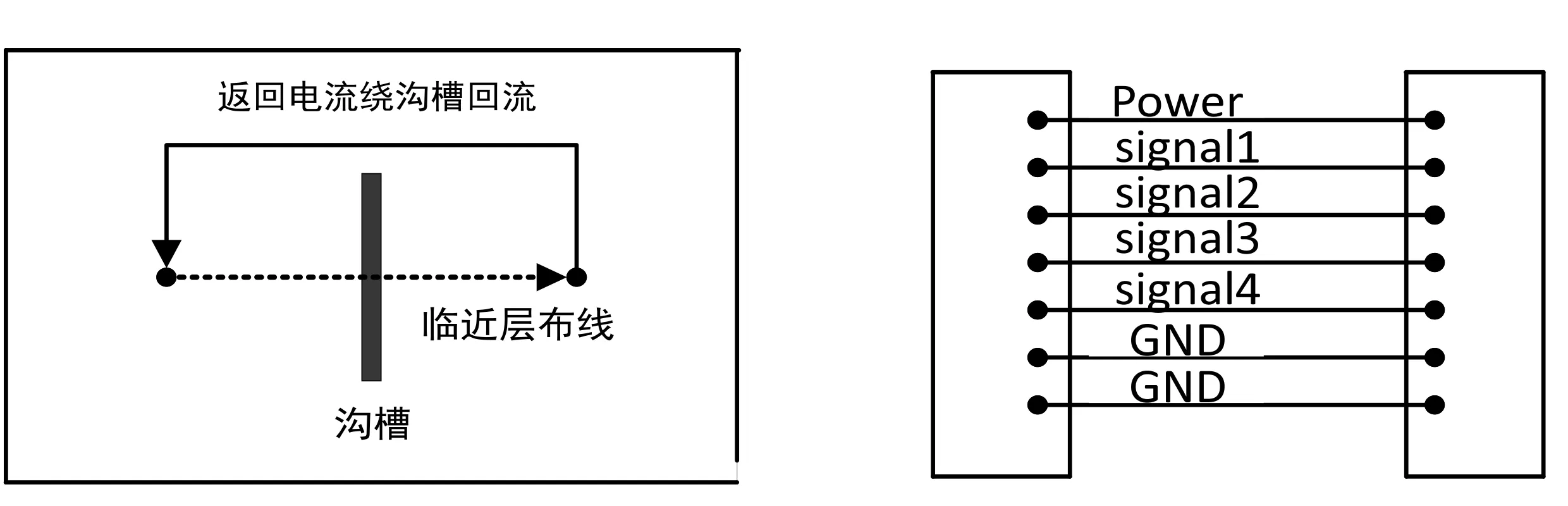

未按照功能、 信号特性划分的PCB 布局将导致导线过长, 由于导线间存在容性耦合, 将不同电路模块的噪声信号耦合至其他电缆线路并对外发射噪声; 电源/地平面设计不合理导致电源/地平面的寄生电感增大, 过大的寄生电感带来更大的噪声电压, 噪声电压驱动PCB 走线、 线缆线束, 等效为偶极子天线导致传导、 辐射超标; 未进行阻抗匹配、 跨地平面的高速信号走线将带来更大的反射噪声及信号回路面积, 导致辐射发射超标。 常见的具有一定隐蔽性错误的PCB 地设计如图2 所示。

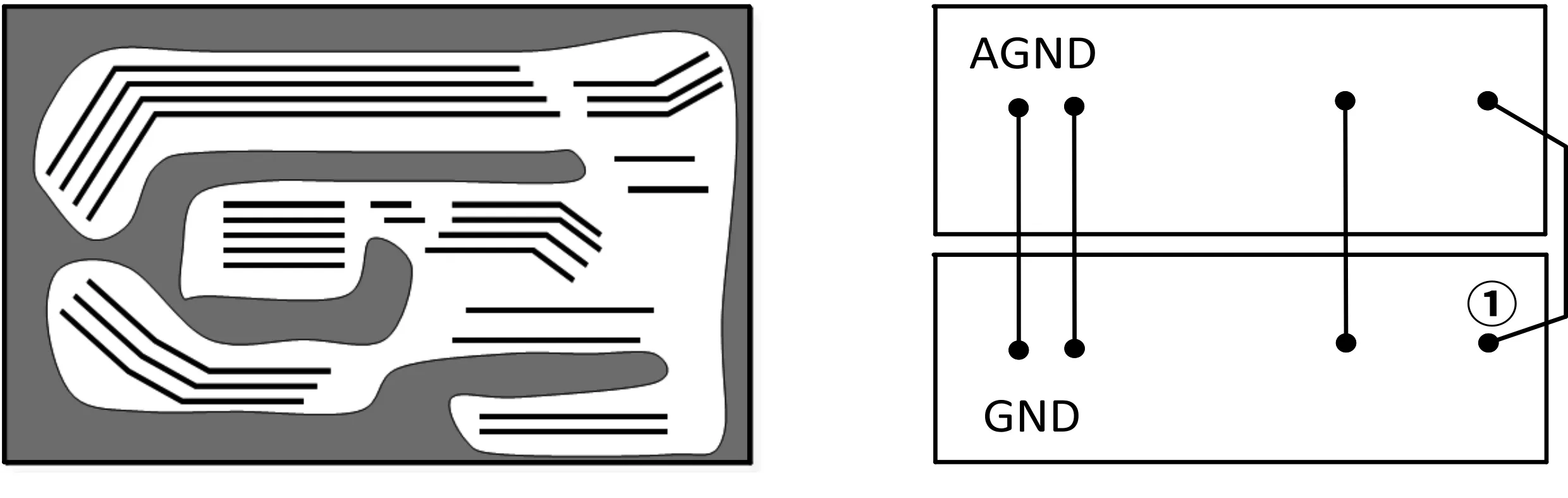

图2 隐藏寄生天线的PCB 地设计

图2a 所示的地平面设计, 因无法减小回路面积, 故不能减小电磁辐射。 由于大量的信号走线没有进行伴地设计, 所以也无法减小轨线间的串扰。图2b 所示的地平面分割设计, 2 组地平面间通过导线①单点地连接; 由于3 组信号跨地平面走线且未通过电容近距离搭接, 所以可等效为3 组环形天线并对外产生电磁辐射; 由于3 组信号均通过导线①进行信号返回, 导线①上存在较大的噪声电压, 所以在带来公共地阻抗耦合的同时,噪声驱动两组地平面也形成等效偶极子天线, 对外产生电磁辐射。 图2c 所示的接地平面在信号返回电流路径上存在沟槽, 信号返回电流被迫绕沟槽回流, 形成很大的回流面积, 等效为环形天线对外产生电磁辐射。 图2d 所示的PCB 间排线连接, 由于电源线、 信号线均未采用伴地设计,同理于图2b, 所以可等效为5 组环形天线、 公共低阻抗耦合, 地噪声驱动两侧地平面等效成偶极子天线对外产生电磁辐射。

2.3 底盘接地不当的等效天线分析

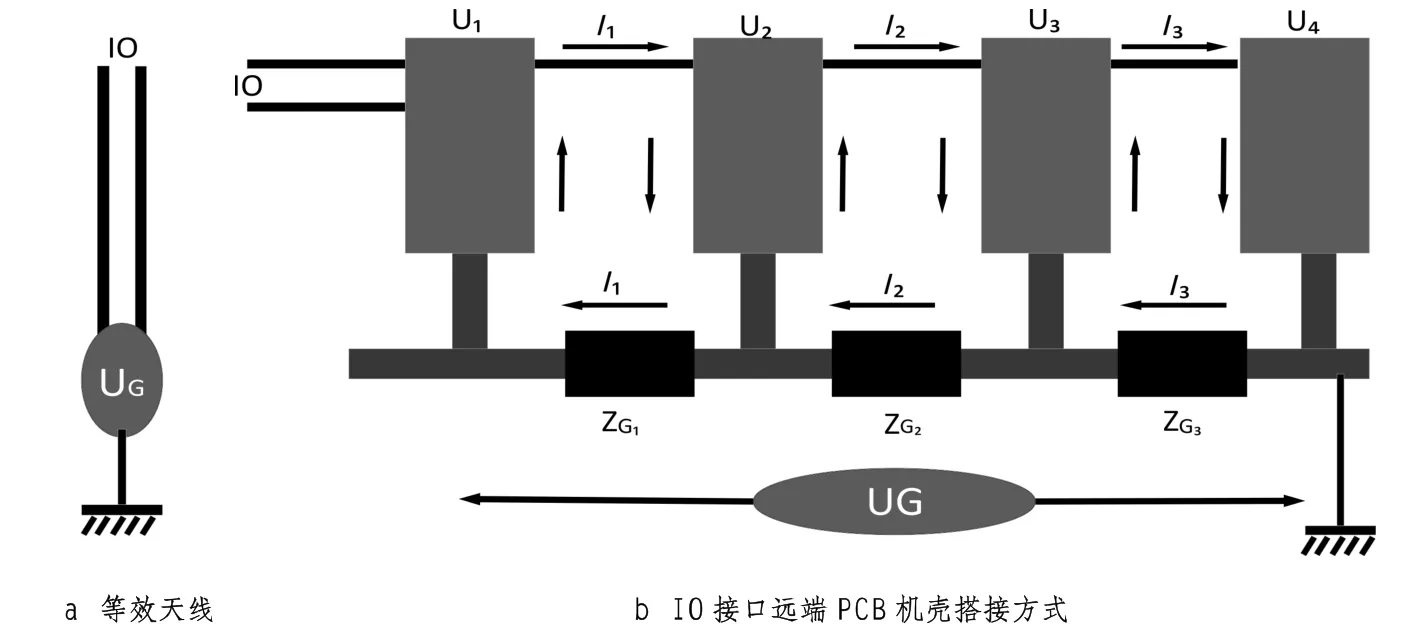

所有的地, 无论是地走线还是地平面, 均具有一定的阻抗。 流经工作地中的电流主要有两个方面: 1) 信号回流; 2) 电源回流。 当电流流过时, 产生电压降。 若PCB 与机壳搭接不当,将带来共模电压, 共模电压驱动与PCB 连接的电缆, 形成等效偶极子/单极子天线, 对外产生电磁辐射。 常见的不正确的搭接方式如图3 所示。

如图3b 所示, PCB 地平面采用IO 电缆远端的单点搭接产品机壳。 由于PCB 地平面存在阻抗,所以工作电流产生的地电位差UG驱动IO 接口电缆等效为单极子天线, 对外产生电磁辐射。 UG的大小由公式(3) 所示的模型表达, ZG为地阻抗。

图3 底盘接地不当及其等效天线

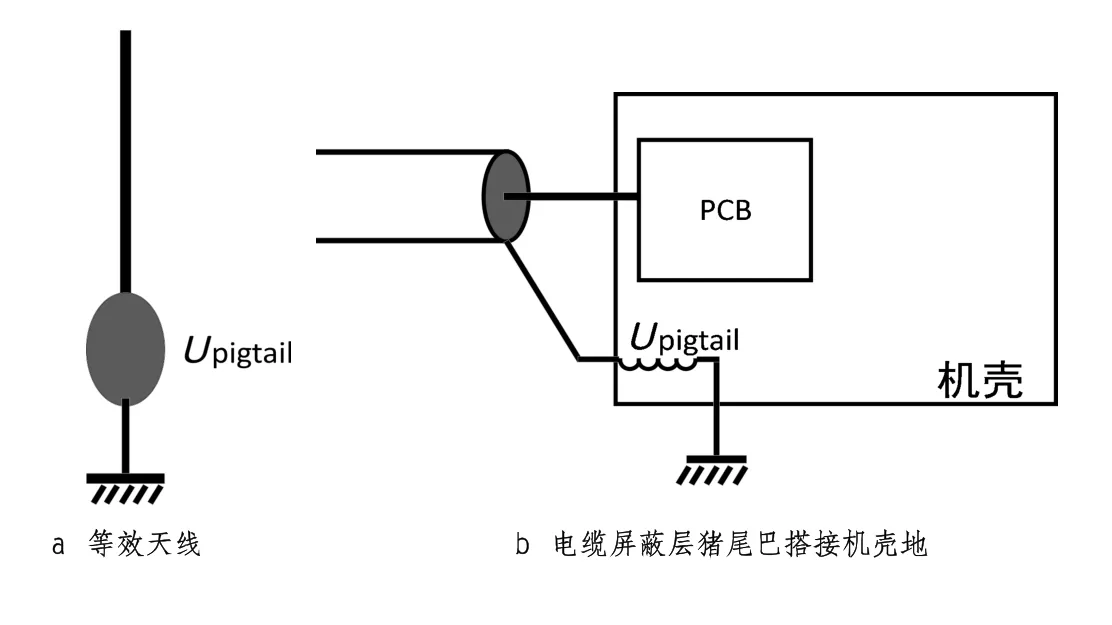

2.4 电缆屏蔽层搭接机壳地不当的等效天线分析

电子产品出于防电磁辐射和提高抗干扰能力等因素的考虑, 信号线往往使用屏蔽电缆设计。 若使用过程中, 电缆屏蔽层与金属机壳未采用360°搭接方式, 而将屏蔽层在接近产品信号端口的地方拧成猪尾巴状(Pigtail) 与金属机壳进行端接, 就会导致电磁兼容问题[5]。 屏蔽电缆猪尾巴效应示意图与其等效天线模型如图4 所示。

图4 屏蔽电缆猪尾巴效应及其等效天线

屏蔽电缆猪尾巴的存在, 相当于在屏蔽层上串联了一个数十纳亨的电感, 因屏蔽层电流的作用而产生一个共模电压。 随着频率的增大, 猪尾巴连接的阻抗也将增大, 使屏蔽电缆失去屏蔽效果。 图4展示了猪尾巴的屏蔽电缆形成辐射的原理, 即较大的阻抗形成较大的压降UPigtail, 该压降驱动屏蔽层变成了等效单极子天线, 对外产生电磁辐射。

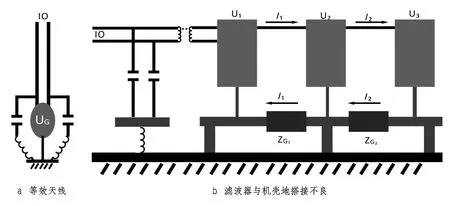

2.5 滤波器与机壳地搭接不良的等效天线分析

滤波器内部的共模滤波电容连接到滤波器的金属外壳上, 通过将滤波器的金属外壳直接安装在金属机箱上实现滤波电容的接地。 在图5b 的安装方式中, 滤波器的外壳没有与产品机壳地低阻抗搭接(如采用长导线连接), 共模滤波电容相当于通过高阻抗电感后与机壳地相连, 起不到滤波的作用, 其等效天线依然为单极子天线。

图5 滤波器搭接不良示意图及其等效天线

3 电磁兼容接地设计

在PCB 设计过程中, 接地是信号返回其源的低阻抗通道。 接地设计的根本目的主要体现在以下两个方面。

a) 信号返回其源的路径

首先, 这个路径必须足够的短, 否则其等效的环形天线将导致电磁发射和抗干扰能力的降低; 其次, 这个路径不能影响到电路的敏感单元, 不能通过已被污染的干扰电流较大的地走线。

b) 此路径必须为低阻抗

高阻抗将产生高共模电压导致产品发射超标。对于静电、 EFT 等外部共模干扰电流, 也需要设计其低阻抗返回路径, 控制其路径不能经过PCB 的功能区, 并保证路径的低阻抗, 共模电流流过高阻抗路径时将导致共模电流转为差模电压, 影响产品的可靠性。

底盘接地与PCB 地平面通常在一点或多点连接在一起, 接地点位置决定噪声的大小。 在有输入输出IO 电缆的PCB 情况下, 电路地与底盘在IO连接处低阻抗连接, 此时驱动共模电流到电缆上的电压理想情况下为0。 高频时为获得更低的接地电感, 需要多点接地。

屏蔽电缆电磁兼容问题多为屏蔽端接不良引起, 屏蔽端接需保证端接的连接阻抗非常低, 电缆屏蔽层与机箱金属壳体或底板有360°的接触。

滤波器使用过程中的性能更多地取决于其安装方式, 尤其要保证机箱壳体的低阻抗及滤波器到机箱壳体的低阻抗搭接, 其阻抗值必须远低于滤波器内共模滤波电容的阻抗值,为流过滤波器的共模干扰电流提供最佳的返回路径。

4 结束语

接地设计对产品电磁兼容性的影响很大, 并且无需任何额外的单位成本, 是电磁兼容设计的重点。 本文通过对PCB 地平面、 底盘接地、电缆屏蔽层搭接和滤波器搭接设计4 个方面分析不良接地方式的等效天线模型, 给出电磁兼容接地设计思路及分析方法。