宽带高效率二倍频器的设计

傅海鹏,郑玉学,陆 敏

宽带高效率二倍频器的设计

傅海鹏1,郑玉学1,陆 敏2,3

(1.天津大学微电子学院,天津 300072;2. 中兴通讯股份有限公司,深圳 518057;3.移动网络和移动多媒体技术国家重点实验室,深圳 518057)

针对共源二倍频器匹配电路版图面积较大和传统共基二倍频器变频增益低的问题,本文提出一种二次谐波短路的共基二倍频器电路.共基结构和共源结构相比输出电容较小使得匹配电路尺寸较小,同时在输入端引入二次谐波短路电路,有效提升了共基二倍频器的变频增益.该二倍频器由Push-push二倍频器电路和驱动放大器构成,其中前者用来产生二倍频信号,后者用来对二倍频信号进行放大输出以便驱动二倍频器的后一级电路.基于对晶体管偏置与二次谐波输出功率关系的研究,将晶体管偏置在AB类提升了输出功率和变频增益.输入端共模点接地减小了输入匹配的相位误差,提升了基波抑制和三次谐波抑制.驱动放大器采用共发射极放大器结构,输出匹配部分采用并联电阻变压器结构用于提升匹配带宽. 测试结果表明,在输入功率为2dBm的条件下,3dB 带宽绝对频率范围是13.8~23.2GHz(相对带宽50.8%),基波抑制带内优于32dB,功率附加效率达到19%(输出功率5.2dBm,直流功耗16mW).二倍频器芯片(核心区域,不含测试焊盘)面积仅为 0.245mm2.

二倍频器;Push-push;宽带;高效率

近年来随着Ku/K波段测距雷达的应用越来越广泛,雷达系统对频率源的性能要求越来越高[1-3].信号源是雷达系统收发机中的关键部分,随着工作频率逐渐升高到Ku/K波段,无源器件品质因数下降和有源器件寄生电容所占比例加大,使得宽频段和相位噪声性能优异的频率源的获得变得困难[4-5].倍频器可以将主频频率降低,这样就可以在低频设计宽频带和低相位噪声的频率源很大程度上提升Ku/K波段频率源的性能,同时降低设计难度.但是额外增加的倍频器电路造成了系统整体功耗增加和版图面积,低功耗和低成本的要求使得布局紧凑、宽带、高效率倍频器得到广泛研究[6-11].

倍频器电路分为有源倍频器和无源倍频器两大类,因为无源倍频器损耗大,谐波抑制差,在Ku/K波段几乎不采用.有源倍频器电路主要分为4类[12]:①基于混频结构的倍频器输出功率较低,同时基波抑制较差,额外引入混频器,版图面积较大,且多用于产生奇数次谐波[13];②基于单管非线性放大器的倍频器需要高功率的输入信号,谐波抑制较差[14];③注入锁定倍频器可以实现比较宽的频率带宽,但是输出功率较低[15];④基于Push-push结构的倍频器带宽较宽,同时输出功率较高[16-17].Tsai等[16]为了提升基波抑制和拓展带宽,在输入匹配部分引入补偿线优化马相巴伦的对称性.倍频器电路采用共源Push-push结构,但是共源结构的米勒电容较大,为了在输入端实现宽带匹配,需要在马相巴伦之后串联电感用于吸收共源放大器的输入电容,引入了额外的版图面积.Ye等[17]输入匹配部分采用中心补偿电容改善输入巴伦的对称性来提升带宽,同样的因为采用共源放大器结构,需要额外的串联电感来吸收输入电容,版图面积较大,为0.276mm2.Wan等[9]采用双平衡Push-push倍频器结构改善基波抑制,实现带内基波抑制高达44dBc.但是输入端需要混合正交耦合器来生成4路正交信号,在不采用驱动放大器的基础上,版图面积也为0.400mm2,十分不利于集成.为了解决共源Push-push二倍频器因输入电容过大导致匹配电路版图面积较大的问题,Mazor等[18-19]提出了共基Push-push二倍频器电路,共基电路输入电容较小,仅采用单个变压器就实现了良好的宽带输入匹配.但是输入端二次谐波处的阻抗使得共基结构的最大可用增益(maximum available gain,MAG)减小,进而导致二倍频器的变频增益较低,仅为-1.5dB.

针对共源结构版图面积较大和共基结构变频增益低的问题,本文对共基极放大器进行改进,提出一种二次谐波短路的共基极放大器,该结构相比共源结构来说输入电容较小,匹配电路仅需一个变压器即可完成,版图面积得到有效减小.同时二次谐波短路提升了共基结构的MAG,从而使得二倍频器的变频增益增加,输出功率升高.并基于该放大器结构,采用130nm SiGe BiCMOS工艺,设计出一款新型堆叠共基Push-push二倍频器电路.该电路采用共基极放大器作为二倍频器输入级,相比共发射极放大器来说,共基极放大器在保证带宽的同时易于匹配,可以有效减小版图面积.另外输入匹配巴伦中心接地有效减小相位误差,保证差分信号的对称性,提升基波抑制.采用源极负反馈的发射极放大器作为输出级,在提高输出功率的同时进一步提升基波抑制.

1 二次谐波短路共基极放大器电路设计

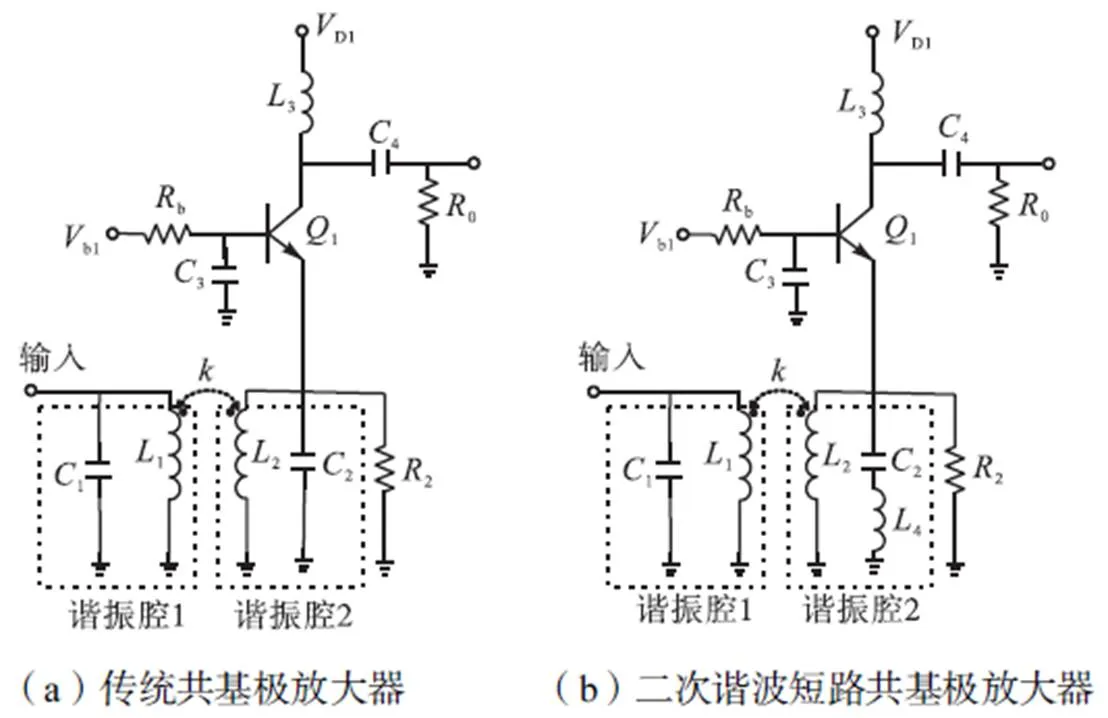

传统共基极放大器如图1(a)所示,输入匹配采用变压器匹配网络.该网络由两个耦合的谐振腔构成,是电感1和2之间的耦合系数.电容1和初级线圈电感1并联形成谐振腔1,电容2和初级线圈电感2并联形成谐振腔2.电感3和4构成输出匹配网络,用于最大功率传输.二次谐波短路共基极放大器如图1(b)所示,相比图1(a),在输入匹配部分,增加一个电感4,4和2串联形成二次谐波短路电路,谐振在二次谐波处.

图1 共基极放大器

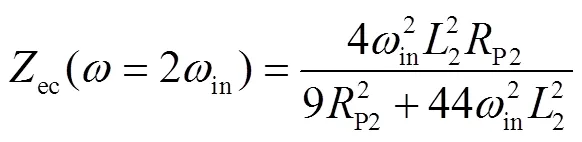

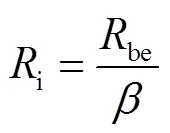

传统共基极放大器的发射极等效输入阻抗ec为

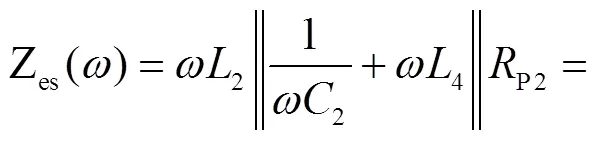

二次谐波短路共基极放大器的输入阻抗es()为

比较式(2)和式(4)可以发现,二次谐波短路共基极放大器发射极输入阻抗在二次谐波处的阻抗为零.

图2 共基极放大器小信号等效模型

共基极放大器的输入电流和输出电流基本上相等,可以认为电流增益约为1.输入电阻i为

相应的电压增益V表示为

这个电压增益是共基极放大器的电压增益,但是因为电压源输入阻抗的原因,输入的信号并没有全部被放大.考虑输入信号源电阻的电压增益称为源电压增益VS,其表达式为

可以看到源电压增益因为输入信号的源电阻s而减小,尤其当s较大时,源电压增益会出现显著减小.对于两级堆叠共基极倍频器来说,第一级电路的输出电阻是第2级放大器的输入源电阻.共基极放大器的输出阻抗o表示为

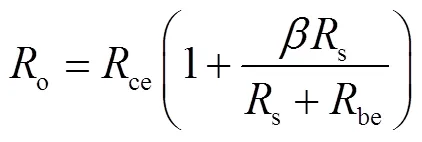

假设源电阻s=0,此时o=ce,这个是晶体管的本征输出电阻.晶体管的电流放大系数较大,这样源电阻s会使输出阻抗o相比本征电阻ce增加了ces/(s+be),使第2级放大器电压源增益进一步下降.改进型Push-push堆叠共基极放大器输入端电感4和电容2形成二次谐波短路,这样减小了第1级放大器的输出阻抗,提升了堆叠共基极放大器的增益.改进型共基极放大器和传统共基极放大器的最大可用增益(MAG)如图3所示.可以看出二次谐波短路电路的引入提升了共基极放大器在Ku/K波段的MAG.

图3 共基极放大器的最大可用增益

2 Push-push堆叠共基极二倍频器电路

2.1 二倍频器电路拓扑

考虑到雷达系统对杂散的高要求,二倍频核心电路采用堆叠形式Push-push二倍频器电路.堆叠结构的输入输出之间的隔离电容相当于单级Push-push结构电容串联,因此堆叠结构的电容大约为单级Push-push隔离电容的一半,这样输入端泄漏到输出端的基波功率减小,有效提升了基波泄漏的抑制效果.

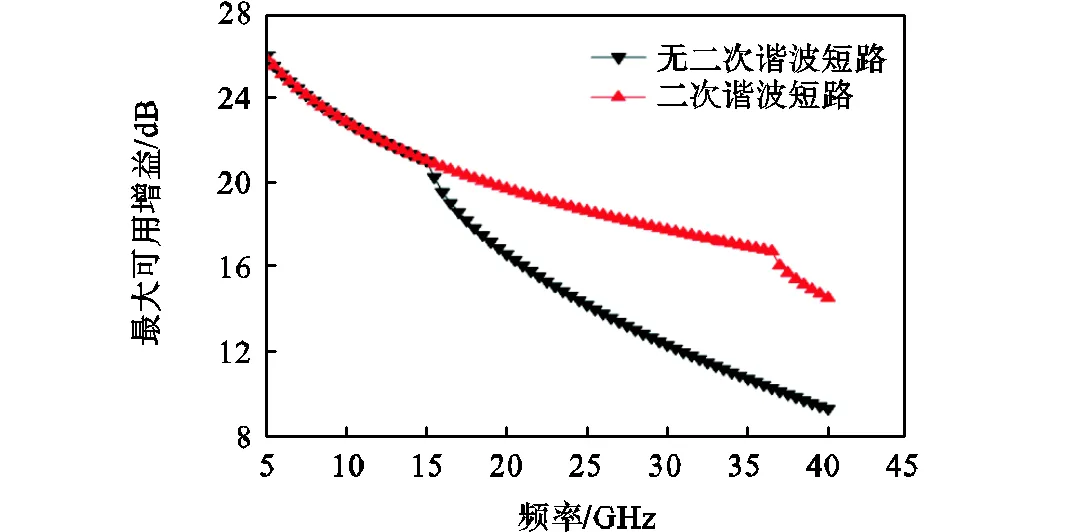

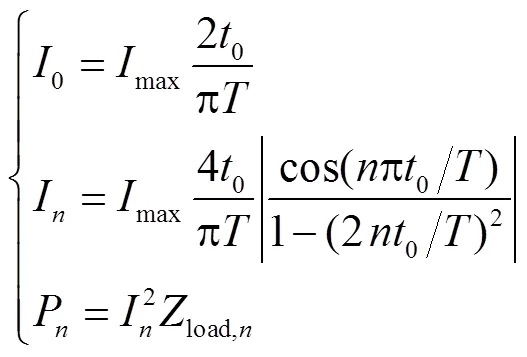

采用二次谐波短路结构的Push-push堆叠共基极二倍频器电路如图4所示.两级均采用共基极放大器结构,共基极放大器相较于共发射极和共集电极放大器,因为其米勒电容较小,特征频率较高,具有很好的宽带特性.同时因为输入电容较小,也更加容易匹配.第2级共基极放大器Q2对二倍频器进行放大同时提升基波和谐波抑制性能.输入端共模点引入电感4和电容2构成二次谐波短路,该结构可以有效减小第1级共基极放大器的输出阻抗,提升第2级共基极放大器的增益,提高二倍频器的变频增益和PAE.输入匹配采用变压器巴伦将单端输入信号,转换为差分信号,作为Push-push电路的输入信号.相比于传输线结构的马相巴伦来说,具有更紧凑的版图布局,可以很大程度上节省芯片面积,降低成本.和有源巴伦相比,可以实现宽带匹配同时没有引入额外功耗降低整体倍频器链路的PAE.因为在低频部分无源器件的值很高,为了实现很好的宽带匹配,在这里并联一个电阻1,降低谐振腔的品质因数实现宽带范围的良好匹配.3、2、5作为输出匹配电路的构成部分,提供高输出阻抗用来获得高的输出功率.二次谐波短路和无二次谐波短路Push-push二倍频器输出功率如图5所示,可以看出二次谐波短路电路有效提升了输出功率.

图4 Push-push堆叠共基极二倍频器电路

图5 二次谐波信号的输出功率

2.2 二倍频偏置对效率和基波抑制的影响

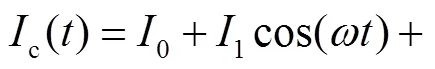

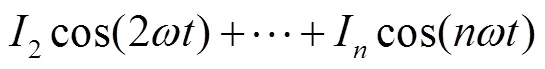

因为二倍频器电路是非线性电路,为了获得高效率的二倍频器,首先对晶体管的各次谐波输出功率和偏置状态的关系进行分析,集电极电流各次谐波电流的值是导通角的函数,导通角是输入信号功率幅值和晶体管偏置共同决定的.集电极电流经过傅里叶变换可以看成是各次正弦波分量叠加得到的,表达式为

式中:Imax为集电极峰值电流;t0为脉冲电流的时间;T为整个的电流周期;Pn为第n次谐波功率.各次谐波和峰值电流比值与电流占空比的函数关系如图6所示.从图6可以看出,为了得到倍频器效率的最大值,此时二次谐波电流和直流电流比值达到最大,二倍频器的效率最高,占空比t0/T=0.35,这里占空比主要和基极偏置有关,基极偏置越高,占空比越大.

从图7中可以看出,随着晶体管基极偏置的增加,二次谐波的比例逐渐升高,在达到一定峰值以后,随着基极偏置继续升高,二次谐波分量逐渐减小.同时为了得到比较好的四次谐波抑制,可以将偏置点稍微前推,此时四次谐波电流分量几乎没有.因为电路拓扑是Push-push结构,当输入信号相位接近180°时,奇数次谐波得到很好的抑制,但是偶数次谐波输出功率较高,需要通过设计进行额外的抑制.

为了更好地分析基极偏置的影响,下面扫描电路二倍频输出信号和晶体管1的基极偏置的关系.从图7可以看出,当基极偏置b1=0.75~0.80V,随着偏置的升高,二次谐波升高而四次谐波降低,大致对应图6中横坐标轴的0.23~0.35区间.基本上在基极偏置处于0.80V,二次谐波输出功率已经达到最大值,但是基极偏置稍微升高达到0.82V,二次谐波功率几乎不变,但是四次谐波很快降低,谐波抑制得到有效提升.基极偏置继续增加到0.85V,二次谐波下降很快.基本符合上述中对二倍频器效率和谐波抑制与基电极偏置关系的理论分析.

2.3 输入匹配对效率和基波抑制的影响

Push-push二倍频器的工作原理是在共模点处奇数次谐波幅值相同但相位相反,两路信号相互抵消;偶数次谐波幅值和相位都相同,两路信号相互增强,实现二倍频信号的输出.从工作原理分析,最理想的输入匹配是两路信号的相位差恰好是180°.当输入匹配出现明显的相位不平衡时,基波和奇数次谐波抑制会很快恶化.二倍频器的输入匹配电路如图8所示.下面从公式的角度说明相位不平衡带来的影响,基波信号输出是两路信号的叠加,其公式为

式中:1为两路信号的幅值;1和2为两路差分信号的相位.当相位差刚好是180°时,此时基波信号为零.相位差偏离180°较大时,基波功率显著上升,抑制较差.三次谐波抑制和基波抑制类似.采用共基极作为输入电路,巴伦的中心接地可以很好实现差分功能.为了实现低的插入损耗,基波输入功率尽可能的注入到电路中,本文采用强耦合的变压器结构.

图8 输入匹配电路

2.4 驱动放大器电路设计

为了提升二倍频器的输出功率以便驱动下一级电路,需要在二倍频器的后面接一个驱动放大器.驱动放大器除了实现高的输出功率,同时可以提高基波抑制和谐波抑制性能.考虑到整体电路的PAE和功耗,最终采用发射极负反馈的共发射极放大器,结构如图10所示.发射极电感e提供作为源退化电感,保证放大器在工作时处于绝对稳定状态,同时在输入和输出之间提供了一个负反馈通路,用来提升线性度[20].输出匹配采用变压器结构匹配,减小版图面积同时可以很好地实现宽带匹配.同时对晶体管进行load-pull实现高功率附加效率(PAE).

图9 输入匹配电路仿真结果

图10 驱动放大器电路

驱动放大器的输出反射系数S22、PAE、输出功率如图11所示,14~26GHz内S22均小于-10dB,在输出功率为7.2dBm时,PAE达到最大值34%,带内PAE均大于20%.

图11 驱动放大器电路仿真结果

3 测试结果和分析

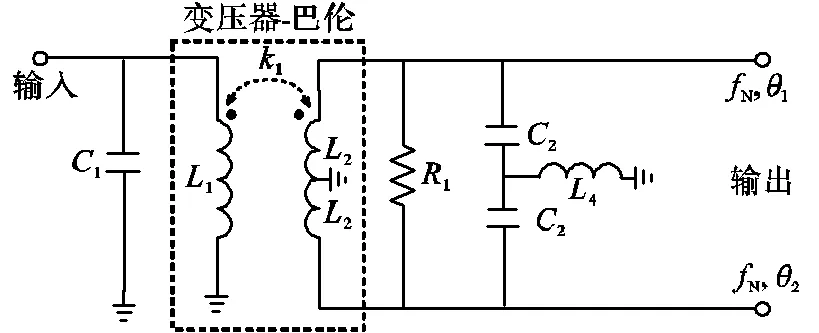

本文设计倍频器芯片显微镜照片如图12所示,因为采用的是共基极Push-push结构,所以输入端仅需要变压器-巴伦匹配,不要额外电感.同时驱动放大器输出匹配也采用变压器-巴伦匹配,版图面积较小(仅为0.245mm2).虽然本设计相比传统共基Push-push二倍频引入了一个额外的电感4用来实现输入端二次谐波短路,但是4的电感值仅为70pH,从图12可以看出二次谐波短路电感4面积很小,没有引入额外的版图损耗.

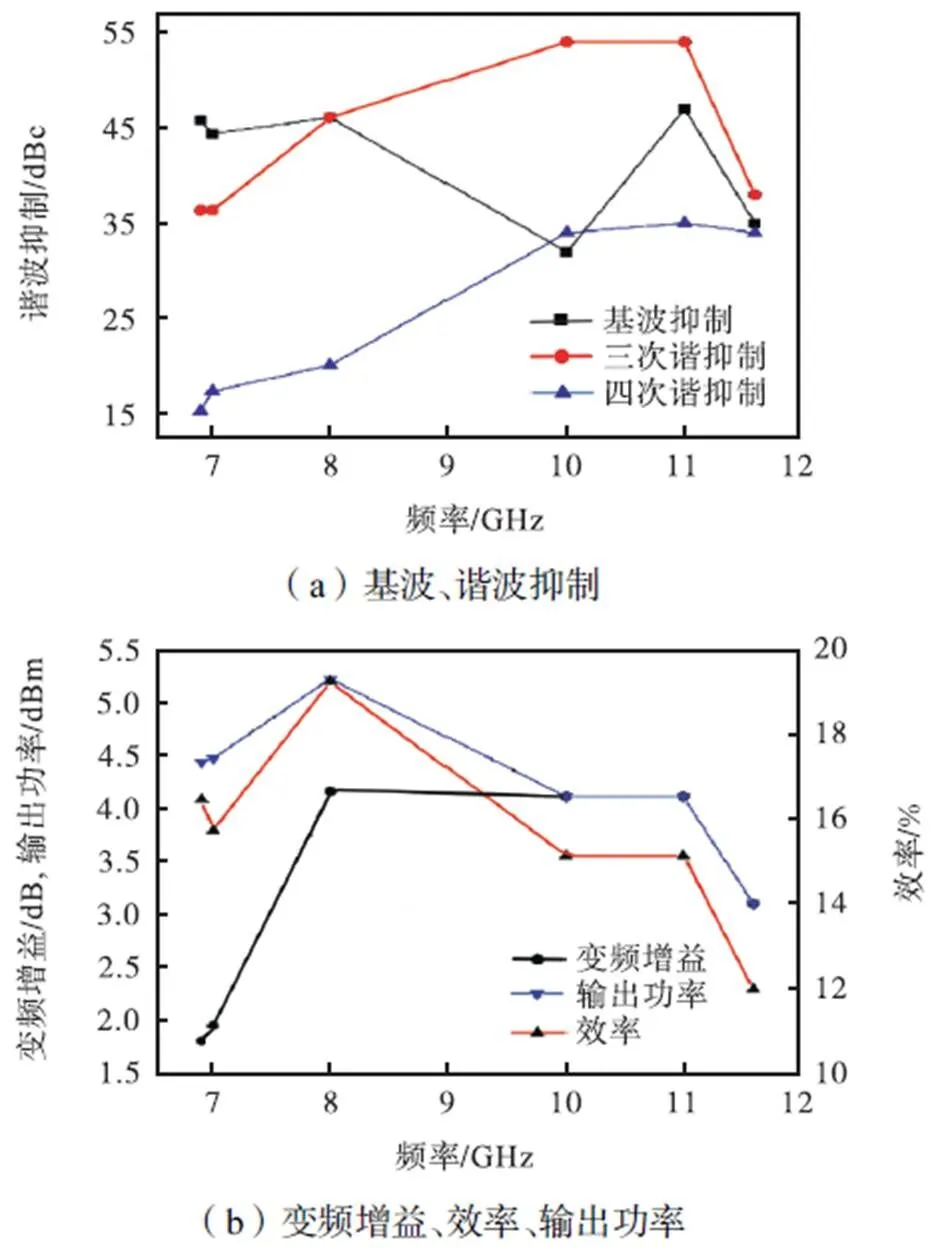

测试设备连接如图13(a)所示,输入信号源由Keysight公司E8275D PSG频率源提供,输出信号由R&S公司FSUP50频谱仪测量.因为输入信号连接到待测芯片输入端和射频输出信号连接到测试设备上都需要很长的同轴线,产生了功率损耗,同轴线的损耗如图13(b)所示.在输入频率为8GHz,输入功率1dBm下的输出谱线如图14所示.此时输出功率为-0.4dBm,计及同轴线损耗5.6dB,实际输出功率为5.2dBm,此时直流功耗16mW,效率达到最大值19%.图15给出倍频器的变频增益CG、输出功率out和PAE的测试结果,从图15(b)中可以观察得出3dB 带宽绝对频率范围是13.8~23.2GHz(相对带宽50.8%.基波抑制在带内均高于32dB,带内PAE为12%~19%.表1为本文中倍频器的指标与已发表的同类倍频器的性能比较,可以看到本设计在效率上均优于同频段设计,即使是带内的最小值12%仍然高于同频段其他设计,同时在版图面积均小于除文献[8]以外的设计.文献[8]面积比本设计略小的原因为文献[8]中二倍频器电路为单级Push-push电路,其变频增益仅为-1dB.综合来看,本设计在版图面积和效率上优于同类设计.

图12 倍频器芯片显微镜照片

图13 测试设备和射频同轴线损耗

图14 倍频器测试谱线(16GHz)

图15 倍频器测试结果

表1 二倍频器性能对比

Tab.1 Comparison of frequency doubler performance

注:1代表CMOS工艺;2代表SiGe BiCMOS工艺.

4 结 语

本文提出了一种二次谐波短路共基极放大器,并基于 130nm SiGe BiCMOS 工艺设计出一款包括二倍频器核心电路、驱动放大器在内的宽带高效率二倍频器,芯片测试结果表明,在输入功率为2dBm的条件,3dB 带宽绝对频率范围是13.8~23.2GHz(相对带宽50.8%),基波抑制带内优于32dB,最高效率达到19%.二倍频器芯片(核心区域,不含测试焊盘)面积为0.245mm2. 综合来看,效率和版图面积上均优于同类设计,适用于K/Ku波段的雷达通讯系统中.

[1] Jung S H,Kim S G,Choi W S,et al. High dynamic range Ku band CMOS transceiver IC for FMCW radar application[C]// IEEE MTT-S International Microwave Symposium. Honolulu,USA,2017:1415-1417.

[2] Wang Y,Lou L,Chen B,et al. A 260mW Ku-band FMCW transceiver for synthetic aperture radar sensor with 1.8GHz bandwidth in 65nm CMOS technology[J]. IEEE Transactions on Microwave Theory and Techniques,2017,65(11):210-218.

[3] Kim Y,Tang A,Chang M F,et al. A Ku-band CMOS FMCW radar transceiver with ring oscillator-based waveform generation for snowpack remote sensing[C]//IEEE MTT-S International Microwave Symposium. Honolulu,USA,2017:64-66.

[4] Andreani P,Andreani P,Padovan F,et al. A 19.5GHz 28nm class-C CMOS VCO,with a reasonably rigorous result on 1/noise up-conversion caused by short-channel effects[J]. IEEE Journal of Solid-State Circuits,2020,55(7):1842-1853.

[5] Katebi M,Nasri A,Toofan S. Low-power VCO for K-band applications[C]//IEEE Iranian Conference on Electrical Engineering Iranian Conference. Mashhad,Iran,2018:144-149.

[6] Vehring S,Boeck G. Novel Push-push frequency doubler concept[C]//IEEE European Microwave Integrated Circuits Conference. Madrid,Spain,2018:210-213.

[7] Vehring S,Boeck G. Truly balanced K-band Push-push frequency doubler[C]// IEEE Radio Frequency Integrated Circuits Symposium. Philadelphia,USA,2018:348-351.

[8] Chakraborty S,Milner L E. A K-band frequency doubler with 35dB fundamental rejection based on novel transformer balun in 0.13μm SiGe technology[J]. IEEE Electron Device Letters,2016,37(11):1375-1378.

[9] Wan J,Chen Z,An Q,et al. A truly balanced Q-band CMOS frequency doubler based on hybrid quadrature coupler[J]. IEEE Microwave and Wireless Components Letters,2017,27(2):165-167.

[10] Shin D,Kim H S,Liu C,et al. A 23.9 to 29.4GHz digital LC-PLL with a coupled frequency doubler for wireline applications in 10nm FinFET[C]//IEEE International Solid-State Circuits Conference. San Francisco,USA,2021:188-210.

[11] Lee W,Alberto V G. W-band SiGe frequency doubler with optimum harmonic termination for 14% efficiency[J]. IEEE Microwave and Wireless Components Letters,2021,31(3):272-275.

[12] Monaco E,Pozzoni M,Svelt F,et al. Injection locked CMOS frequency doublers for U-wave and mm-wave applications[J]. IEEE Journal of Solid-State Circuits,2010,45(8):1565-1574.

[13] Chen Z,Wu Y,Yu Y,et al. A K-band frequency tripler using transformer-based self-mixing topology with peaking inductor[J]. IEEE Transactions on Microwave Theory and Techniques,2020,68(5):1688-1696.

[14] Jung D Y,Park C S. A low-power high suppression V-band frequency doubler in 0.13µm CMOS[J]. IEEE Microwave and Wireless Components Letters,2008,18(8):551-553.

[15] Jia H,Kuang L,Wang Z,et. al. A W-band injection locked frequency doubler based on top-injected coupled resonator[J]. IEEE Transactions on Microwave Theory and Techniques,2016,64(1):210-218.

[16] Tsai P,Lin Y,Wang H,et al. Broadband balanced frequency doublers with fundamental rejection enhancement using a novel compensated marchand balun[J]. IEEE Transactions on Microwave Theory and Techniques,2013,61(5):1913-1923.

[17] Ye Y,Yu B,Tang A,et al. A high efficiency E-band CMOS frequency doubler with a compensated transformer-based balun for matching enhancement[J]. IEEE Microwave and Wireless Components Letters,2016,26(1):40-42.

[18] Mazor N,Katz O,Sheinman B,et al. A SiGe Ku-band frequency doubler with 50% bandwidth and high har-monic suppression[C]//IEEE MTT-S International Microwave Symposium. Tampa,USA,2014:1-4.

[19] Mazor N,Katz O,Sheinman B,et al. A SiGe V-band frequency multiplier with high spectral purity[C]//IEEE European Microwave Integrated Circuits Conference. Paris,France,2015:77-80.

[20] Zhang H,Sánchez-Sinencio E. Linearization tecniques for CMOS low noise amplifiers:A tutorial[J]. IEEE Transactions on Circuits and Systems I:Regular Papers,2011,58(1):22-36.

Design of the Wideband and High-Efficiency Frequency Doubler

Fu Haipeng1,Zheng Yuxue1,Lu Min2,3

(1. School of Microelectronics,Tianjin University,Tianjin 300072,China;2. ZTE Corporation,Shenzhen 518057,China;3. State Key Laboratory of Mobile Network and Mobile Network and Mobile Multimedia Technology,Shenzhen 518057,China)

To overcome the problems of the larger layout area of the common source and the low conversion gain of the traditional common-base doubler,this paper proposes a common base doubler circuit with a second harmonic short-circuit. Compared with the common source structure,the output capacitance of the common-base structure is smaller,thus the matching circuit is smaller. Moreover,the second harmonic short circuit is introduced at the input end,which effectively improves the frequency conversion gain of the common-base doubler. The frequency doubler is composed of a Push-push double frequency doubler circuit and a driving amplifier. The former is used to generate a second harmonic signal,and the latter is used to amplify the second harmonic signal to drive the second-stage circuit of the frequency doubler. The influence of the transistor bias on the output power of the second harmonic was evaluated,and the transistor bias was placed in Class AB to improve the output power and conversion gain. The input common mode point grounding reduces the phase error of the input matching,and improves the fundamental wave suppression and third harmonic suppression. The driver amplifier(DA)adopts a common emitter amplifier structure,and the output-matching part of the DA adopts a parallel resistance transformer structure to increase the matching bandwidth. The test results showed that the 3dB bandwidth absolute frequency ranged from 13.8 to 23.2GHz(50.8% relative bandwidth),and a fundamental rejection of better than 32dB at an input power of 2dBm and a power-added efficiency(PAE) of 19%(output power of 5.2dBm and power consumption of 16mW)was also achieved. The chip size was(core area without test pad)0.245mm2.

frequency doubler;Push-push;wideband;high efficiency

10.11784/tdxbz202103034

TK432

A

0493-2137(2022)05-0504-08

2021-03-17;

2021-09-17.

傅海鹏(1985— ),男,博士,副教授.

傅海鹏,hpfu@tju.edu.cn.

国家自然科学基金资助项目(62074110);国家重点研发计划基金资助项目(2018YFB2202500).

Supported by the National Natural Science Foundation of China(No. 62074110),the National Key Research and Development Program of China(No. 2018YFB2202500).

(责任编辑:孙立华)