一款DVI 视频接收芯片的设计

顾 泓,方 震

(中科芯集成电路有限公司,江苏 无锡 214072)

0 引言

DVI(Digital Visual Interface)芯片在数字视频领域应用[1]广泛且需求量巨大,如数字电视、个人电脑显示屏、雷达显示屏等均广泛采用DVI 技术[2-4]。国外对DVI 技术的研究起步较早,数字显示工作组DDWG(Digital Display Working Group)于1999 年就推出了DVI 1.0 接口标准。标准采用T.M.D.S(Transition Minimized Differential Signaling)技术[5-6]将8 bit 像素数据转换成10 bit 进行串行传输,能够支持三通道并行,各通道串行速率高达1.65 Gb/s 的UXGA 格式像素[7-8]传输。在传输速率较高、时钟与数据相位关系不确定的情况下,接收端如何恢复数据[9]成为了接收端设计的关键。

过采样技术[10]可以有效解决上述数据接收的问题并且易于实现,但是对锁相环(Phase Locked Loop,PLL)的要求较高[11-12]。由于过采样需要产生多个相位时钟,如3 倍过采样就要产生多达30 个相位的时钟,这对PLL 的设计是一个很大的挑战。而本文采用的数据恢复方案基于3 倍过采样,只需PLL 产生12 个相位的时钟,与文献[13]相比大大减小了PLL 的设计难度和功耗。文献[14]会根据采样结果产生相位调整信号输出给相位调整电路,调整PLL 输出时钟相位至合适区间,进而采样恢复出数据。而本文采用基于全数字的数据恢复方案,可直接根据采样结果分析恢复出数据,这样无需时钟相位调整电路,降低了芯片的硬件开销,同时由于采用全数字逻辑实现,提高了电路的稳定性。

基于该方案本文设计了一款DVI 接收芯片,实现了T.M.D.S 编码数据的正确接收和恢复,满足DVI1.0 接口规范的功能和性能要求。本文给出了设计的整体框架,说明了各子模块的功能和作用,重点讲述了本方案中数据恢复的原理和逻辑实现,最后给出了仿真和实测结果,并进行了相关分析和讨论。

1 整体框架及功能

本设计的整体方案框架如图1 所示,包括SPI(Serial Peripheral Interface)及寄存器管理单元、输入整形单元、时钟检测单元、锁相环、数据恢复单元、解码和同步单元。

图1 DVI 接收芯片整体框架

SPI 及寄存器管理单元中,SPI 接口可用于读写寄存器,寄存器管理单元的作用包含电路参数配置、电路状态监控等。

输入整形单元可以抑制输入信号幅度改变导致输出信号幅度改变的影响,使输出信号的高低电平电压值恒定,降低因输入信号幅度变化对后级电路的影响。

时钟检测单元可以检测输入时钟信号并输出使能信号。当检测到时钟输入时,单元输出使能信号控制相关模块进入正常工作状态;当未检测时钟输入时,单元输出使能信号控制相关模块进入空闲状态。

PLL 可以恢复出输入时钟并生成输入时钟2.5 倍频后的12 路等相位间隔的时钟送给数据恢复单元。

数据恢复单元利用12 路等相位间隔时钟对输入串行数据进行3 倍过采样,进而对采样数据进行相位判决恢复出原始数据。

解码和同步单元对原始数据进行解码,恢复出像素数据和场同步数据并进行通道间数据同步,输出并行数据和同步的时钟信号。

SPI 及寄存器管理单元属于比较成熟的数字逻辑电路,时钟检测单元和PLL 也是比较成熟的IP,输入整形单元属于容易实现的模拟电路,对它们本文不做过多的介绍。对DVI 芯片来说,核心功能是将输入串行信号解码恢复成原始并行信号。在DVI 1.0 接口标准中,解码方式被明确地给出了,可以很容易地实现解码逻辑。一旦解码出场同步信号,各通道之间的同步也不难解决。而数据恢复是本设计的难点。由于输入数据和输入时钟之间的相位关系是不确定的,频率也不相同,无法通过直接采样得到数据。数据恢复单元解决了这一问题。它的作用是确定两者之间的相位关系并进行准确的采样。下面将详细介绍这部分的实现原理。

2 数据恢复的逻辑实现

数据恢复单元先对单个码元进行3 次过采样,得到对应10 bit 串行数据的30 bit 采样并行数据,再对这10组(每组3 bit)采样数据进行采样相位关系判决,得出采样时钟相对数据的超前和滞后关系,进而决定出采样中心,对数据中心进行采样恢复出原始数据。数据恢复单元包括采样数据缓冲单元、相位判决单元、中心判决单元和中心采样单元。数据恢复单元整体结构框架如图2所示。

图2 数据恢复单元

本设计采用空间过采样[15]的方式对输入数据进行3倍过采样,10 bit 信号经过3 倍过采样可以产生30 bit信号。文献[16]解释了采样倍数选择的依据,此部分内容不在本文描述范围内。根据DVI1.0 规范,输入数据是以10 bit 为单位进行串行传输,最后需要的是30 bit 并行采样数据,所以需要进行数据缓存和串并转换。采样数据缓冲单元结构如图3 所示。其中,RXin 为接收串行数据,RXCLK 为PLL 恢复出的接收时钟;PH0-11 代表12 路采样时钟,频率是接收时钟频率的2.5 倍,串行码率的0.25 倍,相邻时钟相位差为1/3 码元周期。采样数据缓冲单元由触发器阵列构成,利用时钟间的相位关系对数据进行打拍操作,最终得到30 bit 并行采样数据。并行采样数据包含了时钟和数据的相位关系信息,而这种信息是可以通过某种方式提取出来的。

图3 采样数据缓冲单元

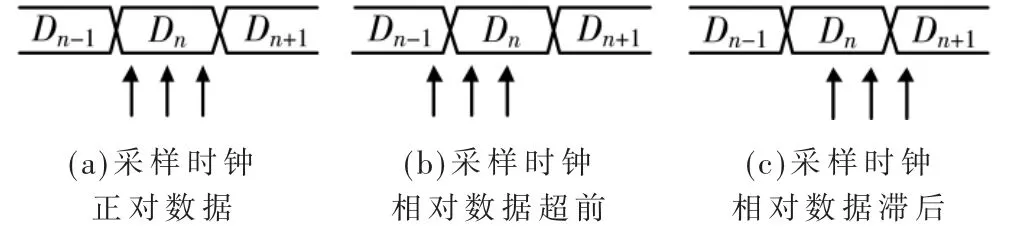

相位判决单元的作用是提取输出采样时钟和输入数据的相位关系并输出。如图4 所示,图4(a)表示采样时钟对同一位数据进行采样;图4(b)表示采样时钟相位相对数据超前,采样结果为1 bit 前一数据和2 bit 当前数据;图4(c)表示采样时钟相位相对数据滞后,采样结果为2 bit 当前数据和1 bit 后一数据。

图4 采样时钟和数据相位关系

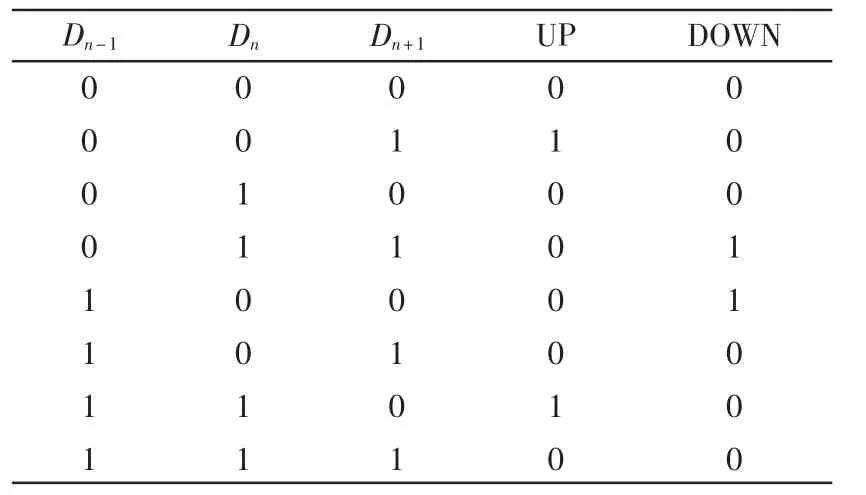

为了区分以上情况,表1 给出了采样结果和相位之间的真值表关系,其中UP/DOWN 为1 代表相位超前/滞后。根据真值表,000 和111 代表图4(a)所示情况,011和100 代表图4(b)所示情况,001 和110 代表图4(c)所示情况,010 和101 为非正常工作情况。这里需要特别指出一种情况即三路时钟的中间路时钟恰好在数据跳变的时候采样,这时候采样结果可能为011、001 或100、110,UP 为1 和DOWN 为1 的数量就变得不可预估,既可以归为超前也可以归为滞后,但不影响最终结果。30 bit采样结果被分成10 组3 bit 数据,经过10 个判决单元,最终得到10 bit UP 和10 bit DOWN 信号。

表1 采样结果和相位关系真值表

中心判决单元的作用是对前级10 bit UP 和DOWN信号进行统计判断,得到最终相位关系UPT 和DOWNT信号。具体的规则是,若UP 信号为1 的数量大于等于5,则UPT 为1,反之为0;若DOWN 信号为1 的数量大于5,则DOWNT 为1,反之为0。由于相位关系只存在三种情况:超前、滞后和正对关系,因此UPT 和DOWNT 的组合为10、01 和00(11 为无效状态)。如果出现连续4 组有效的UPT 和DOWNT 信号,则输出对应有效相位控制信号Phase[1:0]。

中心采样单元可以根据前级中心判决单元提供的相位控制信号Phase[1:0]选取采样中心点,恢复出10 bit并行数据。假设采样数据为A0、A1、A2,若Phase[1:0]为01,则相位超前,采样中心点在A2 位置,选择A2 作为输出数据;若Phase[1:0]为10,则相位滞后,采样中心点在A0 位置,选择A0 作为输出数据;若Phase[1:0]为00,则相位无超前或滞后,采样中心点在A1 位置,选择A1作为输出数据;若Phase[1:0]为11,为无效控制信号,维持之前采样中心点选择,并且此时输出数据无效。一旦确定采样中心点,就可以稳定恢复出并行的10 bit 原始串行数据。

3 结果与讨论

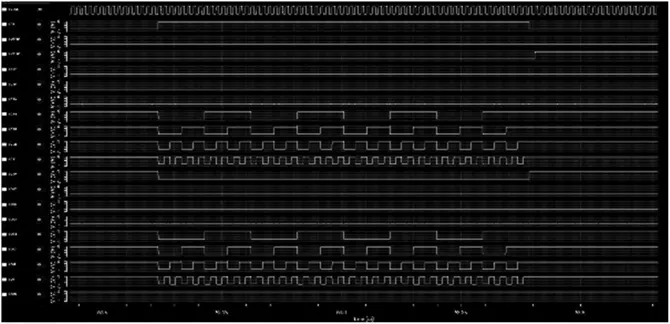

本设计涉及模拟和数字设计,分别对输入整形单元、时钟检测单元、锁相环等模拟模块进行原理图设计、前仿、版图设计和后仿,对SPI 及寄存器管理单元、数据恢复单元、解码和同步单元等数字模块进行Verilog RTL 实现、综合、布局布线、版图设计和后仿,最后对全芯片进行版图设计和后仿验证。经多种条件验证,芯片可以满足DVI1.0 规范的要求,支持三路并行、单通道传输速率高达1.65 Gb/s 的编码像素数据的接收和恢复。如图5 所示,在接收时钟为165 MHz,接收码率为1.65 Gb/s,2 piexl输出模式条件下对全芯片进行后仿验证,输出可以恢复出原始数据(QE7-0 为0x00、0x02、0x04…,QO7-0 为0x01、0x03、0x05…),对应图中两组变化信号部分。

图5 DVI 芯片的数据接收恢复

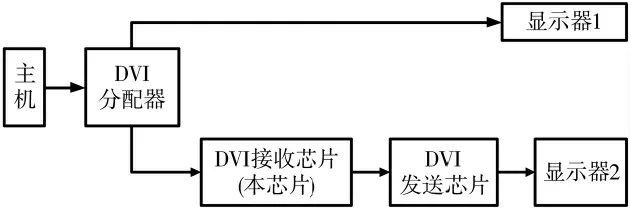

为了验证本芯片数据接收恢复的功能以及与市面上DVI 产品的兼容性,本文在实际测试时采用了本芯片与已有DVI 发送芯片级联通信的方案,如图6 所示。主机发送TMDS 编码信号给DVI 分配器,经DVI 分配器产生与输入相同的两路TMDS 输出信号,其中一路信号直接发送给显示器1 的DVI 接口,另一路信号经过DVI 接收芯片(本芯片)、DVI 发送芯片(市面上已有芯片),最终到达显示器2 的DVI 接口。

图6 本芯片功能与兼容性测试方案

采用该方案对本芯片进行实际测试后,结果如图7所示,可以观察到显示器1 和显示器2 的图像显示结果相同,说明了显示器1 和显示器2 均能够正常接收主机发送的数据。所以,本芯片数据接收恢复功能正常,与发送芯片之间兼容且通信良好,满足DVI 1.0 规范要求。

图7 本芯片与市面上某款DVI 发送芯片之间的级联通信

4 结论

本文研究了DVI 数据接收恢复的关键技术,采用了一种基于全数字的数据恢复方案,降低了PLL 的硬件设计难度。在此基础上,设计了一款DVI 接收芯片,设计满足DVI1.0 接口规范要求,能够实现单通道传输速率在250 Mb/s 至1.65 Gb/s 区间的三路并行TMDS 编码信号的接收解码。经实际测试,该芯片能够实现TMDS 信号的接收和恢复,并且与市面上已有DVI 发送芯片具有良好的兼容性。