应用于高精度模数转换器的乘法数模单元模块研究*

邵 杰,唐 路,2

(1.东南大学微电子学院,南京210096;2.东南大学信息科学与工程学院,南京210096)

1 引言

模数转换器(Analog-to-Digital Converter,ADC)是现代电子系统的关键模块。近年来,随着电子技术的发展,信号测量、电子通信等领域对于ADC的精度、速度、功耗等性能有着越来越高的要求。自20世纪70年代起,各种有优势的ADC架构被相继提出,如Sigma-Delta-ADC、 逐 次 逼 近 型(Successive Approximation Type,SAR)ADC、流水线型(Pipeline)ADC等,Sigma-Delta-ADC架构目前应用很广,尤其是在高分辨率ADC设计上,这种调制型的ADC架构使用过采样算法实现有限脉冲响应或者无限脉冲响应数字滤波器,虽然能实现极高的分辨率但是信号输出会产生延时。SAR-ADC一般应用在中等采样速率中,在高分辨率应用下,成本较大且模拟信号在进行转换之前需要配套的调理电路,这又会进一步增加成本。因此相对于Sigma-Delta-ADC和SAR-ADC,Pipeline-ADC在高速高精度应用场合更受青睐[1-2]。

Pipeline-ADC的基本原理是将总精度N分配到若干个流水线子转换级中,每个流水线子转换级负责部分精度的转换,同时将余差信号放大相应的倍数输出给下一级进行转换,各级转换出的数字信号经过延迟对准后送到数字校正电路进行处理,处理完成后输出最终的数字码。乘法数模单元(Multiplying Digital-to-Analog Converter,MDAC)在Pipeline-ADC中起着余差放大的作用,显然,在多级Pipeline-ADC中,第一级MDAC对性能的要求是最高的[3]。

本文提出一种可以应用在高精度Pipeline-ADC中的首级高性能MDAC电路设计方法。该ADC采用无采保结构,首级流水线子转换级精度为4 bit,要求第一级MDAC有14 bit的有效精度。

2 MDAC的工作原理和误差分析

本文设计的MDAC电路以及时序如图1所示,这是典型的开关电容电路,CS和CF在采样阶段都起到采样电容的作用,反馈阶段利用CF将电路接成负反馈形式,CS底极板接共模电压,顶极板接固定参考电压,利用电荷守恒原理就可以实现余差放大的功能[3]。

图1 MDAC电路结构以及时序示意图

后级子转换级的最大转换精度是总精度减去前级已转换精度,所以开关电容电路性能的优劣会直接影响到整个ADC系统。开关电容电路交替工作在采样和放大两个相位,不同阶段的噪声和误差来源有所差异。在采样相,热噪声是影响采样精度的主要因素,而在放大相,跨导放大器(Operational Transconductance Amplifier,OTA)的建立精度、增益以及本身的噪声都会对MDAC的动态范围(Dynamic Range,DR)产生影响。文献[4]分别对开关电容电路的采样相和放大相建模,分析了开关电容电路中开关以及OTA的输出噪声。采样相积累的噪声在放大相等效到输出端可以表示为:

其中k是玻尔兹曼常数,T为温度,qX是OTA输入端积累的噪声电荷,Cpar是OTA输入端寄生电容。式(2)、(3)分别表示在放大相开关和OTA产生的噪声:

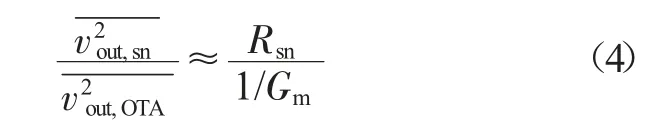

其中Rsn是开关的导通电阻,Req是OTA输出端等效电阻,Ceq是OTA输出端等效电容,γ是过量噪声因数,一般取值在1~2之间,Gm是OTA的跨导,β是电路的反馈系数。将开关产生的噪声和OTA产生的噪声相比可以得到:

因此,在设计开关电容电路时,开关的导通电阻要尽可能小于OTA的1/Gm,这样开关在放大相的影响是可以忽略的。

基于CMOS工艺设计的开关存在电荷注入、时钟馈通以及导通电阻非线性等非理想因素,通过底极板采样技术以及选用全差分架构可以有效降低电荷注入、时钟馈通带来的影响。针对导通电阻的非线性,无采保结构(SHA-Less)Pipeline-ADC的第一级MDAC会选择栅压自举开关(Bootstrap)来降低开关导通电阻非线性带来的影响[5]。

3 关键电路设计

3.1 跨导放大器关键参数的选取

为了保证转换精度,第一级MDAC的静态建立误差需要小于剩余转换精度的1/2最低有效位(Least SignificantBit,LSB),因此OTA的开环增益应满足:

考虑工艺偏差,实际设计中在理论值基础上预留10~20dB裕度,OTA开环增益指标定为130dB。此外,动态建立误差也需要小于剩余转换精度的1/2LSB。MDAC的动态建立过程包括大信号和小信号建立两部分。图2(a)是反馈网络中信号建立的示意图,其中VOV是OTA输入管的过驱动电压。当输入一个阶跃信号时,刚开始阶段反馈网络还没有完成建立,此时OTA处于大信号建立阶段,在Vx进入线性范围之后,环路建立完成,系统进入小信号建立阶段,也称之为线性建立。

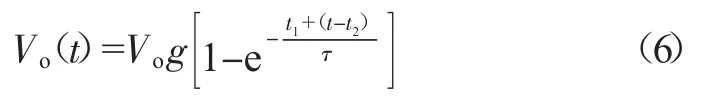

一般情况下,设计者会通过增大静态电流来提高压摆率,进而减小大信号建立时间,但是这在很大程度上增加了电路的功耗。事实上在很多开关电容电路中,只需要在采样阶段最后时刻系统的建立精度能达到要求即可。从图2(b)可知,虽然大信号建立和线性建立的形式不同,但趋势上是一致的,所以大信号建立的时间可以统一到线性建立过程中[6]。

图2 信号建立

将线性建立的表达式修改成式(6),其中t1是大信号建立等效成小信号建立的时间,t2是实际大信号建立时间。

由于系统是连续变化的,线性建立最初时刻的斜率等于压摆率,联立这两个关系式可以计算得到t1,进而得到此时的电压,最后通过压摆率反推出实际的大信号建立时间t2。

已知系统采样率为20MHz,占空比为50%,负载电容CL为8pF,最大差分输出摆幅为4.8V。MDAC要在25ns内完成信号的建立,通过式(6)(7)可以计算出系统所需的最大时间常数τ以及最小静态电流。折中考虑后系统3dB带宽取100MHz,静态电流取30mA,反馈系数β取1/10,则OTA开环单位增益带宽需要1GHz。

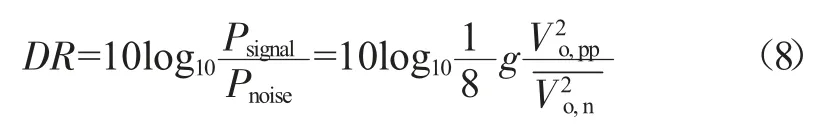

通过前文对MDAC系统误差的分析,当开关导通电阻远小于OTA跨导Gm时,放大相系统的噪声主要由OTA产生。已知后级转换精度是14bit,所以第一级MDAC输出动态范围至少需要86dB。由式(8)可以计算出第一级可以容许的最大输出噪声为7.23×10-9V2。

3.2 增益提升型跨导放大器的设计

传统两级结构的OTA很难实现超过130 dB的直流增益,本设计采用了改进的两级放大器,其中第一级使用了增益提升(Gain Boost)技术,Gain Boost技术的两级放大器如图3所示,其中共模反馈以及偏置电路没有给出。

图3 使用Gain Boost技术的两级放大器

采用密勒补偿实现主次极点分离,从而使系统稳定。但密勒补偿带来的右半平面零点会严重影响系统的相位裕度,通过加入调零电阻调整零点的位置,可以改善相位裕度。

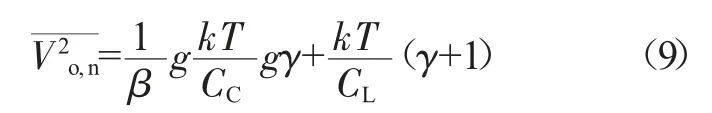

补偿电容的大小除了影响系统稳定性,还和系统的动态范围有关[7]。使用密勒补偿的两级运放构成的开关电容电路输出噪声可以近似表示为:

综合考虑系统的带宽、稳定性和噪声特性,补偿电容CC取30 pF。使用调零电阻RZ后,系统右半平面零点可以用式(10)表示,其中gm23是主运放输入管的跨导。通过式(11)可以计算出将右半平面零点移到左侧UGB外2倍处需要的RZ大小。

使用增益提升技术可以有效提升放大器的直流增益,但是在设计时需要特别关注内部环路的稳定性问题。由于辅助运放的输出端会产生一个零极对,这会对整个环路的信号建立产生恶劣影响。对于零极对的处理方式是将辅助运放的单位增益带宽设置在环路3 dB带宽和系统非主极点之间,内部环路相对于主环路可以更快地建立,这样主环路带宽内就不会受到零极对的影响。如图3虚线框内所示,为了方便优化辅助运放的带宽,可以在主运放的输出端加上旁路电容对内部带宽进行调整,这两个额外的电容也可以起到降低噪声的滤波作用[8-9]。

在评估Gain Boost结构的噪声特性时,可以在传统两级放大器输出噪声的基础上预留10%的冗余。使用了Gain Boost技术的两级放大器的噪声主要由输入对管以及负载电流源管产生,已知共源极电路每单位带宽的输入参考噪声为:

其中RD是漏端电阻,K是一个与工艺有关的常量,数量级为10-25V2·F,WL是晶体管的宽长,f表示频率。在低噪声OTA设计中,输入管跨导要尽可能大,电流源管跨导要尽可能小。为了抑制辅助运放带来的噪声可以适当增大辅助运放的带宽,再利用旁路电容进行滤波以及调整辅助环路带宽。

4 仿真结果

本设计采用0.18μm 5 V/1.8 V CMOS工艺,使用Spectre和Calibre进行后仿验证。第一级最大差分输出摆幅是4.8 V,将输入信号摆幅控制在Sub-ADC一个判别区间之内,从而可以单独对MDAC做快速傅里叶变换(Fast Fourier Transform,FFT)。

本文设计的MDAC电路的频率响应如图4所示,其低频环路增益为133 dB,单位增益带宽为97.15 MHz,相位裕度为83.25°。

图4 频率响应

表1列出了第一级MDAC在放大相位的主要噪声来源。与前文理论分析一致,差分输入对管产生了最主要的噪声,其次是第一级的电流源管以及第二级的差分输入管和电流源管。第一级在放大相位一共产生6×10-9V2噪声,达到设计指标。

表1 主要噪声分布情况

在温度为27℃、TT工艺角下,输入5MHz正弦波信号,MDAC瞬态仿真结果如图5(a)所示,512点FFT结果如图5(b)所示。SNR为84.4dB,ENOB为13.83bit,SFDR为97.6dBc,THD为-94.7dB,基本达到设计指标。MDAC的版图如图6所示,为了保证电路尽可能对称,版图采用完全对称布局,开关电容阵列分布在运放两侧,其中采样电容和反馈电容使用交叉匹配放置,差分输入对管以及采样电容等关键器件使用了Dummy管以及Dummy电容来减小工艺带来的失配。

图5 时域频域仿真结果

表2总结了本设计在部分工艺角和温度组合条件下的性能参数,不同工艺角和温度下本设计的性能相对稳定,有足够的稳健性。表3将本研究设计的高精度Pipeline-ADC和国内一些同类型的高精度Pipeline-ADC进行了比较,从表中可以看出,本设计在动态性能和转换精度上都有一定的优势。

图6MDAC版图

表2 不同工艺脚、温度下的性能参数

表3 本文与此前研究成果性能对比

5 结论

本文设计了一款应用于18 bit 20 MS/s无采保高精度Pipeline-ADC的MDAC模块,分析了电路的误差来源,从减小静态、动态误差以及晶体管噪声的角度对MDAC的设计提出了建议。

通过和同类型设计进行比较,本设计在转换精度、线性度等性能上有一定优势,但同时也存在一些待优化的地方,主要有以下两个方面:首先是功耗较大,虽然本设计在静态电流大小以及补偿电容、采样电容等关键参数的选取上已经做了折中,但是在更注重低功耗设计的今天,本设计的功耗仍相对较大;其次,实际ADC系统中的噪声来源更为复杂和多样,比如时钟抖动、基准误差以及PCB板的电磁干扰,所以MDAC电路设计需要更多噪声冗余空间。针对这两个问题,利用数字校准技术以及更为合理的版图布局来解决是十分重要的研究方向。