FPGA多程序动态老炼系统设计

季振凯,谢文虎

(无锡中微亿芯有限公司,江苏无锡 214072)

1 引言

随着市场需求和技术的发展,FPGA规模呈指数增长,目前国内已经能够研制亿门级FPGA产品,超大规模集成电路由于随机的制造缺陷导致的各类偶发缺陷将无法避免[1]。FPGA制造过程中产生的偶发缺陷通常会导致器件功能异常,90%以上表现为固定缺陷,称之为质量缺陷,可通过圆片测试、初始电测试剔除;少部分表现为初始正常,工作一定时间后,异常缺陷放大,然后表现出功能异常,这种缺陷称为潜在缺陷。由于潜在缺陷的不可预测性,提供有效的方法激发集成电路潜在缺陷、剔除早期失效产品,是高可靠集成电路设计和制造领域的重要研究内容。

剔除早期失效电路的方法是进行电路静态老炼或动态老炼试验[2]。静态老炼只施加电应力和温度应力,可诱发与杂质污染相关的潜在缺陷[2]。动态老炼需在静态老炼的基础上增加激励信号,使电路内部逻辑资源发生翻转,提高老炼应力,激发潜在缺陷。

国外对FPGA老炼的研究较早,美国NASA发表了SRAM型FPGA老炼试验报告[3],详细地介绍了商用SRAM型FPGA老炼试验系统的软硬件设计和试验原理图。加州理工学院和加利福尼亚州立大学发表了针对宇航级FPGA的老炼方法[4],提出宇航级FPGA与普通器件的差异,并设计了相应的测试向量和检错方法。国内对FPGA老炼的研究也取得了较大进步,中国电子科技集团公司第五十八研究所郁振华和朱卫良发表了针对FPGA电路的动态老炼技术,是针对静态老炼的提升,可提高FPGA老炼应力[5];北京微电子技术研究所王茉针对高可靠FPGA提出了老炼系统的软硬件设计方案[6],老炼程序覆盖了FPGA所有IO的一种电平模式,以及通过移位寄存器实现部分资源的覆盖。

目前国内外对FPGA老炼的研究集中在老炼方法设计、单段老炼程序设计和老炼激励设计。但FPGA规模越来越大,单段程序的动态老炼试验资源覆盖率越来越低,存在绝大部分资源未被施加老炼应力的问题。针对该问题,本文提出一种多程序动态刷新老炼系统以及高覆盖率老练程序设计方法,通过多段老炼程序循环刷新的方式提高FPGA的老炼覆盖率。

2 老炼理论依据

2.1 FPGA失效和时间的关系

FPGA寿命周期中失效率和其他集成电路类似,符合经典“浴盆曲线”(或“浴盘曲线”)理论[7],集成电路失效“浴盆曲线”如图1所示。

图1 集成电路失效“浴盆曲线”

根据失效概率,FPGA寿命周期可划分为3个失效期,分别是早期失效期、偶然失效期以及耗损失效期[8],每个阶段表现出不同的特征。

(1)早期失效

早期失效阶段的失效原因是设计缺陷、原材料缺陷或制造过程偶发缺陷[9-10]。该阶段发生失效的概率与时间的关系符合韦布尔分布[11]。

(2)偶然失效期

偶然失效期也称为使用期或随机失效期,FPGA产品进入偶然失效期后失效概率将趋于稳定且降至最低,偶然失效期是产品状态最好的阶段。发生偶然失效主要原因是质量缺陷、材料缺陷、环境过于恶劣或使用方式不当等[9-10]。偶然失效期的失效概率与时间的关系符合指数分布[7]。

(3)损耗失效期

电路长期使用将造成FPGA电路老化和过度损耗,FPGA电路失效概率在此阶段开始快速上升,电路失效的内在原因是金属化电迁移和热载流子效应。损耗失效期的失效概率和时间关系符合对数正态分布[11]。

2.2 FPGA老炼的意义和理论依据

通过环境应力筛选、老炼等措施,可剔除早期失效产品,同时加速集成电路老化,使集成电路尽早进入低失效率的偶然失效期。

老炼试验的理论依据是经典反应速率理论,即当外界的电、热等应力增加时,器件会加速老化[12]。老炼对集成电路寿命周期的影响如图2所示,在正常使用条件下,FPGA器件需要几千小时进入偶然失效期,如果对器件进行老炼,器件可在几十个小时后进入偶然失效期。

图2 老炼对集成电路寿命周期的影响

在FPGA的老炼试验中,频率和电压采用正常工作的条件,主要以温度作为加速变量。硅集成电路在以温度为加速应力条件下的加速因子数据可通过Arrhenius经验公式计算:

其中,T1、T2为开氏温度,t1、t2分别为T1、T2产生相同退化量对应的时间,t1/t2为加速因子;K为玻尔兹曼常量,K=8.62×10-5eV/K;Ea为缺陷激活能,可取0.403 eV。

根据式(1),电路在高温125℃条件下老炼72 h等效于在25℃下老化154天。

3 多程序动态老炼系统设计

多程序动态老炼系统的设计主要包含老炼系统软硬件设计以及被老炼FPGA的老炼程序开发。

3.1 老炼系统软硬件设计

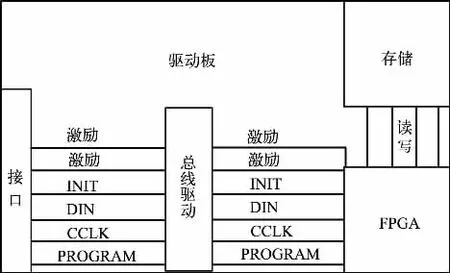

根据整体方案需求,设计了如图3所示的多程序动态老炼系统。整个系统由两部分组成,一部分为工位板,另一部分为驱动板,工位板位于高温箱内部,驱动板位于外部,两部分采用专门的连接件连接。

图3 多程序动态老炼系统整体功能框图

工位板的功能是承载被老炼FPGA电路,该PCB板只包含FPGA安装插座以及相应的阻容器件。工位板FPGA采用被动串行配置,每一个FPGA需要至少4根信号线(CCLK,DIN,INIT,PROGRAM)用于配置,每一块老炼板上有12个FPGA工位,由于CCLK、DIN、PROGRAM为输入信号,INIT在完成初始前为低,完成初始化后为高阻态,以上信号可以直接互连且不损伤端口,为了减少端口数量,多个器件可共享一个来自驱动板的信号,工位板信号共享示意图如图4所示。除配置信号外,还需要激励信号,激励信号采用与配置信号相同的连接方式。

图4 工位板信号共享示意图

软件设计主要体现在驱动板,驱动板功能是向工位板FPGA发送配置信号和激励信号,该板主要由能够控制信号输入输出的FPGA、能够存储所有老炼文件的存储器、能够增强FPGA输出信号驱动能力的驱动电路(如164245等)以及能够提供工位FPGA工作电压的电源芯片组成。驱动板的信号传输流程为:存储器存储工位板FPGA的配置文件由驱动FPGA读出,经过总线驱动电路后发送给工位板并对工位板FPGA进行配置,完成配置后对工位板发送激励信号。驱动板的电路连接图如图5所示。

图5 驱动板电路连接图

3.2 老炼程序设计

实现高覆盖率老炼系统的重点工作内容是老炼程序的设计,需要针对不同的器件单独开发,老炼程序的开发包括功能模块和布线资源的设计,实现对BLOCK RAM、CLB、IOB、DSP、时钟管理模块以及开关和互连线资源的覆盖。老炼程序采用内建自测试(同一个器件同时实现信号发生模块和信号测试模块的功能)的设计方式,老炼系统通过检测电路输出的信号判断电路逻辑正确性,老炼程序使用4个端口输入,并在固定的3个端口输出自测试结果。

3.2.1可编程逻辑块老炼程序设计

FPGA电路包含大量可编程逻辑块(CLB)。每个CLB由2个或4个Slice组成,每个Slice包含4输入或6输入查找表、选择器、进位逻辑以及寄存器等功能模块。CLB内部结构复杂,单段程序无法实现对CLB各个功能块的覆盖。在设计多段老炼程序时,为提高程序覆盖效率,首先应进行模块划分,将能够在同一个程序中实现的模块划分成一类,功能模块划分如表1所示。

表1 功能模块划分

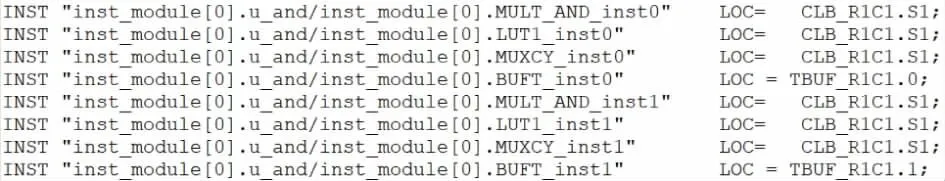

CLB老炼程序采用调用原语的方式实现,然后进行位置约束。根据资源复杂程度的差异,部分模块需要多段老炼程序。以MULT_AND老炼程序为例,MULT_AND一共4段程序,分别覆盖器件上半部分CLB.S0、CLB.S1和下半部分CLB.S0、CLB.S1,主要老炼Slice内部进位链的与门MULT_AND功能块,图6、7分别为MULT_AND上半部分CLB.S1老炼程序部分原语代码和部分UCF约束代码。

图6 MULT_AND老炼程序原语

图7 MULT_AND老炼程序约束语句

表2为MULT_AND老炼程序的资源占用情况,根据表2的统计,单个代码Slice占用率是77%,其中50%的Slice为实现老炼覆盖被约束在器件的上半部分,另外27%是为实现内建自测试消耗的资源。因为单段程序只涉及单一资源,内部触发器和LUT的占用比例较低,但多个程序叠加能够完成对CLB的100%覆盖。

表2 MULT_AND老炼程序资源占用情况

3.2.2 BRAM、DSP和时钟单元等硬核模块老炼程序设计

BRAM、DSP和时钟单元等硬核模块为黑盒子模块,老炼程序设计较为简单,只需要根据BRAM和DSP的各种工作模式进行穷举调用。以BRAM老炼程序设计为例,BRAM初始化值为全0,采用March C+算法,覆盖所有位宽,覆盖A写A读、A写B读、B写A读、B写B读即可。

3.2.3开关和互连线老炼程序设计

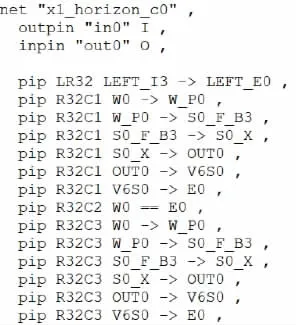

FPGA能够实现高度灵活性的原因在于FPGA包含了大量的开关和互连线资源,这种优势也给老炼程序的设计带来了挑战,开关和互连线老炼程序采用xdl语言设计,首先生成xdl文件,然后通过xdl文件生成位流文件。这种方法不需要约束文件,可以完全根据设计人员的需要定制老炼程序,具有覆盖率高的优点,但需要了解FPGA内部所有互连节点的分布和命名规则。图8是单倍线xdl代码截图(部分)。

图8 单倍线xdl代码(部分)

根据布线资源跨越CLB数量的不同,至少需将互连线的设计分为3类:单倍线(连接相邻开关矩阵不跨越任何CLB的布线)、六倍线(通过一个开关矩阵跨越5个CLB与另一个开关矩阵相连的布线)和全局长线(贯穿整个FPGA的CLB阵列,具有最小延时的布线),且需覆盖开关矩阵内部的可编程互联点PIPs(Programmable Interconnect Points)。

3.3 老炼系统工作流程

工位FPGA采用被动串行配置,老炼系统工作流程由以下步骤构成:

(1)将需要的若干段老炼程序(测试程序移植和减端口改造)以BIN文件的形式写入到驱动板的存储器中;

(2)工位板和驱动板上电后,驱动板向老炼板发送配置时钟信号CCLK和配置信号DIN,实现对FPGA的从串模式配置;

(3)完成第一段全部的配置数据写入后,保持CCLK电平不变;

(4)驱动板根据当前写入的配置程序,给予相应的激励;

(5)在等待特定的时间后(300~600 s),PROGRAM发低脉冲,等待INIT为高后,重新写入新的老炼程序;

(6)重复2~5步,周而复始,实现多老炼程序的动态刷新。

4 覆盖率统计和对比

目前已经在多个FPGA产品中实现了动态老炼系统,以某型30万门FPGA为例,老炼程序共148段,可实现所有硬核资源以及绝大部分开关和互连线资源的覆盖。通过专用软件统计148段老炼程序综合资源覆盖率并与原来的单段老炼程序对比,老炼资源覆盖率对比结果如表3所示。

表3 老炼资源覆盖率对比

①只覆盖了16位数据位宽和真双端口读写模。

②I/O使用率能够达到100%,但是I/O内部资源覆盖率只有10%~20%。

对比结果表明,采用多段程序刷新的方式对电路进行老炼,可显著提高老炼覆盖率。

5 结束语

FPGA制造过程中产生的潜在缺陷会导致器件出现早期失效,老炼试验的意义在于通过加速电路老化使集成电路快速进入失效率低且相对稳定的偶发失效期。由于FPGA结构复杂,单段动态老炼程序并不能使绝大部分逻辑资源进入动态老炼状态,达不到使器件进入偶发失效期的目的,可能使器件潜在缺陷无法暴露,通过多段程序刷新的老炼方法可弥补上述缺陷,实现更高的老炼覆盖率。