一种基于FPGA 的万兆以太网控制器

[吴震霖]

1 引言

随着以太网技术的快速发展,利用以太网承载各种业务的需求也日益增强传统的千兆以太网已不能满足网络对传输带宽的要求[1,2],因此,需要运用更高速率的以太网技术解决传统以太网带宽不足的问题。万兆以太网遵循的标准是IEEE 802.3ae,传输速率可达10 Gbit/s,性能相比千兆以太网有了很大的提高[3]。万兆以太网控制器是协议层与传输媒介之间的桥梁,是实现万兆以太网技术的基础。

本文介绍了万兆以太网控制器主要完成的功能以及万兆以太网数据帧格式,并提出了一种基于FPGA 的万兆以太网控制器,该控制器包括万兆以太网MAC 模块和万兆以太网PCS/PMA 模块,进一步说明了该控制器的用户接口时序要求。最后,将设计的万兆以太网控制器在硬件平台上进行测试验证。

2 万兆以太网相关协议

2.1 万兆以太网控制器与OSI 参考模型的关系

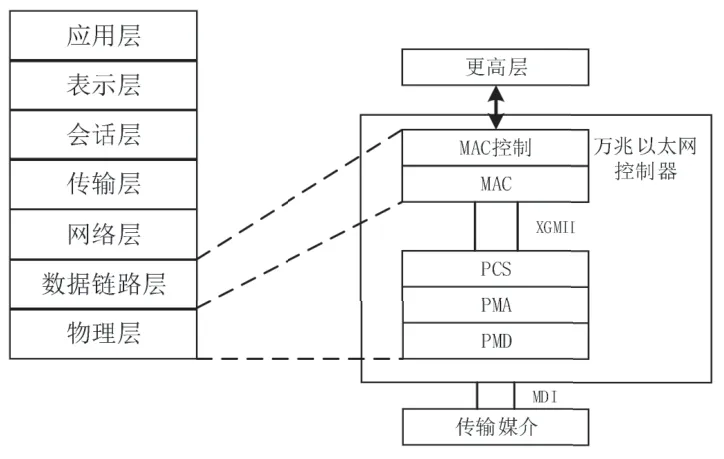

万兆以太网控制器主要完成了OSI 参考模型中的数据链路层和物理层的功能[4],如图1 所示。

图1 万兆以太网控制器实现的功能示意图

数据链路层包括MAC 子层和MAC 控制层子层,MAC 子层负责万兆以太网数据成帧和数据错误判决,MAC 控制层子层负责实时提供流量控制机制。

物理编码子层(PCS)负责对来自MAC 子层的数据进行64B/66B 编码和解码。物理介质附属子层(PMA)在发送方向负责将并行数据串行化,在接收方向负责串行数据流的时钟恢复,同时进行数据的串并转换。物理介质附属子层(PMD)负责信号的调制、放大、整形。介质相关接口(MDI)定义了不同的物理介质和连接器类型。

2.2 万兆以太网数据帧格式

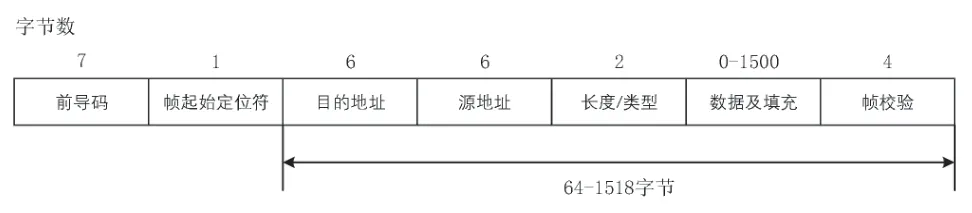

标准的万兆以太网数据帧格式如图2 所示,数据帧的传输顺序为从左到右,万兆以太网数据帧主要包括以下内容。

图2 万兆以太网数据帧格式

(1)前导码:用于数据帧同步,包括7 个字节的数据,内容固定为0x55。

(2)帧起始定位符:标志数据帧的开始,占用1 个字节数据,内容固定为0Xd5。

(3)目的地址:定义数据帧的接收方。

(4)源地址:定义数据帧的发送方。

(5)长度/类型:当该字段用于表示长度时,其值定义了数据域中的字节数量;当该字段用于表示类型时,其值定义了上层协议的类型。

(6)数据:由0~1 500 个字节的用户数据组成。

(7)填充区域:由0~46 个字节的填充数据组成,保证传输的数据帧长度不小于64 字节。

(8)帧校验:其值是对目的地址、源地址、长度/类型、数据、填充区域字段进行CRC 校验所得。

3 万兆以太网控制器设计

3.1 整体结构

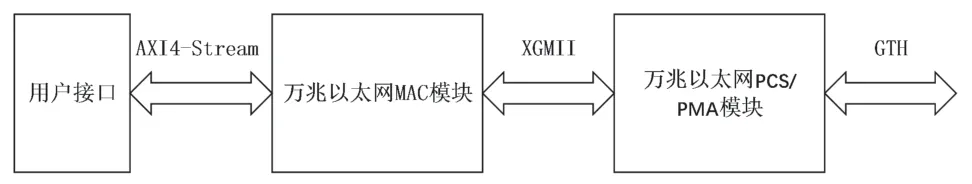

万兆以太网控制器的整体结构如图3 所示,包括万兆以太网MAC 模块和万兆以太网PCS/PMA 模块。万兆以太网MAC 模块主要实现了数据链路层的功能,万兆以太网PCS/PMA 模块主要实现了物理层的PCS 和PMA 子层功能,两个模块之间通过XGMII 接口互连。万兆以太网MAC 模块通过AXI4-Stream 接口与上层协议交互,万兆以太网PCS/PMA 模块通过高速串口GTH 与光模块交互。

图3 万兆以太网控制器的整体结构

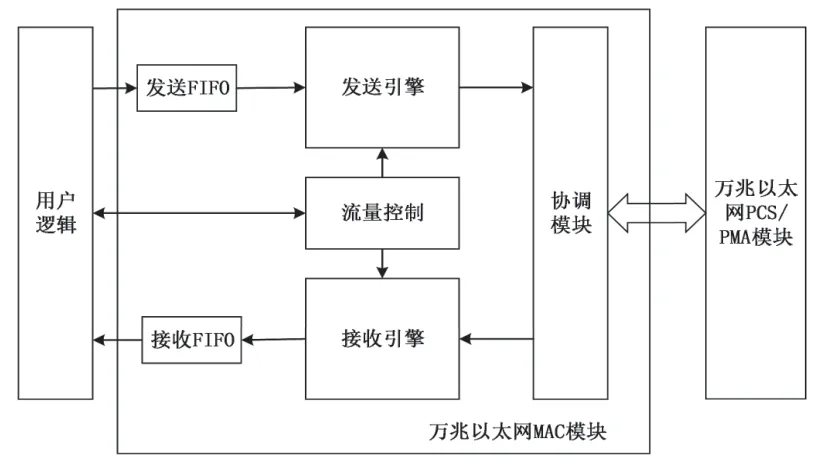

3.2 万兆以太网MAC 模块

万兆以太网MAC 模块组成如图4 所示,包括发送引擎、接收引擎、流量控制模块、协调模块、发送FIFO 和接收FIFO。发送引擎实现万兆以太网数据帧的组帧以及帧间隔的调整;接收引擎实现万兆以太网数据帧的解帧以及数据的错误校验;流量控制模块从接收到的PAUSE 帧中提取暂停发送时间信息,并根据该信息控制以太网数据帧的发送时间间隔;协调模块用于与万兆以太网PCS/PMA 模块的连接适配;发送FIFO 用于缓存用户逻辑发送给MAC 模块的数据;接收FIFO 用于缓存MAC 模块发送给用户逻辑的数据。

图4 万兆以太网MAC 模块组成

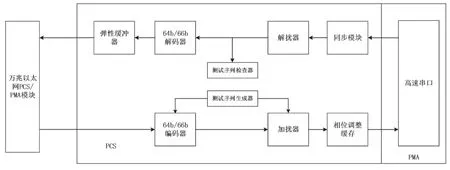

3.3 万兆以太网PCS/PMA 模块

万兆以太网PCS/PMA 模块组成如图5 所示,其中PCS 子层包括64b/66b 编码器、加扰器、相位调整缓存、64b/66b 解码器、解扰器、同步模块、弹性缓冲器、测试序列生成器和测试序列检查器,PMA 子层包括高速串口。

图5 万兆以太网PCS/PMA 模块组成

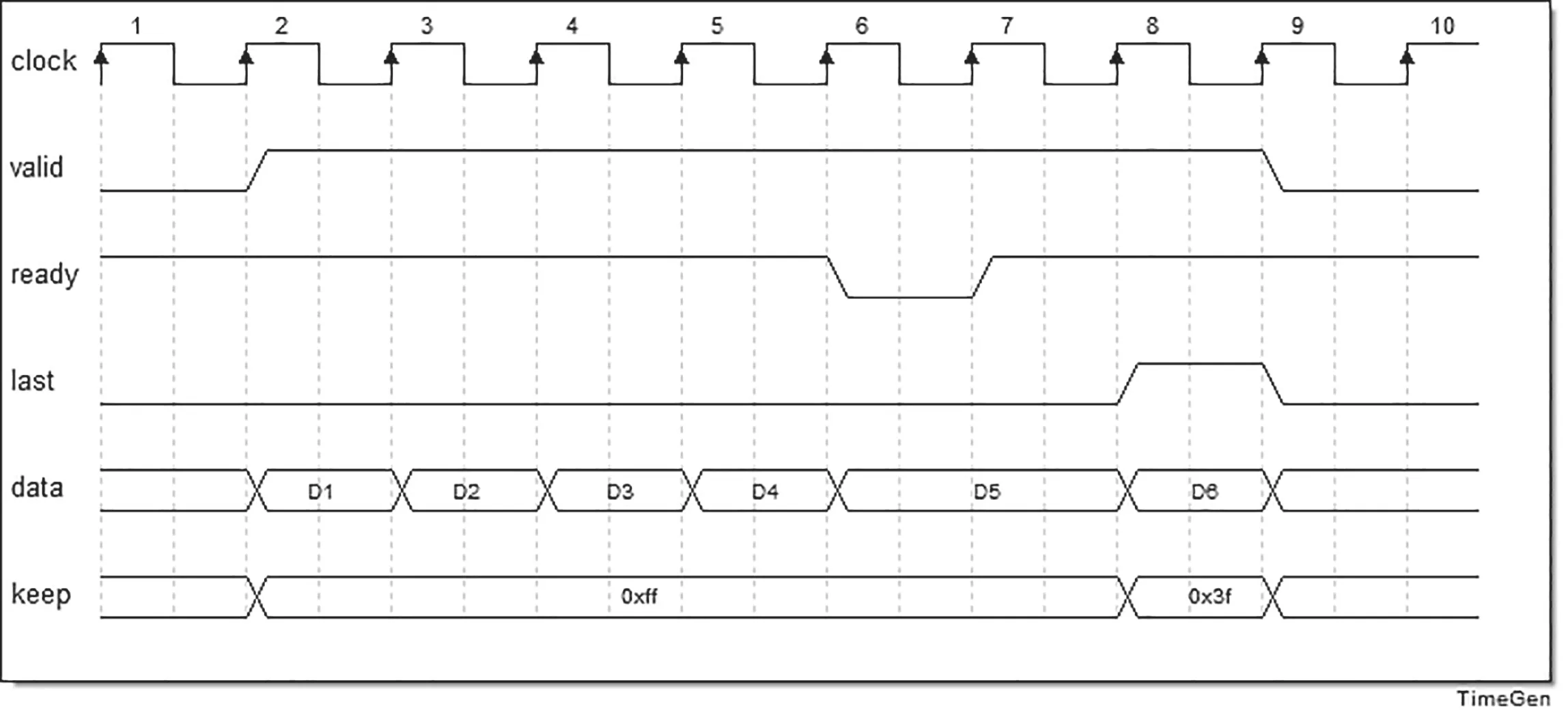

3.4 用户接口时序

用户接口与万兆以太网MAC 控制器之间通过AXI4-Stream 接口进行数据交互,AXI4-Stream 是面向数据流的传输,基于valid/ready 的握手机制数据传输协议,数据的发送方成为主机,数据的接收方成为从机,AXI4-Stream接口的时序如图6 所示。主机使用valid 信号表明数据的有效性,从机使用ready 信号表明自己能够接收数据,keep 信号表明数据字节组的有效性,last 信号表明数据帧传输结束。

图6 AXI4-Stream 接口的时序

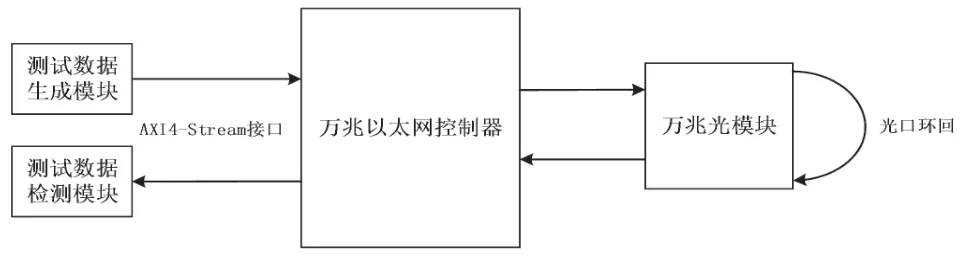

4 硬件测试

万兆以太网控制器仿真测试电路框图7 如图所示,FPGA 的高速串口外接万兆光模块,利用光纤对万兆光模块进行环回,测试数据生成模块根据标准的万兆以太网帧格式生成AXI4-Stream 数据流。启用测试数据生成模块后,它将以配置的最小帧大小开始,并在每帧之后发送,增加帧大小,直到达到最大值,然后再以最小帧大小再次开始帧发送。测试数据检测模块对正被接收的数据提供了一个简单的完整性检查。它使用与测试数据生成模块相同的控制向量,因此期望接收到的数据帧具有相同的帧内容和帧大小增量。监视器首先通过捕获到第一个完整帧的类型/长度字段中的值,判断该帧所在的位置,然后就可以预测下一帧的长度将逐渐增大。如果检测到错误数据,则在不匹配的字节的位置使能错误标志,错误标志将被采样输出。

图7 万兆以太网控制器测试电路

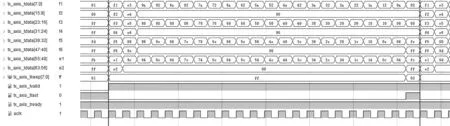

测试数据生成模块生成的数据流中其中一帧数据如图8 所示,数据从控制器的用户接口输入,经过控制器处理之后从高速串口发送端发出。测试程序希望发送一帧数据时,使能tx_axis_tvalid 信号,同时在同一时钟周期上发送数据tx_axis_tdata 和控制信号tx_axis_tkeep。控制信号tx_axis_tkeep 表明发送数据中的有效字节。当数据被控制器接收之后,使能tx_axis_tready 信号,测试数据生成模块准备下一时钟周期的数据。如果tx_axis_tready 没有使能,测试数据生成模块必须保持当前的有效数据和控制信号。tx_axis_tlast 信号有效表明一帧数据的结束。

图8 测试数据生成模块生成的数据流

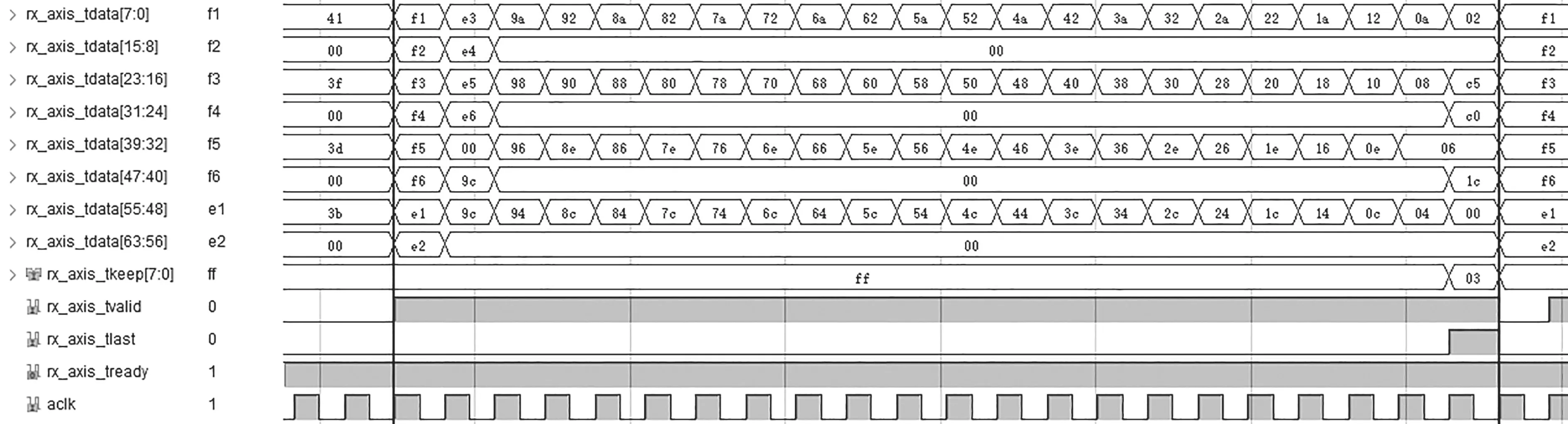

仿真程序设置高速串口环回,将高速串行数据环回到接收端,控制器恢复的数据流从接口输出,与发送端相对应的一帧数据如图9 所示,测试数据检测模块接收一帧数据时,在rx_axis_tvalid 信号有效时采样数据rx_axis_tdata和控制信号rx_axis_tkeep。控制信号rx_axis_tkeep 表明接收数据中的有效字节。当数据被测试数据检测模块接收之后,使能rx_axis_tready 信号,控制器准备下一时钟周期的数据。如果rx_axis_tready 没有使能,控制器必须保持当前的有效数据和控制信号。rx_axis_tlast 信号有效表明一帧数据的结束。

图9 测试数据检测模块接收到的数据流

经分析,测试程序发送给控制器的数据帧与控制恢复出来的数据帧内容一致,同时测试5 小时无错误标志信号输出,从而验证了控制器的功能。

5 结论

依据万兆以太网的标准,分析了万兆以太网控制器所需要实现的功能以及在OSI 参考模型中所处的位置,提出了一种基于FPGA 的万兆以太网控制器,该控制器可利用FPGA 内部逻辑资源实现,为使用万兆以太网技术进行组网提供基础。通过硬件测试,验证了该万兆以太网控制器能够为上层协议提供10 Gbit/s 的传输带宽,且传输性能满足要求。