基于SSD 控制器芯片测试平台转移及测试向量转换的方法

冯文星,余 山,周 萌,柳 炯

(赛迪工业和信息化研究院集团有限公司,江苏苏州 215104)

1 引言

随着移动智能设备呈井喷式增长,云计算、物联网、智能制造等新业态不断涌现,集成电路技术的发展也出现新态势[1]。在此大环境下,集成电路产业在我国如雨后春笋般蓬勃发展,如何生产高质量的芯片也逐渐成为人们关注的热点。在芯片生产过程中,芯片测试作为提高芯片性能可靠性的有效方法,是半导体集成电路制造过程中极其重要的一道工序[2]。而芯片功能测试主要基于价格昂贵的自动化测试设备(Automation Test Equipment, ATE)进行,不同型号规格的ATE,其单位时间测试成本相差很大。据估计,将来集成电路测试成本有可能占到整个产品成本的40%~50%,甚至更高[3-4],所以使用单位时间测试成本低的ATE 机台和缩短测试时间具有重要意义。本文针对不同测试平台的测试程序进行开发,对测试向量进行转换,来实现测试平台的转移。

2 芯片测试的参数要求

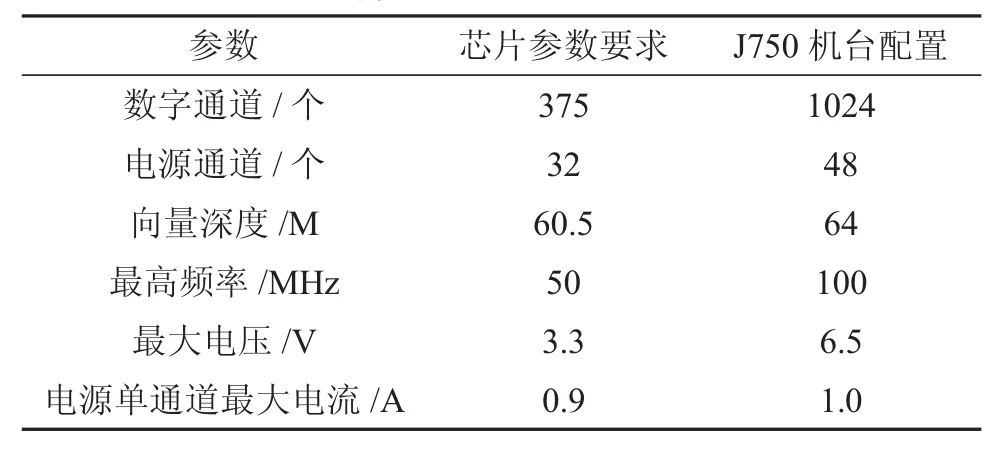

要实现芯片测试平台的转移,转入的平台需满足芯片测试的参数要求,否则芯片测试将无法进行,也不允许进行平台转移。研究将芯片测试从爱德万(Advantest) 的V93K 转移至泰瑞达(Teradyne)的J750,故对芯片测试参数的要求及J750 机台配置进行分析,具体参数见表1。

表1 芯片参数要求及J750 机台配置

根据表1 分析,需要测试的固态存储硬盘(Solid State Drive,SSD)控制器为纯数字芯片,所以配置有HSD800 数字板卡和HDDPS24 电源板卡的J750 测试机台即可满足芯片测试的要求。

3 测试平台转换的测试程序开发

高性能28 nm SSD 控制器是一款PCIe Gen3 x4、NVMe 1.4 固态硬盘主控芯片,支持容量高达2 TB。采用增强型无本地动态随机存储器(Dynamic Random Access Memory,DRAM)架构,支持主机内存缓冲区HMB 功能。其测试主要包含开短路(Open-Short,OS)测试、电源短路测试、漏电流测试、频率测试、功能测试以及Efuse 烧写及验证测试。其中Efuse 主要烧写芯片的产品型号、版本信息、晶圆批次号、芯片位于晶圆的位置坐标(X,Y)、漏电流、测试频率等。

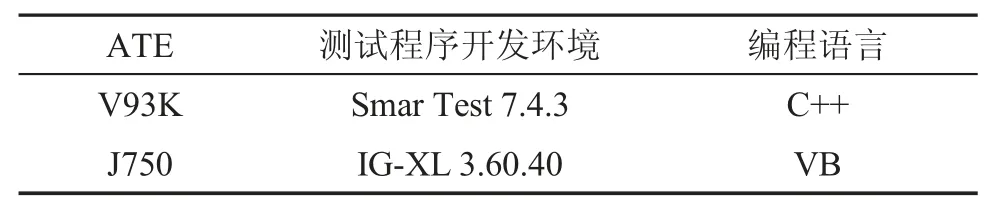

测试平台转换的测试程序开发主要涉及测试向量的转换和测试程序的开发调试。测试程序的开发可以按照两条技术路线进行:一是直接按照测试方案进行开发;二是按照原平台程序中所设置的相关参数在另一个转入的平台进行相同的参数设置,其语法和逻辑因平台不同,需要灵活设置,同时需要掌握这两个平台的开发环境及使用方法。对于V93K 原平台和J750 转入的平台使用的开发环境及编程语言如表2所示。

表2 ATE 测试程序开发环境

使用ATE 机台进行芯片测试程序开发,主要包含以下7 个步骤。

1)Channel Map 硬件资源的分配:根据芯片输入输出管脚、电源管脚,为芯片管脚分配ATE 硬件资源。

2)Level 电压的设定:根据芯片的设计参数设置输入电压(Vil、Vih)、输出电压(Vol、Voh)、电源电压(Vcc)等进行电压设定。

3)Spec 参数设置:芯片测试的加载电流、匹配电阻、限流、限压设置。

4)设置时序:根据芯片的时序逻辑等设置频率、时钟沿、输出信号比较方式(边沿比较还是窗口比较)、波形的形状等。

5)测试Class 的调用及开发:根据芯片测试的要求和不同的测试方法,需要在测试主程序中调用不同的测试Class,一般机台开发程序都带有基本测试模板Class。复杂及灵活的测试需要自己编写相关代码作为测试Class 来对芯片进行测试。

6)测试主程序的调用:Testflow 为主程序,其规定可测试的条件,调用相应的Level、Spec、时序、Class、向量对不同的测试项进行测试。Testflow 还规定测试项的先后顺序。

7)测试程序调试:调试时需根据芯片测试结果进行调整,修改Level 中的值,用Shmoo 工具来选择Vil、Vih、Voh、Vol等相关的值。另外根据测试结果还会对测试向量进行修改,一般需要芯片设计人员进行配合。

而针对转平台测试程序开发,因原测试平台已进行了相关的调试测试工作,所以转平台测试程序开发中一般不会修改上述步骤7 的Level 和向量,而是修改不同平台向量的格式,从而节约调试时间。

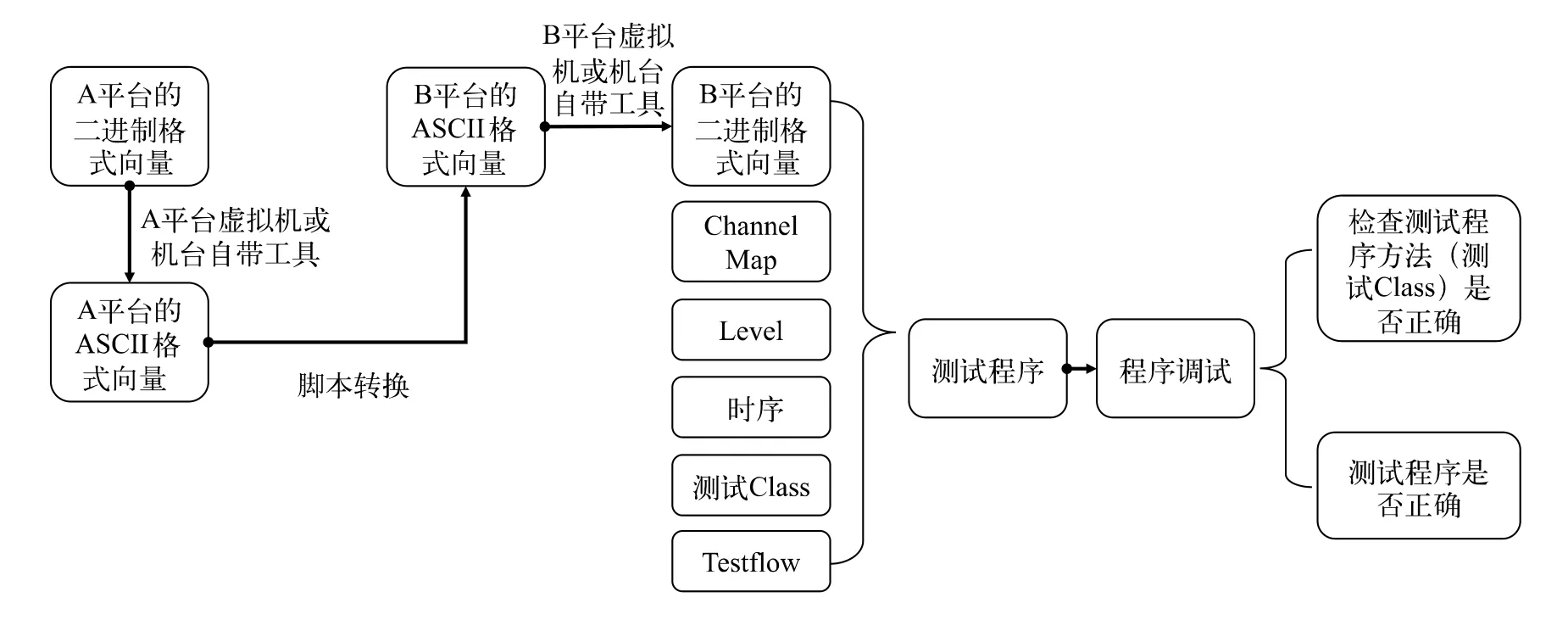

转移测试平台进行测试程序开发的主要流程如图1 所示。对于此项目,V93K 为A 测试平台,J750 为B 测试平台。

图1 转移平台测试程序开发流程

转移平台测试程序开发中除了Efuse 测试程序外,其他OS 测试程序及功能测试基本上都是使用J750 自带模板,以下重点介绍Efuse 程序的开发。

此SSD 控制器具有64×32 bit 的Efuse,其使用一次性可编程(One Time Programmable,OTP)存储器。OTP 存储器具有高可靠性、稳定性、抗辐射等特性[5]。如对OTP 进行烧写,首先需检验OTP 是否被烧写,若已被烧写则不进行烧写。烧写时,芯片首先进入OTP烧写模式,将烧写的信息转换为二进制数据,然后配置烧写地址。根据协议,此烧写采用JTAG 协议将数据信息烧写到相应地址,烧写完成后再读出相应地址的信息。之后将读出的信息与烧写的信息进行比对,来验证烧写信息是否正确。烧写流程如图2 所示。

图2 OTP 烧写流程

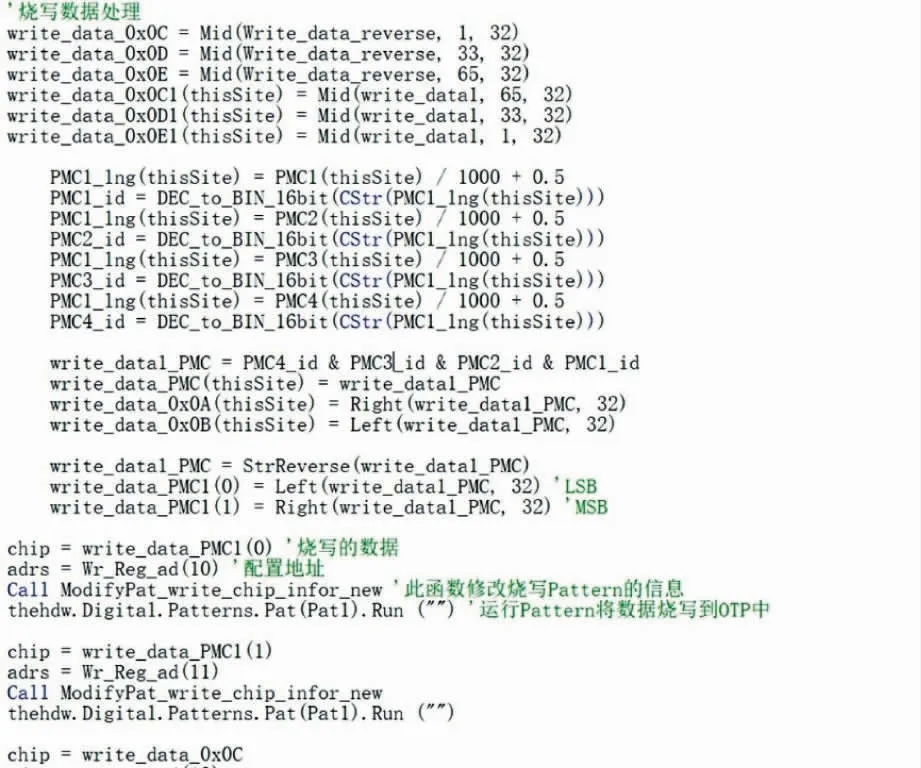

使用ATE 测试机台进行OTP 测试,将被烧写的数据转化为向量中的0、1 数据,然后运行测试向量可将烧写的数据烧写到OTP 中。OTP 测试过程中关于OTP 数据处理、配置地址、最后烧写的部分代码如图3所示。

图3 OTP 测试部分代码

通过对芯片测试程序的开发,测试芯片的功能得以实现。芯片测试程序开发是芯片测试的重要环节,要保证芯片测试的相关参数设置正确,测试时间符合规定要求,测试方法满足要求。在测试程序开发中遵循并行测试原理。在J750 测试中,可以定义向量组进行测试,即一个测试项可以同时运行多条向量,这对于测试向量较大的扫描测试来说可以提高测试效率,从而节省测试时间。同时通过程序并行优化,可以减少不必要的操作,这样可以将芯片一个Touch Down的测试时间从原先的14.05 s 缩短为12.08 s,效率提升11.08%。一片晶圆的测试可以节省35 min。

4 测试平台间的测试向量转换

由于不同测试平台间向量规则和时序设置不同,原测试平台上的向量规则不再适用于转入的测试平台,故需要对向量进行转换,对时序进行重新设定,从而使得测试平台施加的激励与其响应一致。故进行脚本转换之前首先需了解V93K 的向量规则和时序的特点,并针对J750 的向量规则和时序特点,将其转化为J750 的向量和时序。

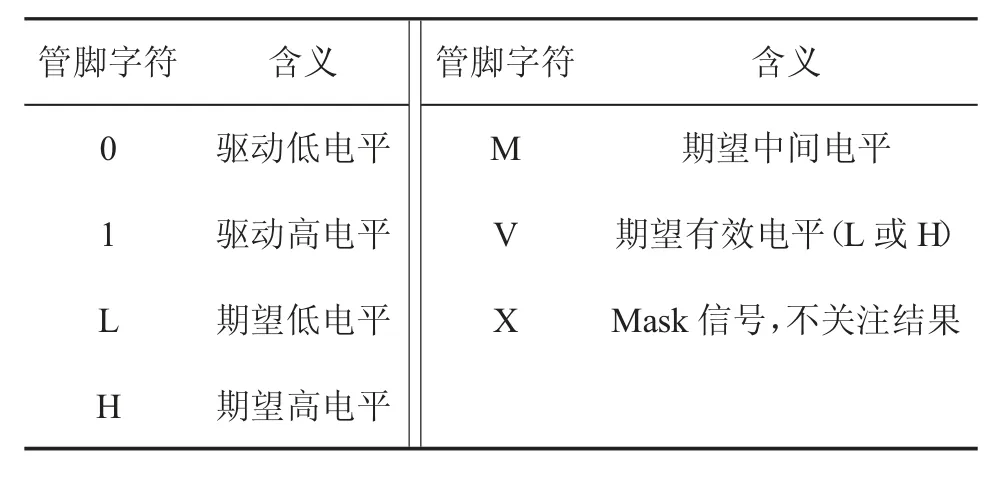

利用Python 语言进行向量转换时要涉及到一些特殊的向量字符。在V93K 中可以自行定义任意的字符来表示不同的波形含义(具体下文将详细解释),而在J750 HSD800 向量的格式中字符及其含义是固定的,常用的有0、1、L、H、M、V 和X,含义解释见表3。V93K 和J750 波形产生的机理也不同。J750 是按照wave format 来产生波形的。图4(a)展示了J750 常用的几种波形格式(NR、RL、RH、SBC、SBH、SBL)在扩展模式下的波形,从中可以看出J750 向量中的相同字符(0、1)在不同波形格式下的波形是不同的,二者相结合,可以构造出J750 所需要的波形[6]。而V93K 是按照数据沿来构造波形的,在相应的位置沿给驱动1 和0,则会产生不同的波形。1“d1:1 d2:0”1 代表的波形如图4(b)所示,在d1 沿处进入高电平,在d2 沿处进入低电平。由此可以看出,二者的数据结构方式不一样。在对V93K和J750 的时序和向量进行转换时,需对二者的字符在各自不同的波形格式中表示的波形形状进行比较,将V93K 中特殊的向量字符转化为J750 对应的字符,同时二者对应的字符所表示的波形需一致,另外也要达到转化后满足J750 向量格式的要求。

表3 J750 向量中字符的含义

图4 J750 与V93K 波形构造的差异

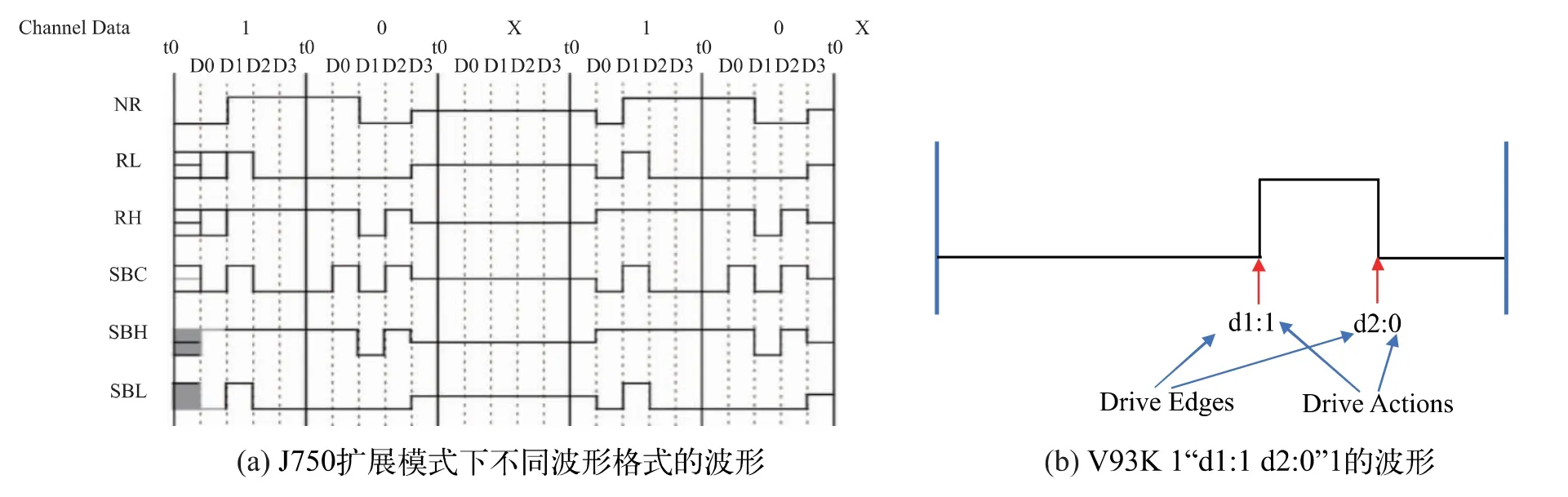

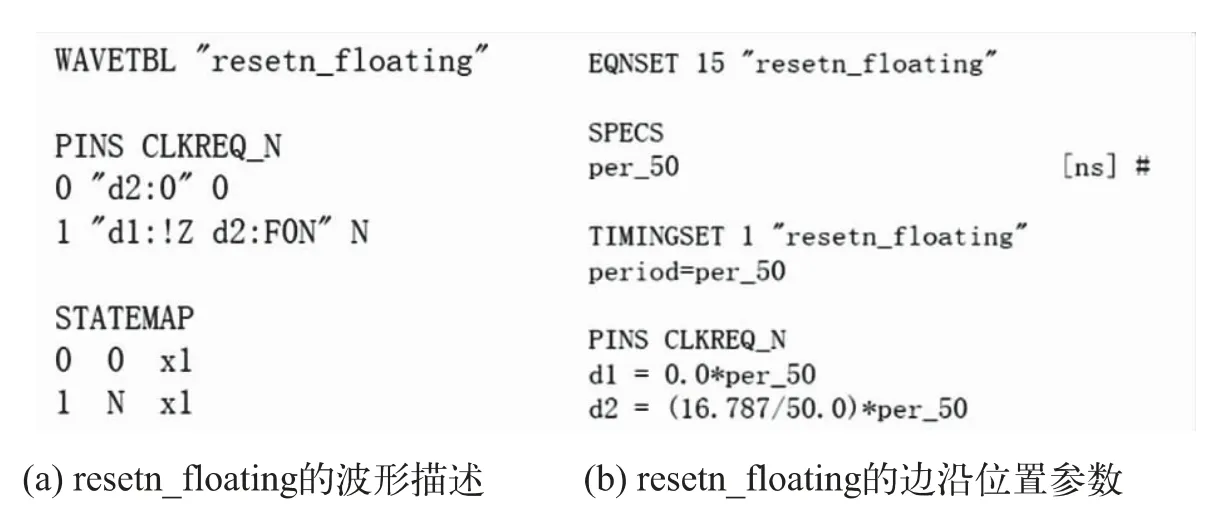

V93K 的时序周期参数如图5 所示,主要包含周期、边沿位置、波形等参数。以一个名为“resetn_floating”的时序为例,其使用的波形格式(WAVETBL)为“resetn_floating”,周期参数(SPECSET 1)为“resetn_floating_50”,其周期为50 ns。

图5 V93K 的时序周期参数

图6描述了管脚(CLKREQ_N)的波形,规定边沿的位置为d1 和d2,也自定义了字符0 和N 的含义来描述波形。其描述的波形为:当CLKREQ_N 在向量中的信号为0 时,在d2 处降为低电平(0“d2:0”0);当CLKREQ_N 在向量中的信号为N 时,表示在d1 处关闭高阻态,再在d2 处进入低电平(1”d1:!Z d2:F0N”N)。其中边沿d1 位置为一个周期的0 时刻,d2 为一个周期的16.787 ns 时刻。

图6 V93K 中管脚CLKREQ_N 的波形形状和边沿位置参数

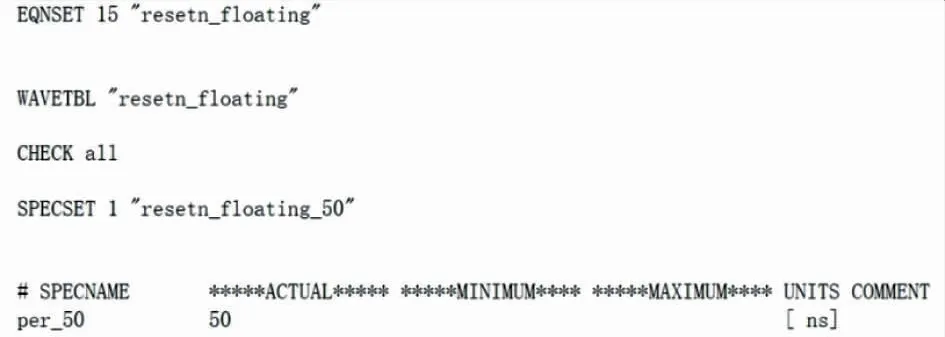

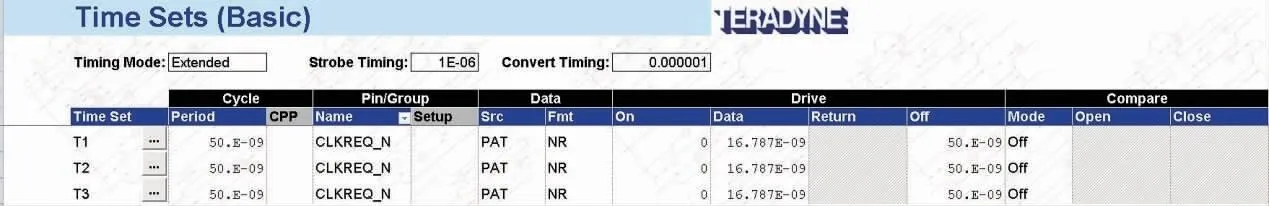

J750 的时序设置格式如图7 所示。不同于V93K中一个管脚中不同的波形格式需采用不同的字符来表示,J750 中一个管脚的波形格式需借助时序中Time set 来实现,此处设置了T1、T2、T3 三种格式的时序。根据管脚(CLKREQ_N)的V93K 波形,J750 设置其周期为50 ns;此管脚CLKREQ_N 的时序设置表示在D1沿16.787 ns 时刻进入驱动,若向量为1 则驱动为高电平,若为0 则驱动为低电平。根据V93K 的时序格式,CLKREQ_N 转为J750 的向量应该都为0。其他管脚(如GPI0、TCK、PERST_N、TMOD 等)的转换与此类似,这样即实现了从V93K 时序向J750 时序的转换。

图7 J750 时序格式

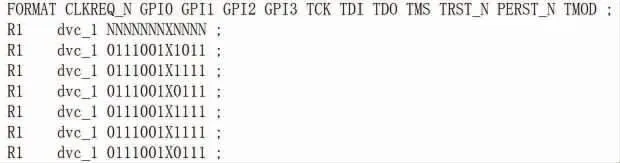

V93K 的向量格式如图8 所示,第一行向量中“FORMAT”为关键字,后边以空格分隔的为管脚名称,最后以分号结尾。第二行到最后一行依次为各周期中各管脚依次施加的信号,其中R1 表示只执行一次不进行循环,若为R100 则表示循环100 次。dvc_1为关键字。

图8 V93K 向量格式

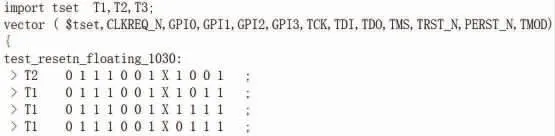

J750 的向量格式如图9 所示,第一行中首先导入时序设置中的Time Set,设置了3 种不同的波形T1、T2、T3 格式,第二行中vector 为关键字,括号中$tset后为各管脚名称,管脚之间以逗号隔开。第三行大括号后为测试相关的信号,“test_resetn_floating_1030”为第一行向量的一个标签,其名称与向量名称保持一致,其标签也可不进行设置。V93K 的向量转为J750的向量重点是向量描述的波形要一致,此也是转测试向量的难点所在。故测试向量转换中需明确J750 中每个周期使用的时序,如图9 所示,第一个周期使用的是T2 时序,第2~4 个周期使用的是T1 的时序,在不同时序下,即使向量字符相同,描述的波形也不一定一致。

图9 J750 向量格式

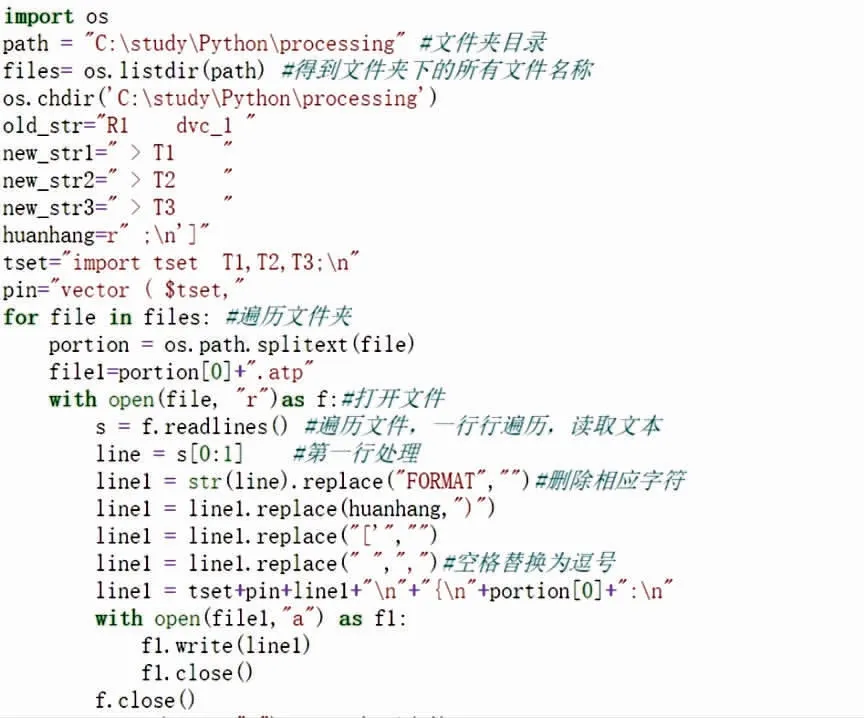

根据V93K 和J750 向量格式的不同,图10 所示的Python 脚本程序可实现将V93K 第一行的格式转化为J750 向量前四行的格式。

图10 实现格式转换的Python 脚本程序

V93K 中向量的相关字符转换为J750 的相关字符可以通过具体的字符查找替换来实现。根据信号字符的规则,需将N 替换为1 或0 等,替换后的信号需用空格隔开。实际脚本转换过程中使用Python 中的replace、join、字符串切片等函数,可以实现相应位置的字符替换、字符串替换以及相应字符间插入空格,以使转出的向量满足J750 向量格式的要求。通过增加条件语句,解决每个周期中使用的时序(T1、T2、T3)。脚本如图11 所示。

图11 实现字符串转换和修饰的Python 脚本程序

相比V93K,J750 中最后一行需要加“halt”关键字来表示这个向量的向量施加结束,最后用“}”包围。故利用如图12 所示的Python 脚本程序来实现。

图12 实现J750 向量结束的Python 脚本程序

通过以上Python 脚本程序即可实现对应时序的向量转换。转换时将被转换的V93K 向量放入指定的文件夹下,例如“C:studyPythonprocessing”,运行此程序,则可生成J750 的ASCII 码格式的向量,最后使用J750 的虚拟机或机台自带的向量转换小工具“Pattern compiler”即可转换为J750 机台使用的二进制格式的向量。

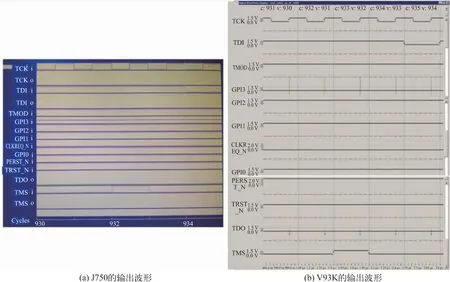

5 测试平台间的测试数据比对

为了验证测试程序中向量转换的正确性,采用V93K 的工具和J750 的工具来分别观察同一个向量转换后的波形,转换后的波形如图13 所示。从中可以看出,针对同一个向量,两个ATE 的实际输出波形一致,由此证明测试向量转换有效并可行。

图13 J750 和V93K 对同一个向量转换后的输出波形

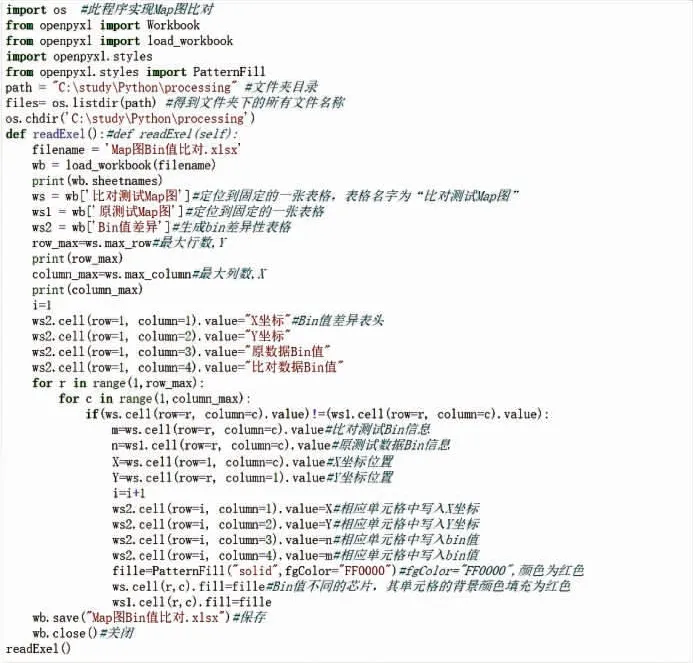

为验证不同测试平台转换后测试结果的一致性及有效性,测试后对不同测试平台得到的数据进行比对。由于此项目测试的SSD 控制器晶圆上有近4000颗die,人工逐个比较难以实现,所以开发了基于Python 的比较程序(如图14 所示)。利用此程序可以实现以下功能:

图14 基于Python 的比较程序

1) 将原测试Map 图与比对测试Map 图进行比较,并将比对的差异Bin 值数据放入Bin 值差异表格;

2) 将原测试Map 图与比对测试Map 图进行比较,对Bin 值不同的坐标进行突出标红显示。

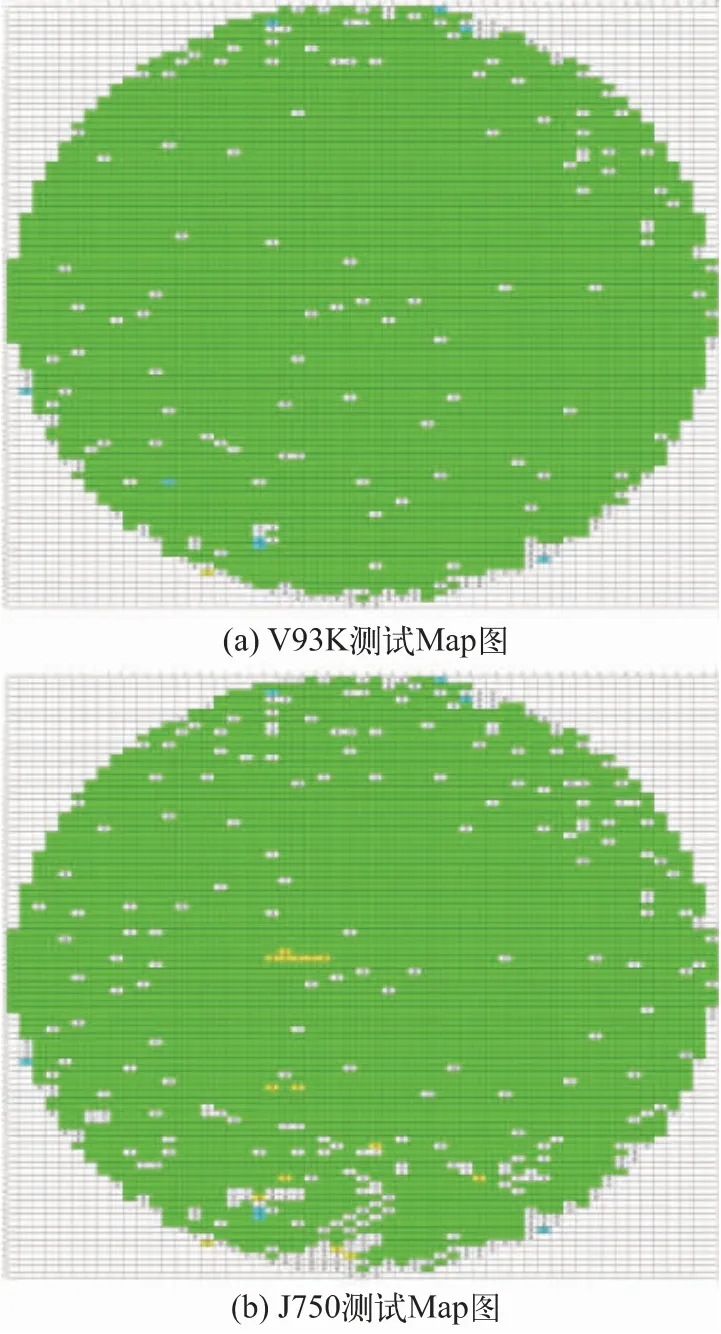

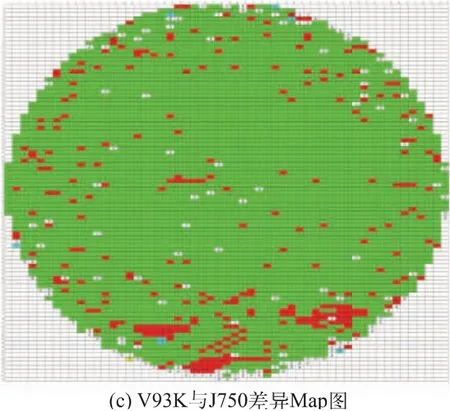

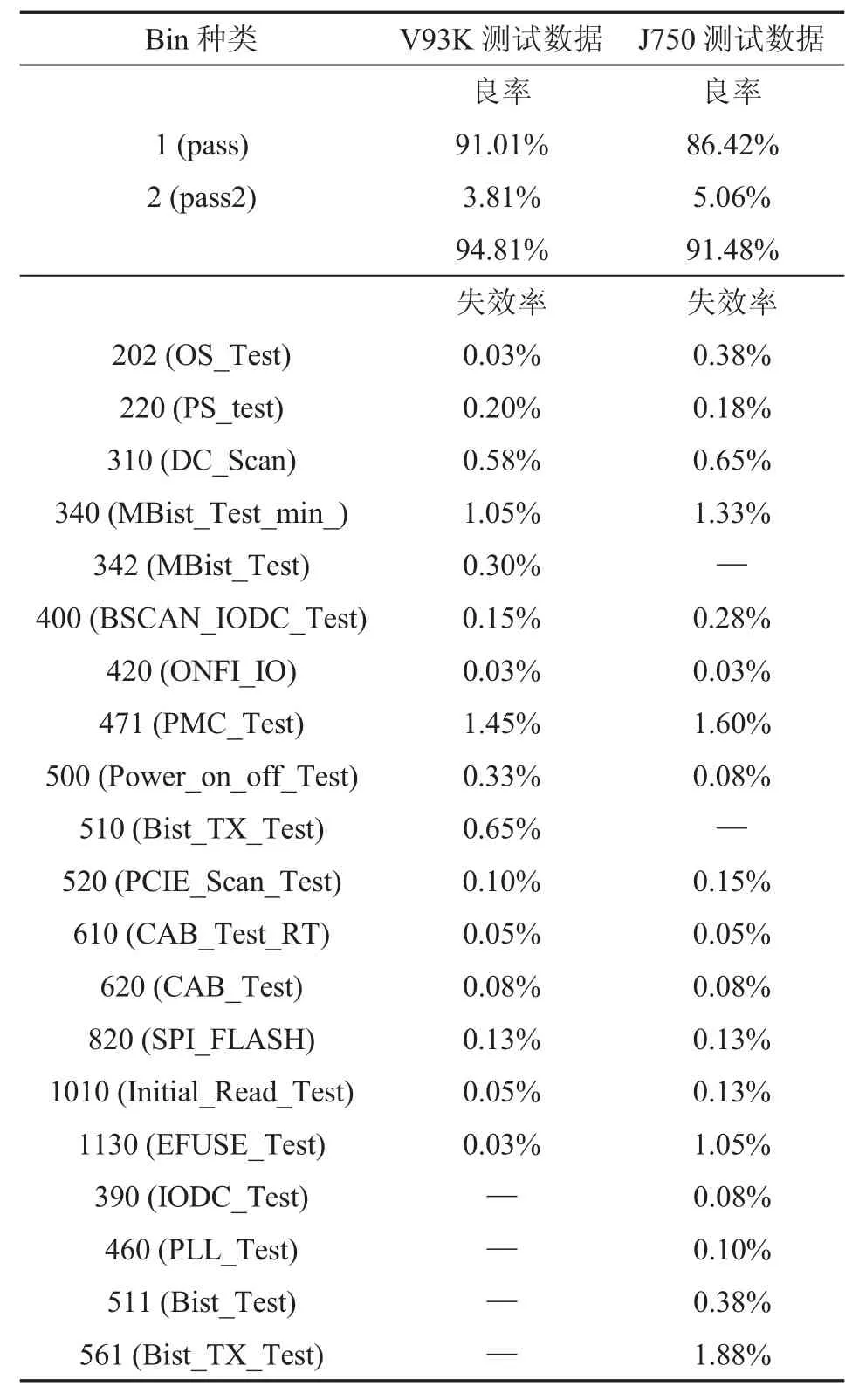

SSD 控制器在V93K 和J750 测试平台上得到的Map 图及基于Python 得到的Map 差异图如图15 所示。从中可以看出,测试的近4000 颗die 中有298 颗die 的Bin 值不一样,二者的差异率为7.5%。接下来又对有差异的Bin 进行了具体分析,结果列在表4 中。

图15 V93K 与J750 Map 图比对

表4 V93K 和J750 测试Bin 值差异一览表

从表4 可以看出,相比V93K 测试得到的良率,J750 测试得到的良率为91.48%,良率相差3.33%,略高于2%。这可能是由于晶圆多次测量导致芯片测试焊点接触不良造成的。而其他Bin 值显示的失效率均在2%之内,属于正常的良率范围[7]。由此可以说明J750 测试平台与V93K 对良品的判断大致一致,进而表明此项目测试方法的准确性。

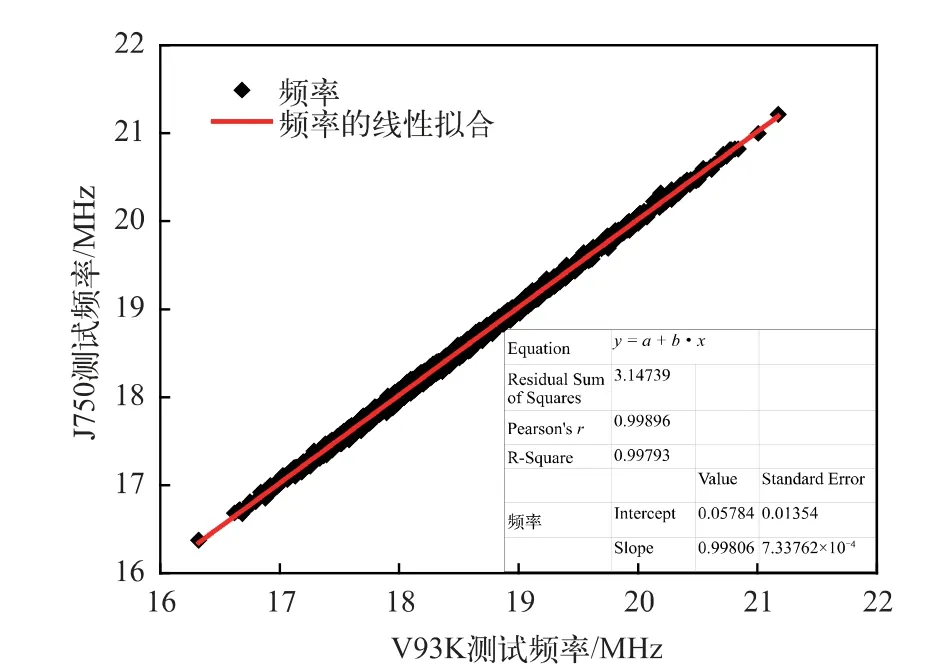

为了进一步验证测试数据的一致性,此文选取两个测试平台测量得到的频率来研究二者的相关性。PMC_Test 测试项测试得到的频率值总共有3845 个。针对V93K 和J750 对同一晶圆相同坐标位置的die 进行测试频率值比对,使用Origin 软件对3845 对测试数据做出的线性相关图如图16 所示。两个测试平台频率的相关程度通过相关系数r来表示[8],其计算公式如式(1)所示。

图16 V93K 和J750 测试得到的频率值的线性相关性

从图16 得到相关系数r为0.99896,约等于1,再结合V93K 和J750 测试数据得到的散点图,可以判断在V93K 和J750 测试平台上测试值线性相关[8]。

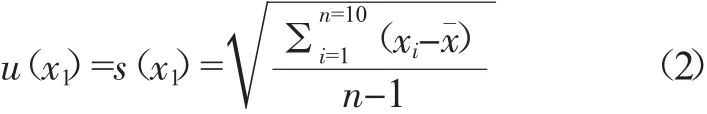

为了进一步说明两种ATE 测试频率的一致性,本文又对频率的标准不确定度进行了分析。使用J750 对一颗die 进行10 次循环测试。10 次测量的结果分别为17.955 MHz、17.940 MHz、17.938 MHz、17.938 MHz、17.945 MHz、17.948 MHz、17.930 MHz、17.938 MHz、17.925 MHz、17.920 MHz。重复测量采用A 类方法进行评定,用贝塞尔法计算不确定度[9]。10 次测量的算术平均值x¯=17.938 MHz。单次测量的标准不确定度按照式(2)计算[10]。

单次测量的标准不确定度为0.010 MHz,相对不确定度为0.056‰(标准不确定度除以算术平均值),测试的不确定性较小,再次说明测试结果较为准确,证明转移后的基于J750 测试平台的测试结果是可重现且有效的。

6 结论

本研究基于SSD 控制器芯片测试,将芯片功能测试从昂贵的V93K 测试机台转移到相对廉价的J750测试机台,得到准确且一致的测试结果。转移过程涉及评估平台转移的可行性,开发测试程序,对相关测试向量进行转换,最后对转换前后的波形进行比较,对测试结果进行评估,来验证测试结果的一致性和准确性。转移测试平台方法简单有效,测试向量转换方法可行且Python 脚本转换方案成本较低,可以满足实际生产测试的需求。同时在验证比对过程中,为了简化工作,开发了Map 图比对程序,对相关Bin 的差异进行比较,缩短了处理数据的时间。本文的研究内容将高端测试机台转移到低端测试机台,可行有效,能节省测试成本,对测试平台的转移有一定的参考意义。