防火墙并发连接数测试平台的研究与设计

胡少文 谈卫兵 章俊 黄浪鑫 余里辉

摘 要:由于当前并发连接数测试工具相对较少,操作复杂,且其只能测试吞吐量、时延、丢包率等参数,基于RFC2544国际测试模式中针对网络测试参数的技术要求,设计了一种高性能,高集成化的以FPGA为主控单位的具有并发连接数的测试模式的硬件开发平台。以Tele-Explore为软件平台,并通过自带的仿真器对防火墙的并发连接数进行仿真验证,仿真结果表明整个测试系统平台的搭建符合设计标准,能够满足防火墙并发连接数测试的需求,能为网络故障诊断和维护分析提供及时可靠地依据,进而满足人们对于网络服务质量更高需求,有效提供网络运行的可靠性。

关键词:FPGA; 并发连接数; TeleExplore;

中图分类号: TN91 文献标识码: A

0引言

网络测试技术与网络传输技术同步发展,早期网络传输速率较低,该阶段测试一般不需要专用硬件测试系统,就可以通过软件完成对网络协议一致性的分析测试,通过网络互连设备的动态交换信息,实现对网络协议正确性测试。目前,随着网络传输技术不断升级和网络应用日益扩大,不仅需要对网络传输测试指标进行更加详细的规定,还需要基于专用硬件系统平台完成对网络互连设备的传输分析和监控,方便实现用户现场网络维护的要求[1-5]。

并发连接数是其传输测试指标中的一个重要指标[1]。在IETF RFC 2647中给出了并发连接数(Concurrent Connections)的定义,它表示防火墙或代理服务器对其业务信息流的处理能力,是防火墙能够同时处理的点对点连接的最大数目,并且其反映出防火墙设备对多个连接的访问控制能力和连接状态跟踪能力。这个参数的大小直接影响到防火墙所能支持的最大信息点数[6-10]。

因此基于网络互连设备的并发连接数测试技术的需求,开发一套针对网络互连设备的高可靠性,高可用性和实时性的网络互连设备并发连接数测试系统,能为网络故障诊断和维护分析提供及时可靠的依据,进而满足人们对于网络服务质量提出的更高需求,有效提供网络运行的可靠性。这既是本项目研究意义的关键所在,也是国内外众多研究人员和企业共同致力研究的目标[11,12,13]。

目前,国内外有多家公司在从事网络测试系统方面的研发和生产,虽然已有几种高速网络测试系统产品问世,但这些仪器主要有国外公司所研制,其中较为领先的并发连接数测试设备有思博伦的Avalanche 3100,美国IXIA网络测试仪。下面对美国IXIA网络测试仪进行简单介绍:

1、统一的测试平台可以提供真正的2-7 层完整测试解决方案;每个端口都有独立的CPU,基于端口的多用户操作,大大提高使用效率;

2、 GE接口模块及支持多种接口类型的10G模块可以在±102ppm 范围内调整 帧发送频率,方便灵活;

3、测试平台支持超过1500个端口的 全网状流量测试。

4、全面,灵活,丰富的路由仿真、MPLS、电信级以太网、宽带接入等测试;

5、4-7层三重播放业务承载在动态路由表之上的QoE测试方法;

6、应用层协议支持的4-7层多重播放测试和信息安全测试;

7、全面的API 接口,“一键生成脚本”的强大自动化能力和“所见即所得” 的自动化编程环境,并提供全面的自动化测试管理工具。

以上这些由国外研制的测试设备,有时不能够满足国内的某些特定测试要求,其次它与国人的使用习惯有差别,不便于使用,同时国外产品价格昂贵。由于国内外通信网络具体情况的差别,为配合国内通信网络的迅速发展,研制出符合国内的高质量、高性能的网络测试仪是势在必行的。因此,国内的也越来越多厂商加入以太网测试系统方面产品的研发与设计,能够适应多种网络诊断和性能验证,功能强大且性价比优越[15-19]。

目前的网络性能测试工具只能测试吞吐量、时延、丢包率等参数,并且并发连接数测试工具还是比较少,而且操作复杂,效率低。针对这一问题,设计了一种高性能,高集成化的以FPGA为主控单位的具有并发连接数的测试模式的硬件开发平台就显得尤为重要,本测试平台采用型号为Virtex5-155T,(XC5VLX155TFF1136)的FPGA作为硬件平台搭建核心控制模块[20-24]。

1.硬件平台搭建

基于FPGA的网络测试系统,其核心部分为采用FPGA针对网络的MAC层数据进行收发,并在FPGA内容完成在互连设备传输过程中各个性能的统计与分析,且在FPGA上内嵌一个完整的,可移植、固化和裁剪的占先式实时多任务内核,完成对MAC层数据接收、发送、分析和与上位机通信整个过程的控制。下面具体设计采用以FPGA为核心的控制芯片进行硬件平台的搭建,如图1所示。

测试仪X86处理器上运行测试软件,然后通过处理器接口將控制数据发送给网络测试模块,配置好网络测试模块。网络测试模块的FPGA芯片完成报文的发送和接收处理,包括流调度,头处理,测试域处理等关键技术。处理后的报文再经过PHY芯片完成物理层处理,然后发送给被测设备,如交换机等。通过被测设备转发回来,由网络测试模块接收,进行相关接收处理后,将测试结果上传到X86处理器上运行的测试软件。

FPGA开发设计主要包括方案分析与代码设计、功能与时序分析和电路测试。FPGA设计特点并不是简单的顺序流程而是具有迭代性特点,一旦验证和仿真步骤出了问题,则回到之前的设计步骤重新检查、修改,最后直至符合设计要求,开发流程如下图2所示

FPGA开发设计,对系统进行详细规划和功能描述,其次,通过系统级仿真实现系统的性能考量和整体权衡。待系统确定整理功能后,就需要对系统进行划分功能模块,接口定义和协议描述,在此基础上进行方案之间的性能优劣比较,再根据性能指标要求优化方案满足设计需求。

系统功能模块与接口定义好后,就需要进行规划寄存器间逻辑功能实现。设计输入是把设计系统在开发需求确定后以某种形式表示出,再导入EDA工具的过程。常用设计输入方法主要有硬件描述语言(HDL)和原理图输入方法等。原理图输入是一种最直接的描述方式。需要将所需器件模块从元件库中导出,搭建原理图。这种方式便于理解,较为直观但不灵活,也不便于模块的重用和构建,因此,硬件描述语言(HDL)输入方式是当前主流设计方式。自顶而下的设计思想,通用性强和移植性好,容易实现模块的划分与复用。

再根据设计具体要求优化门级网表的组合,供FPGA布局布线进行实现,综合需根据给定的约束条件实现电路既定的功能设计要求,如功耗、速度、成本、芯片面积和电路的类型等,再通过计算机进行算法优化处理,最终获得一个能够满足要求或者相近最优电路设计方案。

根据硬件平台流程图及FPGA开发流程,基于PCIE总线设计,采用以太网背板交换技术,设计开发了一套能够支持10G、10/100/1000M测试模块,可实现2-7层全网络协议测试及仿真测试设备,设计开发的测试设备实物图如图3所示。

2.防火墙并发连接数测试软件平台搭建与设计

2.1 硬件环境配置

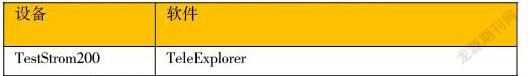

该系统的硬件主要是包括TestStrom200、防火墙ASA5510及5米cat5e的网线,具体配置如下

2.2 软件配置

安装在TestStrom200的软件是Tele-Explorer,它主要是运行在管理PC上对测试仪进行配置与管理的应用软件,主要配置如下:

2.3 测试拓扑及说明

(1)测试拓扑图如下图所示

并发连接数:DUT(测试设备)对多个连接的访问控制能力和连接状态跟踪能力,是衡量DUT性能的一个重要的指标。使用HTTP协议仿真可以测试基于HTTP的命令的并发连接数,以及基于TCP的并发连接数。每个测试项覆盖字节、速率和时长等参数调整。

3.防火墙并发连接数测试

3.1测试实物连接图

具体的测试实物连接图如下图所示:

3.2 测试过程

1. 将测试仪 1,2 端口分别和DUT的 1,2 端口连接,此处设置 DUT 的 1,2 端口的IP地址分别为:10.1.1.1/16, 20.1.1.1/16

2. 打开 TeleExplorer ,Resource Setup页面进行资源配置:添加并连接机框,预约端口

3. 配置测试仪端口和 DUT 端口在同一网段

4. 打开Protocol Emulation界面,切换到HTTP 标签页

5. 使用1端口做Client,2端口做Server,所以勾选1端口的Server,2端口的Client

6. 编辑 Client,在HTTP Commands 页面

Command Timeout 编辑为一个较大值 Destination 处选择 Chassis1-Card1-Port2-Server1:80 (注意:機箱和板卡号要选对) ,Connection 处选择 HTTP-Enable Pipeline

7.在Load Profile界面 Load Type 处选择 Concurrent Connections, Load Value 填写比预期稍大的值, Ramp Time 中填写一个合适的值(最好不超过每秒新建连接数的速率),在Max Concurrent Connections处填写一个大于 Load Value 的值

8. 编辑 Server,Request Timeout 填写一个较大值,比如600sec

9. 开始测试,打开 Statistics 页面,在该 Client 对应的 Concurrent Connections 列查看测试结果

在测试 基于 TCP 的并发连接数,则只需在第6步中,将 Connection 修改为 TCP 即可。

若测试 Server 的并发连接数,则需要在第6步中,将 Destination 改为 Server 的IP地址。

4.结论

设计了一种高性能,高集成化的以FPGA为主控单位的具有并发连接数的测试模式的硬件测试平台。并且通过对防火墙的并发连接数的测试,验证了该测试平台可以可靠地实现并发连接数的测量,进而满足人们对于网络服务质量提出的更高需求,有效提高了网络运行的可靠性。

参考文献

[1]林丹生. 硬件防火墙TCP并发连接数测试技术[J].软件,2014,35(03):108-110.

[2]赵飞燕,蔺勇. 基于FPGA技术的多路并行通信信号采集系统[J].现代电子技术,2018,41(19):27-30+35.

[3]张一荻. 基于FPGA的脉冲信号参数高精度测量技术研究[J].仪器仪表用户,2017,24(01):32-33+41.

[4]黄滔,叶立芳. 广域网并行TCP加速系统的研究与实现[J].中国新技术新产品,2014,{4}(08):18.

[5]吉根云,蔡勇. 基于建模的TCP拥塞控制机制的研究[J].淮阴工学院学报,2008,{4}(01):51-55.

[6]左延智,王娟,吴训吉,张宗鹏. 网络丢包在线检测算法研究[J].数字通信世界,2020,{4}(05):1-2+6.

[7]杨建明,朱玉,李诣烽,王冠南,金敏. 智能变电站网络性能测试研究与应用[J].江西电力,2020,44(04):2-6.

[8]侯溪溪,周卓,李天赋,杨亮. 基于TestCenter的AFDX网络性能测试技术研究[A]. 航空工业测控技术发展中心、中国航空学会测试技术分会、状态监测特种传感技术航空科技重点实验室.第十六届中国航空测控技术年会论文集[C].航空工业测控技术发展中心、中国航空学会测试技术分会、状态监测特种传感技术航空科技重点实验室:《测控技术》杂志社,2019:4.

[9]江淑明,仇润鹤. 移动通信网络节点性能的自动化测试平台的搭建与应用[J].科技与创新,2019,{4}(05):51-53+55.

[10]李旋,顾建新,李毅. 网络安全专用产品网闸性能测试方法[J].计算机系统应用,2019,28(01):233-238.

[11]戴祥. 基于网络性能测试仪的RFC3918软件方案设计与实现[D].南京理工大学,2019.

[12]韦梦园. 基于网络性能测试仪的RFC2889软件方案设计与实现[D]. 南京理工大学,2019.

[13]张天奇. 基于NFV的网络性能测量系统的设计与实现[D].南京航空航天大学,2019.

[14]冯欣. 基于FPGA的网络报文解析和性能测试单元的设计与实现[D].南京理工大学,2019.

[15]张家波,李哲,王超凡. 面向车联网的LTE网络性能测试与分析[J].计算机工程,2018,44(07):303-307+315.

[26]李哲. 基于V2X的无线通信网络性能测量与评价[D].重庆邮电大学,2018.

[17]俞海. 网络延时測试实验及分析[J].软件导刊,2018,17(02):192-194.

[18]王书诚,曹凡,叶荣军,雷霓,陈祖刚. 无线通信网络测量关键技术研究[A]. 中国造船工程学会电子技术学术委员会.中国造船工程学会电子技术学术委员会2017年装备技术发展论坛论文集[C]. 中国造船工程学会电子技术学术委员会:中国造船工程学会,2017:5.

[19]王加熙. 机载网络化测试系统网络性能综合评价研究[J].中国高新科技,2017,1(08):3-6.

[20]金燕,陈佳彬,陈尔言,王卫静. 基于RFC2544的千兆以太网性能测试的实现[J].浙江工业大学学报,2016,44(06):628-632.

[21梁保柱,刘仕华. 校园局域网络的性能测试研究[J].信息通信,2016,{4}(02):175-176.

[22]阿喜达. 基于JVM对NIO网络通信性能测试[J].阴山学刊(自然科学版),2016,30(02):32-34.

[23]赵硕. 网络性能测试系统功能模块的FPGA实现[D].南京理工大学,2016.

[24]徐娟. 矿井智能物流系统网络性能测试方法[J].工矿自动化,2015,41(07):98-100.

基金项目:基金来源:江西省科技厅,项目名称:基于物联网的智能养虾池智能控制系统平台设计与应用,项目编号:20202BBFL63047;

基金来源:江西省科技厅,项目名称:面向物联网DDoS僵尸网络安全生命周期的入侵检测大数据分析与监测平台,项目编号:20192ACB50028。

作者简介:胡少文(1987-08), 男,汉,江西南昌人,硕士,工程师,研究方向为物联网技术及信息安全