探讨混合微电路用多芯组瓷介电容加固

刘 丹

(四川工业科技学院,四川 德阳 618000)

多芯组瓷介电容具有较大的单位安装面积容量,所表现出来的抗机械应力非常强,等效串联电阻不高,凭借上述优势在混合微电路中得到广泛应用。多芯组瓷介电容的前身是片式瓷介电容器,经过改造与创新研发出来的新电容器,多芯组瓷介电容应用到精密堆叠技术、金属引线封装技术等,同时具有片式瓷介电容器和多芯组瓷介电容所有的特性,。除此之外,瓷介电容的容量损耗在温度频率影响下具有很高的稳定性,比较特殊的串联结构更是适合在高电压极长时间运行中应用,高电流爬升速率的情况下,在大电流回路无感型结构中具有较高的适用性。

1 多芯组瓷介电容器

1.1 多芯组瓷介电容结构与原理

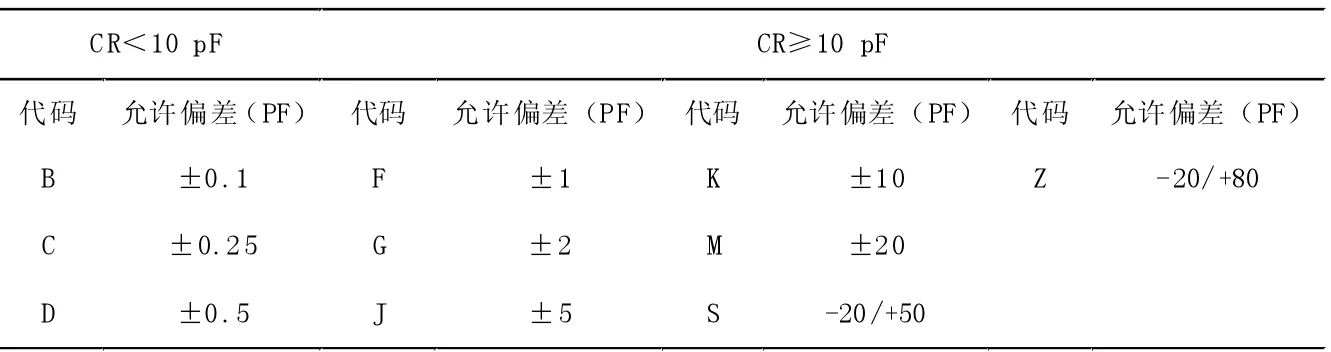

所谓瓷介电容,使用高介电常数电容器陶瓷,将其挤压之后形成圆管、圆片、圆盘等介质,利用烧渗法在陶瓷上以银镀为电极制作而成,主要有高频瓷介、低频瓷介两种类型(瓷介电容器参数见表1、表2、表3)[1]。作为电容器,正电容温度系数较小,在高稳定振荡回路当中使用,也被当作回路电容器、垫整电容器加以应用(电容器结构见图1)。多芯组瓷介电容是以片式瓷介电容器为基础,此类片式瓷介电容器在电子无源元件领域具有应用范围广的特点,然而体积比较小,所以无法达到大容量的效果。经过创新与改造之后,多芯组瓷介电容器将片式瓷介电容器容量方面的问题解决,利用精密堆叠(原理见图2)和封装技术(见图3),达到大容量效果,也使可靠性得到显著提升[2]。

表1 电容量温度系数(10-6/℃)

表2 电容量温度特性

表3 电容量允许偏差

图1 电容器结构

图2 精密堆叠技术原理

图3 封装技术原理

混合微电路中的多芯组瓷介电容为了保证其应用效果,一般需要予以加固,处于电容器制造领域,实际生产环节往往采用多芯组径向引线这一工艺,如此一来多层瓷介电容器的性能与功能得到完善,多芯组径向引线多层瓷介电容器生产与制造环节,电容器可能存在的外形尺寸超差这一现象便可得到解决[3]。夹具经过优化设计后叠片处理之后的多芯组径向引线多层瓷介电容器,不仅可以保证外形尺寸的规范性与整齐性,还有效控制了尺寸偏差。

1.2 多芯组瓷介电容类型

多芯组瓷介电容包括片式瓷介电容器、高温焊料和金属引线,组成了电容结构。①片式瓷介电容器是以普通的陶瓷电容器为主,并利用超过1 206 尺寸的电容器堆叠;②高温焊料的焊料是以共晶温度在240 ℃焊料为主,常见的有高铅焊料和锡锑焊料,此类材料支持二次焊接;③选择金属引线时,应该重点检查是否匹配片式瓷介电容器、高温焊料,可伐、锡磷青铜这一类材质的金属引线最为常见[4]。

根据片式瓷介电容器所使用的堆叠方法,多芯组瓷介电容有平行堆叠、垂直堆叠两种类型,而且分别体现出不同的优势与不足[5]。采用垂直堆叠方式的多芯组瓷介电容器,若干片式电容器在堆叠之后,重心不会发生改变,然而安装面积却会不断增加,导致高密度组装难度提升。

多芯组瓷介电容根据金属引线成型这一方法,也被划分为几种不同的类型,如“C”型、“J”型、“L”型等。每一种金属引线都会在相应的行业领域得到广泛应用,混合微电路使用的多芯组瓷介电容,通常以“C”型、“J”型多芯组瓷介电容为主。

2 多芯组瓷介电容焊接加固实验与分析

2.1 焊接加固原因

混合微电路本身可靠性比较高,在生产制造阶段基板主要利用氧化铝、氮化铝陶瓷,而焊盘则选择钯银、铂银两种材料。使用铅锡焊料在基板焊盘上方焊接多芯组瓷介电容,因为焊盘材质以银为主,所以经过回流焊、高温存储和老炼工艺的加工之后,受到热应力作用影响铅锡焊料、焊盘必然会有Ag3Sn、Ag4Sn 等金属间化合物产生,这种金属间化合物表现出不良脆性,一旦金属间化合物过量,便会对焊接界面电气性能、机械性能造成干扰[6]。经过以往焊接实践,发现回流焊作业之后,焊盘金属间化合物的厚度在2~5 μm 之间,处于150 ℃的高温存储环境,当时间不断延长,金属间化合物厚度也会随之增加,当存储时间达到24 h 之后,金属间化合物的厚度将增加至5~8 μm,如果存储时间延长至360 h,测量发现金属间化合物厚度将会达到16~20 μm。如果检测发现金属间化合物厚度已经大于20 μm,那么处于环境应力、机械应力多重条件下,焊接界面也会发生应力集中这一现象,增加了基板焊盘上方多芯组瓷介电容脱落的概率[7]。

2.2 焊接加固方法

要想切实提高混合微电路多芯组瓷介电容的稳定性与可靠性,建议在加固时采用硅橡胶、环氧树脂,对于已经焊接完毕的组件实施加固处理,可有效提高安装强度与可靠性。尽管辅助加固的方法也可以进一步改善焊接组件在安装时的强度,但是如果具体的加固位置、采用加固方法和加固胶量没有合理控制,便会在环境应力筛选过程中,导致所有材料之间的热膨胀系数偏差,从而造成组件失效[8]。针对多芯组瓷介电容加固方法进行设计,必须合理分析设计与实操是否可行、辅助加固实际的占用面积、多种类多芯组瓷介电容的兼容性。针对这三点因素,不建议针对设计中所运用的相应加固载片、粘接剂,采用以下两种加固方法。第一种加固方法,是将载片直接粘接在多芯组瓷介电容的底部,随后载片、片式瓷介电容器的中间接触部位涂抹粘接剂。第二种加固方式是在多芯组瓷介电容的一侧贴装载片,并利用粘接剂将载片、基板和载片、片式瓷介电容器连接。

上述两种加固方法,分别在环境应力、机械应力的环境下展开仿真分析,选择典型平行堆叠瓷介电容器、可伐材质的金属引线以及铅锡焊料。首先进行温度循环应力条件下的仿真分析,这里提到的温度循环,属于非常严格的环境应力筛选,按照《微电子器件实验方法和程序》中的相关要求,确定仿真分析的方法之后,将条件设置为C,温度在-65 ℃~150 ℃之间,两种加固方法分别展开仿真分析,其间观察完整温度循环期间产生的应力分布情况。根据仿真分析发现,处于温度循环期间,多芯组瓷介电容器所呈现的最大应力点,全部位于加固胶、瓷介电容器之间的接触位置,第一种加固方法的电容本体所能够承受的应力最大是34.5 MPa,第二种加固方法的电容本体承受应力最大只有14.0 MPa。瓷介电容器陶瓷层压烧结通常会选择钛酸钡一类材质,拉伸强度控制为70 MPa,处于温度循环期间,电容承受应力不会超过陶瓷材料呈现的抗拉强度。为了提高混合微电路的可靠性,建议温度循环建议超过100 次,材料反复温度循环时,极有可能发生疲劳、应力集中等现象,所以第一种加固方式可能造成电容器损坏。

针对上述两种加固方法展开机械冲击应力仿真分析,混合微电路筛选、使用期间,必然会面临机械应力,机械冲击、离心加速度是多芯组瓷介电容稳定性的直观影响因素。同样需要参考《微电子器件实验方法和程序》中提出的要求,确定加固方法,选择条件B,将峰值加速度设定为1 500 g,其中g 代表的是重力加速度,脉冲宽度则设定为0.5 ms,对于两种加固方法同时施加机械冲击载荷,观察机械冲击应力分布情况。根据仿真操作的观察,施加机械冲击载荷两种加固方法对应的最大应力点位置虽然不同,但是最大应力都比较小。第一种加固方法的最大应力点位于金属引线,测算最大应力是3.9 MPa。第二种加固方法最大应力点位于载片,测算其最大应力是6.0 MPa。综合分析之后可以确定,两种加固方法施加机械冲击载荷,其间不会发生多芯组瓷介电容受损的问题。

3 多芯组瓷介电容加固稳定性效果检验

按照以上提出的第二种加固方法,多芯组瓷介电容属于常规形式的平行堆叠瓷介电容器,根据《混合集成电路通用规范》中提出的要求,可以对多芯组瓷介电容加固稳定性效果进行检验。分别从高温存储、温度循环、机械冲击、扫频振动、随机振动、恒定加速度5 个维度进行检验,确定检验方法之后,按照上面5个维度依次设定检验条件如下:①存储温度为-150℃,168 h;②温度循环条件为C,进行100 个循环;③机械冲击设定为条件B;④扫频振动设定为条件A;⑤随机振动设定为条件F;⑥恒定加速度为49 500 m/s2,Y1方向。结束检验之后,测定多芯组瓷介电容加固功能,可以确定最终加固效果满足使用要求。

4 结论

综上所述,混合微电路使用多芯组瓷介电容器,在安装环节为了保证可靠性,针对多芯组瓷介电容一般会采取加固的方法。因为瓷介电容的材料不同,所以选择加固方法也有所区别。针对不同的加固方法,工作人员应该展开综合分析,探讨每种加固方法的优缺点,必要的情况下还可以展开试验分析,选择适用性与可靠性最高的加固方法,保证多芯组瓷介电容安装可靠性的同时,也可以为混合微电路的运行提供支持,继而有效提升多芯组瓷介电容加固水平,也为今后瓷介电容组装阶段的加固处理积累经验。