一款高线性度正电压控制的压控衰减器

许传栋,苏郁秋,董思源,李光超,周宏健

(中科芯集成电路有限公司,江苏无锡 214000)

在无线接收机系统中,为实现对信号幅度的控制,可变衰减器是极其重要的器件[1]。虽然信号幅度的控制可以通过可变增益放大器(VGA)来实现[2],但是VGA 芯片的线性度较差,不适用于接收机的射频前端。压控衰减器具有成本低、插入损耗小、频带范围宽、信号幅度变化线性度好、电路形式灵活、芯片可靠性高等优点,适用于微波系统的射频前端[3-5]。

目前已有学者对压控衰减器进行相关研究,Maecus Granger-Jones 等人基于SOI CMOS 工艺研制一款工作频率在0.05~4 GHz 的压控衰减器[6]。但是,SOI CMOS 的产品抗辐射能力较差,该工艺制造的芯片不能满足卫星通信的要求。国内白银超等人基于GaAs PHEMT工艺设计了一款工作频率在0.05~3 GHz的高线性度压控衰减器[7],但其控制信号为负电压,在实际工程应用中,正电压很容易实现,而负电压则需要特殊提供,加大了系统的复杂性。白元亮设计了一款正电压控制、工作频率为DC~4 GHz 的压控衰减器,但是需要引入额外的驱动电路,增加了设计的复杂度[8]。因此针对以上问题,该文设计了一款工作频率在1~6 GHz的正电压控制的压控衰减器,管芯选用噪声系数低、电阻率变化更小的D-mode PHEMT晶体管,通过电压浮地技术实现正电压控制,应用更广[9]。

1 电路设计

1.1 GaAs PHEMT等效模型

衰减器电路中GaAs PHEMT 管芯是集成电路的关键器件,管芯的电特性对电路的设计至关重要[10]。压控衰减器中,管芯工作在无源状态,即源漏之间电压很小,栅极加直流电压控制信号幅度,管芯的等效电路如图1 所示,当栅极电压变化时,栅下的耗尽层随之变化,相应源漏间电阻RDS同样改变。对于耗尽型晶体管,当栅压VG=0 时,栅下沟道全部打开,管芯处于导通状态,源漏间电阻等效为小电阻Ron,如图2(a)所示[11]。当栅压增大时,沟道缩小至截止,RDS增加,当VG>Vp(管芯的导通电压)时,RDS达最大值,源极和漏极之间等效为大电阻Roff和电容Coff的串联形式,如图2(b)所示。由上述理论,在ID不饱和,VDS较小时,PHEMT 管芯可以作为可变电阻,通过改变控制端VG电压,可以控制晶体管漏极和源极之间的电阻。在实际应用中,根据具体指标选择不同的晶体管,采用合适的衰减结构就能够设计电压可控衰减器[12]。

图1 无源PHEMT模型

图2 PHEMT导通和截止态等效模型

1.2 压控衰减器的拓扑电路

单片衰减器的基本衰减结构有三种:桥T 型、T型和π型[13],在这三种不同结构中,桥T 型衰减电路的插入损耗最小,同时衰减也可以达到较大的衰减范围,但是其工作频段内衰减平坦度最差;π 型衰减电路的插入损耗较小,但其工作频带内衰减平坦度也较差;T 型衰减电路的插入损耗也较小,同时衰减量也较大,工作频带的衰减平坦度也较好[14]。通过比较三种不同的电路结构,该设计采用T 型衰减网络。

T 型衰减电路的衰减量与串联电阻R1、R2、并联电阻R3的关系如下:

由上述公式可以得到,为实现压控衰减电路端口的良好匹配,主路串联可变电阻R1、R2,其阻值应控制在0~50 Ω,并联可变电阻R3的阻值控制在0~+∞。因此在电路设计中,R3由晶体管实现,R1、R2由晶体管并联一个固定电阻实现,电路的拓扑图如图3 所示。

图3 T型衰减器的电路拓扑图

1.3 管芯的选择和加电方式

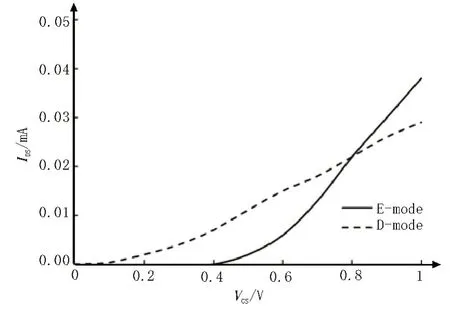

管芯的选择主要是根据管芯的线性度指标进行的,线性度越好,管芯的电阻变化率越小,压控衰减器的控制电压能够更精确地控制衰减量,同时衰减电路具有更高的稳定性和高低温特性。首先比较相同的管芯尺寸,如图4 所示,相同尺寸的D-mode 管芯和E-mode 管芯,两种曲线的VDS为1 V。从图4 可以看出,在电压开启后,E-mode 管芯控制电压低于0.4 V 时没有导通,在高于0.4 V后IDS迅速上升,表明阻值变化剧烈。D-mode 管芯阻值变化比较平缓,在电压变化范围内IDS缓慢上升,PHEMT 晶体管工作在相同功率时,D-mode 管芯导通电阻变化率较小,有着更好的线性度,利用这种晶体管设计的电压衰减器有着更高的输入三阶交调截取点[15]。

图4 PHEMT管芯的VGS和IDS曲线

对于耗尽型管芯D-mode,在传统的控制电路中,当栅极接-5 V 时,为高阻状态,当栅极接0 V 时,为导通状态。但在实际应用中,控制信号为正电压的应用范围更广,因此需要对传统的衰减器的电路结构进行改进,该文采用了电压浮地技术,其原理是在管芯的两侧源极和漏极加上偏置电压VC,其拓扑如图5 所示[16]。偏置电压VC=5 V 时,当栅极接0 V 时,栅源电压VGS=-5 V,晶体管处于高阻状态。当栅极接5 V 时,栅源电压VGS=0 V,晶体管处于导通状态[17]。在实际电路中,采用电压浮地技术,并在射频输入、输出端加隔直电容,可以将传统的负电压控制衰减器改进为正电压控制。

图5 电压浮地技术拓扑图

2 仿真和测试结果

2.1 仿真结果

压控衰减器基于0.25 μm GaAs PHEMT 工艺研制,选用ADS 2016 软件完成电路的仿真和整体版图的设计,采用图3 的拓扑结构,芯片内部的射频输入、输出端和接地端加载隔直电容抑制直流信号,最终优化压控衰减器的性能和尺寸,芯片尺寸为1.75 mm×1.35 mm×0.1 mm。

压控衰减器有一个供电端VC、两个控制端VT1和VT2。VC为5 V 直流供电,VT1变化范围为0~5 V,VT1、VT2电压变化关系为VT1+VT2=5 V。栅极加载20 kΩ电阻作为隔离电阻。

压控衰减器的仿真性能如图6 所示。输入、输出端的电压驻波比在工作频段内小于1.5,插入损耗小于2.3 dB,最大衰减量大于31 dB,动态衰减范围为0~28 dB,整个工作频带内平坦度在1 dB以内,控制电压的变化范围为0~5 V,衰减量随着电压变化具有良好的线性度,仿真结果符合设计要求。

图6 压控衰减器的仿真结果

在芯片设计中需要考虑静电放电(ESD)问题。为实现对芯片的静电保护,通常在电源电压VC和控制电压VT1、VT2的输入端串联二极管连接到地。电路正常工作时,二极管截至,处于断开态,当产生静电时,二极管雪崩击穿,导通到地,保护内部芯片。

2.2 测试结果

对流片完成的芯片进行探针台测试,测试仪器有Cascade 探针台、ACP-GSG-I50 微波探针、Agilent 5225B 矢量网络分析仪和稳压直流电压。芯片的偏置电压和真值表如表1 所示,测试结果如图7 所示。

图7 压控衰减器的测试结果

表1 真值表

通过对比仿真和实测结果,实测的输入、输出驻波比与仿真结果基本一致,驻波最大值仿真为1.5,实测为1.6,衰减动态范围和控制电压衰减曲线与仿真结果吻合,证明了该设计的正确性和工艺的精确性。对于驻波曲线的误差分析,主要原因如下:1)晶体管的S 参数测试数据误差;2)衰减器的内部分压误差;3)版图小型化过程中内部微带线之间的相互耦合。

3 结论

该文对压控衰减器的线性度和电压浮地技术进行了分析,采用0.25 μm GaAs PHEMT 工艺研制了一款正电压控制、高线性度的压控衰减器。其工作频段为1~6 GHz,控制电压变化范围为0~5 V。最终流片测试结果表明,压控衰减器插入损耗小于2.3 dB,最大衰减量大于31 dB,动态衰减范围为0~28 dB,整个工作频带内平坦度在1 dB 以内,芯片尺寸为1.75 mm×1.35 mm×0.1 mm,满足设计指标要求。