元器件失效分析在核级产品的应用

邓玉娇,陈荣华

(西安交通大学核科学与技术学院,陕西 西安 710049)

0 引言

电子元器件的失效分析可以追溯到20世纪40年代,即半导体和可靠性工程学科诞生之前的电子管时代。随着半导体技术的发展,以及电子信息技术的广泛应用,失效分析技术的发展越来越快,应用也越来越广泛[1]。在20世纪60年代,美国国家航空航天局(national aeronautics and space administration,NASA)、海军电子实验室、IBM、贝尔实验室、CALCE和波音等公司或机构就开始建立专门的失效分析实验室或机构。自1962年开始,每年举办的国际可靠性物理研讨会上[2]都有失效分析专题论坛或章节。1963年,IEEE组件封装与制造技术协会诞生,之后每年一届的电子元器件与技术会议[3]都会出现元器件可靠性与失效分析的专题学术交流,从而有效促进了失效分析技术及其应用的快速发展。失效分析技术的应用也由最初的简单电子管发展到大规模集成电路,为国家重大工程(包括火箭、飞机制造等)的发展作出了重要贡献。

集成电路产业的快速发展带来了许多新材料和新工艺的技术问题。大规模量产的生产趋势,引发人们对失效分析重要性和必要性的正确看待。电子元器件失效分析的发展也因此突飞猛进。

核级产品一旦发生失效或故障,所造成的损失和影响是巨大的。因此,核电领域从一开始就将产品可靠性放到安全考虑的第一位。在产品研制和使用阶段,必须对异常问题进行失效分析,并将其作为质量归零的前置和必备条件,以此保证核级产品应用的可靠性。

某核级项目实施过程中,某模块遇到多个相同问题:正常输入20 mA的理论输出是20 mA,而实际所有通道无输出。经分析:该模块输入通道±15 V供电异常,电源芯片的±15 V输出引脚与GND_COM短路,电路后级正常。分析结论是电源芯片内部短路故障。

本文对元器件失效分析方法进行介绍,并采用合适的失效方法对模块进行详细测试分析,确认失效问题及后续纠正处理措施。

1 失效分析技术简介

元器件失效分析是针对在工程运用过程中出现故障或失效的元器件进行的一种寻因检查[4]。通过失效机理、失效原因分析而获得产品改进的建议,可避免类似失效问题的发生,提高产品可靠性。而失效分析是一种借助各种测试技术和分析方法确定元器件失效根本原因的技术。失效分析技术通常包括外观检查技术、电性能分析技术、显微形貌技术、无损结构分析技术、开封制样技术、微区成分分析技术,以及失效复现和验证试验技术等[5]。失效分析的具体技术如下。

1.1 外部目检

失效分析一般从外观检查开始,主要对象包括失效元器件的外观、失效周边的微环境,以及开封后内部电路和外观。其目的是发现导致失效的直接证据。失效分析一般是无损的,主要通过显微镜检查。

1.2 电参数测试

电参数测试包括电性能测试、直流测试和失效模拟测试[6]。如阻容感抗测试、端口测试等,通过测试分析元器件的参数变化情况,为失效定位或分析方向提供依据。

1.3 内部分析

内部分析包括X射线检测、红外线显微分析和声学扫描显微分析、残留气氛分析、密封性检查等[6]。内部分析是失效分析的核心,可以观察任意区域的微观形貌和结构,从而探测低密度封装材料内部或界面的结构缺陷。

1.4 失效点定位

失效点定位时,器件必须开封,使芯片暴露出来。对于不同的封装材料与封装结构,可以采用机械或化学腐蚀的方法进行开封[6]。失效定位常用的方法为解剖制样。解剖制样技术是破坏性分析方法,主要用于制作元器件封装的关键截面切片,以便观察和分析元器件内部的结构缺陷和形貌。

1.5 确定失效机理

失效分析的最终目的是确定失效机理,找出元器件失效的真正原因。因此,必须从不同的角度、方法进行分析,以便给出解释元器件失效的合理原因,从而有针对性地提出改进措施[6]。

2 失效品详细分析

2.1 样品概述

`样品包括:失效品3只,编号为NG1#~NG3#;良品2只,编号为OK1#~OK2#。

样品失效信息:样品经过回流焊后失效,具体表现为样品的输出引脚与Common短路。

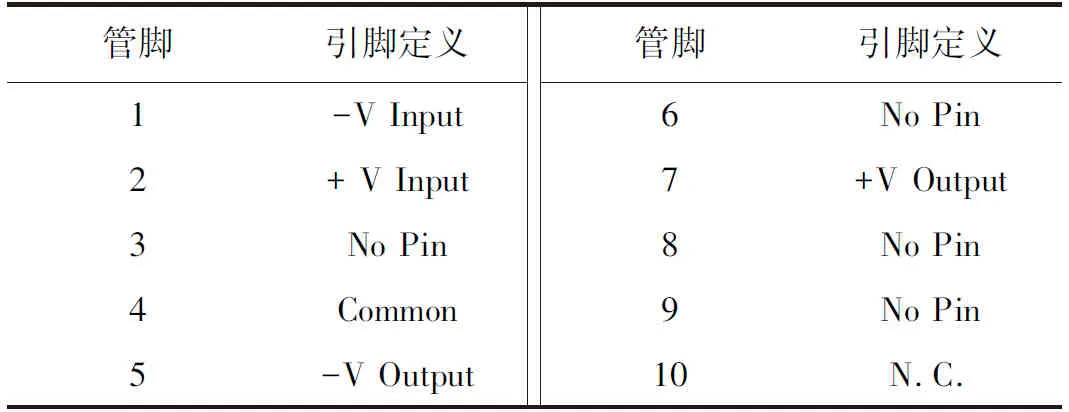

样品引脚定义如图1所示。

表1 样品引脚定义

2.2 分析过程

电子元器件是组成电子产品的最小单元。只有把好元器件质量关、从源头上进行质量控制和筛检,才能够有效提高产品质量和性能[7]。失效分析是元器件质量工作的重要环节。通过外部目检可以观察到基础的缺陷。随着电路集成化发展,不可见的缺陷越来越多,电参数测试、内部分析、失效定位技术应运而生。常见的光学和扫描电子显微、X光透射、开封、机械探针和解剖制样等失效分析技术被广泛应用。以下对第1节的失效分析技术进行详细阐述。

2.2.1 外部目检

为了检查样品在安装、试验和使用过程中引起的损坏,使用体视显微镜对样品进行外部目检。

样品为塑封模块,失效样品表面覆盖三防漆。去除三防漆后,样品的厂家、型号等字符标识清晰可见。所有失效样品的引脚残留焊料,外观未见过电烧毁或机械损伤。

2.2.2 电学特性测试

为了确定失效样品的失效特性、鉴别失效模式,使用晶体管图示仪对样品引脚间的I/V特性进行测试。

结果显示:NG1#和NG2#样品的输出端引脚PIN5(-V Output)和PIN4(Common)短路;NG3#样品的输出端引脚PIN7(+V Output)和PIN4(Common)短路。

2.2.3 X射线检查

为了检查样品封装内的缺陷、损伤,利用X射线检测系统对样品进行X射线检查。

失效样品内部元器件未见破损,PIN4、PIN5和PIN7引脚之间可见异常阴影。

2.2.4 CT检查

为了非破坏性地检查失效样品异常阴影的具体位置,利用三维X射线成像仪对NG2#样品进行CT检查。

检查结果显示,NG2#样品内部异常阴影灰度与焊料灰度一致,异常阴影区域分布在模块内部器件的引脚之间。

2.2.5 内部检查

内部检查是为了检查失效样品内部组装、互联结构是否符合要求,以及是否存在与失效模式有关的内部结构异常或缺陷,从而确定失效位置。

对NG2#样品进行研磨。研磨顺序是从样品的引脚侧向内部器件方向进行。将研磨样品进行CT检查,发现异常阴影位置:PIN4与PIN5引脚间的电容器下方塑封料存在空洞。该空洞斜向延伸,连接相邻引脚。同时,发现空洞内存在颗粒状金属,金属残留处与CT检查中发现的异常位置相同。对金属颗粒进行X射线能谱仪分析(energy dispersive spectrometer,EDS),其主要金属元素为铅和锡。

从NG3#样品的背面向内部器件的方向进行研磨,研磨到输出端电容器下方的塑封料位置,发现在PIN4与PIN7引脚间的电容器下方的塑封料内存在多处空洞。空洞内残留颗粒状金属,形貌与NG2#样品内发现的金属一致。

2.2.6 综合分析

NG1#和NG2#样品的输出端引脚PIN5(-V Output)和PIN4(Common)短路,NG3#样品的输出引脚PIN7(+V Output)和PIN4(Common)短路,与实际开封内部观察一致。

通过X射线检查,在失效样品输出端引脚间发现异常阴影。制作金相切片,在引脚间的塑封料内发现空洞。空洞在引脚形成桥连。空洞内部可见颗粒状金属残留。金属残留处与异常阴影的位置相同。通过对EDS作成分分析,确认残留金属的主要金属元素成分为铅和锡。铅和锡为焊料的主要成分。

在进行回流焊过程中,内部焊料受高温也会处于熔融状态。由于引脚间的塑封料内存在空洞,熔融态的焊料会填充到空洞中。样品内部的空洞连接了相邻引脚,故熔融的焊料填充在空洞中,造成了引脚短路。

3 失效品控制方法

由2.2节分析可知:失效样品由于其本身引脚间存在的质量问题,焊料会填充到空洞中,造成相邻引脚短路,最终使元器件失效。通过失效机理分析查明,本次失效原因是元器件固有质量问题。后期将针对性地加强物料采购筛选、回流焊接后测试过程的监控,并及时针对问题向生产厂家提出质量改进要求[8],通过建立相应的检验方案、采取优化措施等方式,避免问题再次发生。具体措施如下。

3.1 优化来料检验方案

目前,来料检验方案采用的是放宽政策,即使用统一的抽样检验标准——计数抽样检验,统计抽样的个数或缺陷的个数,仅计算单位产品中的不合格数,以此作为检验抽样依据。这种方案过于僵化。而核级产品属于安全级(1E级)电气设备,质保等级一级,应采用加严型方案。具体方案为:当产品质量正常时,采用计数抽样检验;当产品质量下降或过程不稳时,采用加严型方案,即批量全检方案,以保护使用方的利益[9]。

对来料检验过程实行全面的数据化管理,对所有质量异常数据进行记录反馈。根据前期项目经验总结,电源芯片属于制造过程及后续测试过程中易损坏的元器件,因此来料检验过程中对电源芯片类型的产品应采取加严型方案。发现异常模块后,应及时与供应商进行交流,反馈其质量检验异常数据,提示其进行改进。供应商对供货元器件进行系列排查,在采购元器件过程中把好质量关,使后续出现的产品异常显著减少。

3.2 增加产品功能测试

针对核级产品采用功能测试方法。该测试可对印刷电路板(printed circuit board,PCB)所有硬件接口、通信、精度进行综合性测试。功能测试比回流焊接过程测试覆盖面更广,更易发现隐藏问题。考虑核级产品的安全性要求高,该功能测试为全检测试,不采用抽检等其他形式。

功能测试是发现产品异常的关键性测试。增加该测试,可有效减少不良品往后流转的可能性。

3.3 建立故障报告、分析和纠正措施系统

电子产品及其所用元器件的可靠性分析、评价和改进都离不开故障信息。建立故障报告、分析和纠正措施系统的目的是保证故障信息的正确性和完整性,并及时利用故障信息对产品进行分析、改进,以提高电子产品的可靠性[10]。

生产、检验环节采用纠正措施系统,可及时分析故障原因,从而确认问题源头。经过层层把控,失效样品数量断崖式减少。在之后的其他项目及批次中,该问题不再出现。

4 结论

本文通过建立供应商采购体系、规范采买渠道、严把器件质量关、监控各个测试过程、缩紧不合格的器件流通途径、建立故障纠正措施系统等多种方式,有效地解决了核级产品在制造过程中出现的元器件失效问题。