应用于时钟发生器的低杂散亚采样锁相环*

杜佳恒,赵宏亮,刘兴辉,程 帅,赵日新,赵 野

(1.辽宁大学 物理学院,辽宁 沈阳 110036;2.中国科学院 微电子研究所,北京 100029;3.中国科学院 硅器件技术重点实验室,北京 100029)

0 引 言

许多集成电路中都需要周期时钟信号。例如,用于时间—数字转换器中的细采样时钟、在无线收发器中对所需要的信号进行上转换和下转换等。时钟信号的精度影响整个系统的性能,因此,一个稳定的低杂散的时钟信号是必不可少,而时钟信号的产生离不开锁相环(phase-locked loop,PLL)。传统电荷泵PLL(charge-pump PLL,CPPLL)在带宽确定的情况下,参考杂散主要来自CP充放电电流的失配[1]。若选取较小的环路带宽,可以抑制控制电压的纹波,从而降低杂散,但这会增加锁定时间和环路滤波器电容面积。

本文提出的亚采样PLL(sub-sampling PLL,SSPLL)电路结构消除了传统CPPLL中鉴频鉴相器(phase frequency detector,PFD)延迟失配和CP电流失配所引起的杂散,并且因为锁定时核心环路中没有分频器的存在[2],带内噪声不会被放大N2倍(N为分频比)。

1 CPPLL杂散分析

传统CPPLL的参考杂散主要来源于CP的输出电流失配。图1为PFD和CP的原理。在工作过程中,PFD将分频(Div)后的相位与参考(Ref)频率的相位进行比较,生成UP和DN信号来控制CP的开关,将Ref和Div的相位误差转换为CP上电流源IUP和下电流源IDN之间的准时差τUP-τDN。理想情况下,当PLL锁定时,CP提供的净电荷应为零,即IUP=IDN,此时锁定点如图1中A点所示。

图1 PFD/CP原理

为了保持稳态锁定条件,必须满足下式

IUP·τUP=IDN·τDN

(1)

当IUP与IDN存在失配时,即IUP≠IDN,此时锁定点如图1中B点所示。因此,CP其中的一个电流源必须打开更长的时间才能满足式(1)的要求,这会导致CP的输出电流出现如图1所示的电流纹波,结果使PLL的输出产生较大的杂散。

2 低杂散SSPLL设计

本文提出的改进型SSPLL电路结构如图2所示。SSPLL采用双环路,包括核心环路(core loop)和锁频环路(frequency-locked loop,FLL)。其中,核心环路包括亚采样鉴相器(sub-sampling phase detector,SSPD)、亚采样电荷泵(sub-sampling charge pump,SSCP)、低通滤波器(low-pass-filter,LPF)、压控振荡器(voltage controlled oscillator,VCO);FLL相比CPPLL多个死区(dead zone,DZ)发生器模块。由于环路锁定时,只有核心环路工作,没有分频器的存在,SSPLL的带内噪声不会被放大N2倍。

图2 SSPLL结构

2.1 SSPLL杂散分析及优化

SSPLL杂散的主要来源是BFSK效应,即SSPD对VCO的周期性扰动。当SSPD中的开关闭合时,采样电容CSAM连接到VCO,成为VCO负载的一部分;当开关断开时,VCO没有负载CSAM。采样器在频率fref处的周期性开关以类似于二进制频移键控(binary frequency shift keying,BFSK)的方式调制VCO的输出频率。由于SSPD通过周期性的改变VCO电容负载干扰了VCO的工作,因此引起杂散。

为了抑制BFSK效应,增加了一个互补开关虚拟采样器(dummy sampler),如图2中所示。由于采样器和其虚拟采样器的互补切换,VCO总是连接到一个CSAM上,VCO的负载电容不随时间变化,BFSK效应得到补偿。此外,在VCO和SSPD之间添加一个隔离缓冲器,实现更好的隔离,进一步降低了杂散。

2.2 改进型SSPD/SSCP电路

SSPD/SSCP的增益很大导致图2中滤波器电容C1的面积很大。图3(a)给出了一种带有脉冲发生器(Pulser)的SSPD/SSCP,以降低C1的面积,从而有利于PLL的集成。SSPD采用传输门作为采样开关可以减轻时钟馈通和电荷共享的不利影响。

图3 SSPD/SSCP原理与SSCP电路

SSCP的电路如图3(b)所示,在SSCP中加入单位增益缓冲器,使得当输出端充放电开关关闭时电流源管的漏端电压和控制电压相同,有效减小了由电荷共享而引起的控制电压纹波,增强了 SSPLL的杂散性能。

2.3 PFD/可调窄死区发生器

环形振荡器具有较大的调谐增益,VCO控制电压小的变化就会导致VCO输出频率大的变化,从而增大锁定时间。因此,基于环形振荡器的SSPLL需要一个窄死区发生器,FLL应该一直工作到VCO的输出频率进一步接近锁定为止,这样就减少了SSPLL锁定建立过程中累积相位的时间。图4为可调窄死区发生器的原理。

图4 PFD/可调窄死区发生器原理

本文设计的可调窄死区发生器可以通过外部调节Vtune来控制死区时间。在Vtune=0.7 V的情况下,建立的死区时间±0.7 ns,仿真结果如图5所示。

图5 死区建立时间

2.4 电流饥饿型环形VCO

电容电感型VCO和环形VCO已经被广泛应用[3~5]。后者噪声性能不如前者,但由于SSPLL的低带内噪声特性,采用大环路带宽使环形振荡器所主导的带外噪声有效降低。本文设计了4级全差分延迟单元结构级联的电流饥饿型环形振荡器,通过线性电压转电流模块将控制电压转换成对VCO的控制电流Iref,实现对频率的调节。整体结构及延迟单元如图6所示。延迟单元额外设计3路调节电流3 bit_Iref,补偿频率衰减,减小误差。

图6 VCO结构图及延迟单元

本文设计的VCO控制电压在0.4~0.8 V之间变化时,输出频率随控制电压呈线性变化,VCO调谐增益约为621 MHz/V,如图7所示。

图7 VCO调谐增益

3 仿真分析

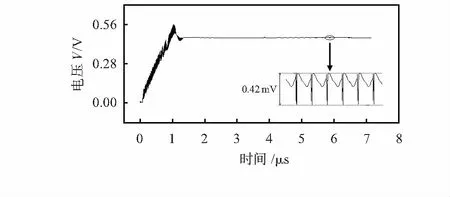

本文采用110 nm CMOS工艺设计,其中参考晶振频率为75 MHz,电源电压为1.2 V。版图绘制完成后,提取寄生参数进行后仿真,环路锁定行为建立过程如图8所示,SSPLL锁定时间小于4 μs;由于本文低纹波电路的设计,锁定后的VCO控制电压纹波得到有效降低,仅为0.42 mV。

图8 SSPLL环路瞬态响应及控制电压纹波

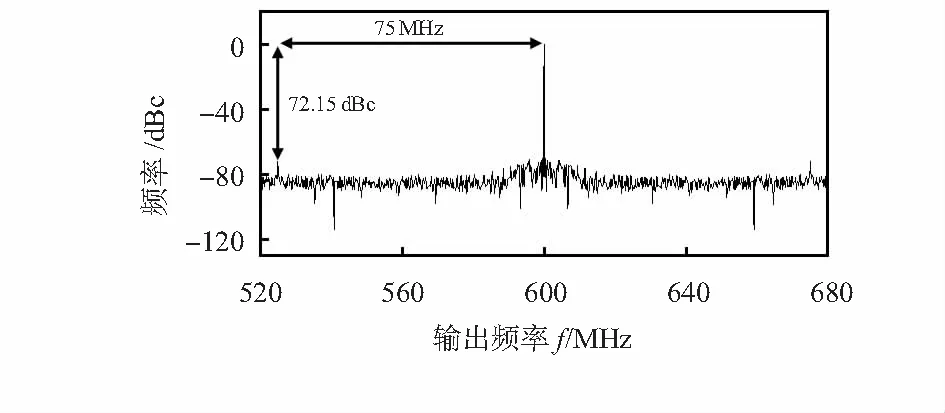

图9为SSPLL频谱,输出频率为600 MHz,偏离中心频率75 MHz处,参考杂散为-72.15 dBc。本文设计的SSPLL与文献[2,6~8]的PLL对比如表1所示,控制电压纹波以及参考杂散均得到一定程度的优化。

图9 SSPLL频谱

表1 PLL性能对比

时钟发生器通过注入锁定的原理,将SSPLL的输出信号注入到多个注入锁定振荡器(ILRO)中,使它们锁定到与SSPLL的输出相同的信号,从而产生稳定的多路时钟信号。时钟发生器为时间—数字转换器(TDC)提供稳定的时钟信号进行细采样,进而实现时间脉冲信号到数字电平信号的转换。整体版图如图10所示,其中,SSPLL面积约为1.2 mm×0.3 mm。

图10 基于SSPLL的时钟发生器及TDC整体版图

4 结 论

基于110 nm CMOS工艺,本文设计了应用于高精度时钟发生器中的SSPLL,分析了传统CPPLL和SSPLL的杂散机理,提出了实现低杂散和减小锁定时间的电路结构,以及同时降低芯片面积和带外噪声的方法。基于本文设计的SSPLL的时钟发生器,可以产生稳定的多路时钟信号。该SSPLL在1.2 V电压供电下,功耗为7.3 mW,锁定时间小于4 μs,输出电压纹波为0.42 mV,参考杂散为-72.15 dBc。