反射内存高速光电转换接口单元设计与实现

王廷凯,周 强,武 元

(北京航空航天大学 自动化科学与电气工程学院,北京 100191)

0 引言

随着仿真技术的迅速发展,仿真模型变的较为复杂,仿真规模也越来越大,目前单节点仿真测试系统已经无法满足实际仿真需求。采取多个节点协同仿真,建立分布式仿真系统是未来的发展方向。

对于分布式仿真测试系统,业内已有部分研究。国外,1978年美国空军上尉J.A.Thorpe在“Future Views:Aircrew Training 1980-2000”论文中首次提出分布式仿真的概念,但限于当时的技术条件,未能投入到工程领域中[1]。1983年,美国国防部提出SIMENT计划,将车辆、飞机等多种仿真器连接起来组成了仿真网络,首次成功应用了分布式仿真技术[2]。1989年,分布式仿真技术有了新的发展,不再仅支持同构网络,也兼容支持异构网络[3]。1996年美国国防部建模与综合办公室提出仿真综合框架(HLA),综合了DIS以及ALSP协议,支持多类型仿真应用[4-5]。

国内,国防科技大学建立的KD-DRT系统是基于反射内存连接实现多计算机节点仿真数据通信[6];中国航天科工二院建立了基于协同仿真技术、支持多产品多领域协同仿真的COSIM平台[7];华如公司建立的XSIM可扩展仿真平台是借助多台计算机共同完成多实验、多设计、多样本的仿真需求[8]。北京神州惠普科技公司研制的DWK借鉴了HLA仿真结构,采用实时数据分发服务(DDS),并对各个组件建模,从而建立起分布式仿真测试系统及其开发工具[9]。

目前,分布式仿真系统都是采取反射内存网络作为通信协议,反射内存网络又多是采用光纤作为传输介质[10]。反射内存网络直接靠硬件实现数据映射,延迟低且可预测。随着分布式仿真技术的蓬勃发展,仿真节点个数逐渐增加,各个仿真节点由于分散在不同区域[11],有时相距较远可达数十千米。这时网络的传输延时、数据处理延时增大,会严重影响仿真系统性能[12]。为解决各仿真节点远距离实时通信的问题,研制实现了用于长距离、高速率、低数据处理延时的高速光电转换接口单元。该接口单元可以作为一个节点加入到用户原有的反射内存网络中,主旨是用于解决远程多节点分布式仿真测试系统中仿真节点互连问题,以及实现多种电信号(数字IO、LVDS、RS422、ARINC429、模拟量)的接口通信功能。该系统可以满足如下功能需求:

1)可以实现电信号和光信号间的高速转换,可支持数字IO、 LVDS、RS422、ARINC429、模拟量接口电信号的交互传输;

2)有效传输距离达到10 km以上,信息在各仿真节点间的数据处理延时达到微秒级;

3)配备人机交互监控界面。

1 总体设计

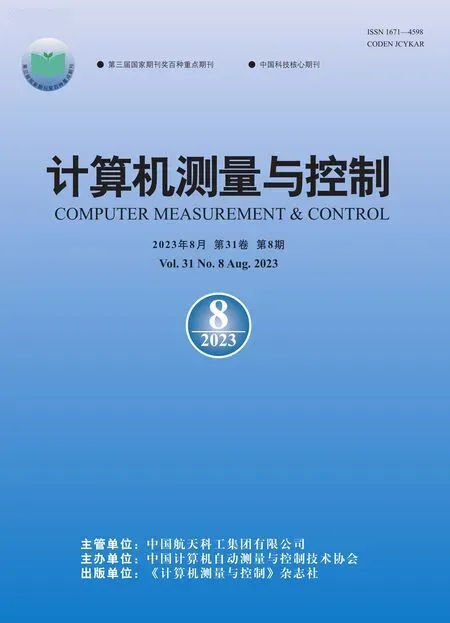

高速光电转换接口单元包括光纤转换器和多功能接口模块两个组成部分。单元的总体架构如图1所示。

图1 高速光电转换接口单元架构简图

光纤转换器用于接入原有多模光纤反射内存网络,将多模光纤信号转换为单模光纤信号,以便于实现长距离传输。实际方案实施中选用了商用的千兆单多模双纤转换器,具体型号为STC-9SMCMM-D-SC,其主要技术指标如下:

1)可在850 nm、1 310 nm多模光纤和1 310 nm、1 550 nm单模光纤之间进行转换;

2)支持全双工和半双工网络通信,带有自动协商能力;

3)支持各种长度数据包;

4)低功耗低发热可长时间稳定工作。

光纤转换器实现了多模反射内存网络和多功能接口模块的远距离通信。当光纤网络中某一节点有数据更新时,数据经过光纤转换器后将多模光纤信号转换为单模光纤信号并远距离传输给多功能接口模块。多功能接口模块接收到单模光纤数据后,一方面将光纤数据转发,另一方面根据地址信息截获数据进行处理。多功能接口模块接收到外部电信号时,将数据按照反射内存网络帧格式进行重组,通过单模光纤发送至光纤转换器,再由光纤转换器将数据同步到反射内存网络中。

2 多功能接口模块硬件设计

为满足强实时性远距离传输的目的,多功能接口模块具有如下技术特点:

1)采用单模光纤作为通信介质;

2)通信协议兼容反射内存网络;

3)采用母板配合子板的架构。

传统的总线协议转换装置一般将所有的通信接口集成到一块板卡上,并通过 FPGA或者DSP实现各通道协议之间的转换[13]。

但是对于分布式仿真测试系统,各个仿真节点具有的总线类型不完全相同,而且通道数量迥异,如果采用集成到一块板卡上的架构设计,会使得通信接口使用率低,造成浪费。

因此接口模块设计采用了母板配合子板的总体架构形式。其中,母板通过高速光纤与仿真网络完成数据交互,子板与母板采用GTX高速差分线连接通信,物理连接上采用可插拔的XMC接口。母板与多个子板协同工作,共同完成仿真任务,实现对不同接口信号的处理。

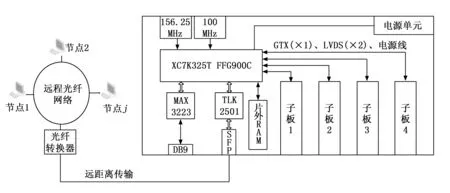

2.1 母板结构设计

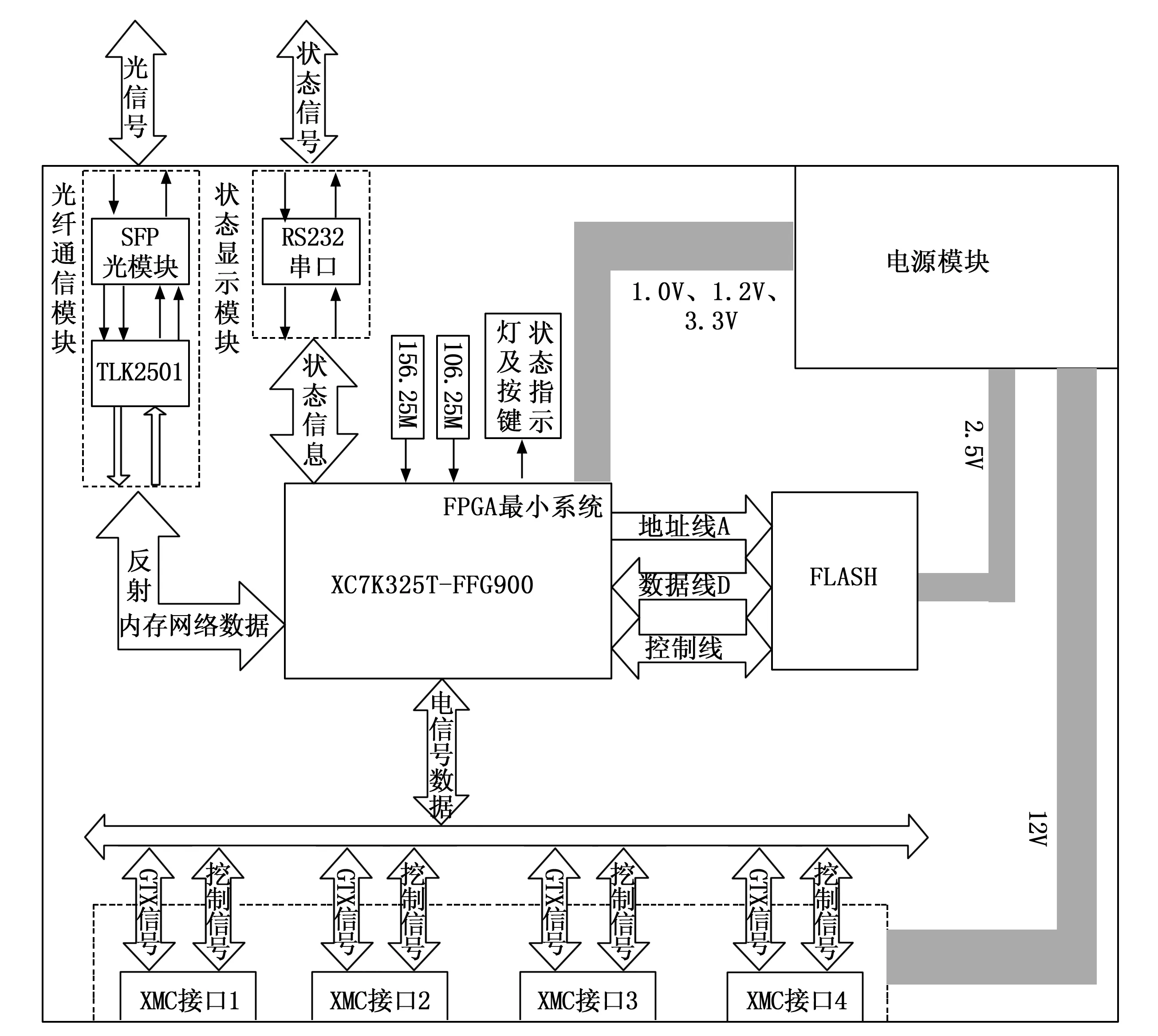

母板设计基于FPGA技术,用于实现与光纤网络的数据交互,并将指令及信息通过GTX高速串行数据线分发至各子板。母板在硬件结构上主要包括5个模块:FPGA最小系统模块、电源模块、光纤通信模块、板间通信模块和状态显示模块。其结构如图2所示,实物如图3所示,其中子板一、子板三在母板正面插载,子板二、子板四在母板背面插载。

图2 多功能接口模块母板结构示意图

图3 接口模块母板实物图

FPGA最小系统采用Xilinx公司 XC7K325T系列产品,具体型号为 XC7K325T FFG900。该芯片逻辑资源充足,内部RAM可达一万六千多KB,单端IO数量500个,差分IO数量120对,还有16对高速差分收发端口,可以满足设计需要。设计中采用的是Master BPI配置模式(即主BPI配置模式),通过配置M[2:0]为“010”,并且外挂一片 BPI Flash芯片实现,具体型号为PC28F00AP30TF,该型号芯片存储容量是1G bit,具有并行独立的16位数据线和26位地址线,可以通过并行加载的方式更快的向FPGA中写入固化程序。在这种配置模式下,可以兼容JTAG配置模式,实现FPGA的在线配置和调试。

电源模块采用12 V的开关电源供电,为满足板卡各芯片的供电需求,借助PTH08T230芯片搭建电压转换电路将12 V电压转换为1 V、1.8 V、2.5 V、3.3 V供FPGA内核以及IO输出使用;使用LT1963和LT1528芯片产生2.5 V、3.3 V给光纤模块及串并转换芯片TLK2501供电。

因为电路中包含多种类型电源,为避免各模块工作顺序混乱造成电路产生不确定状态,对于每种电压的上电时序要有精确的控制。为保证FPGA最小系统的可靠性和稳定性,要求FPGA的上电时序符合先上电内核电压,而后上电IO端口电压,并且要求内核电压在建立的过程中单调上升。在本设计中,采用的上电时序为:首先上电内核电压1 V,第二上电辅助电压及普通IO端口电压1.8 V,第三上电普通 IO 端口电压2.5 V 和3.3 V。设计过程中,通过采用上电延迟芯片TPS3808,将1 V作为1.8 V上电的使能信号,1.8 V作为2.5 V和3.3 V的上电使能信号,从而达到顺序上电的目的。

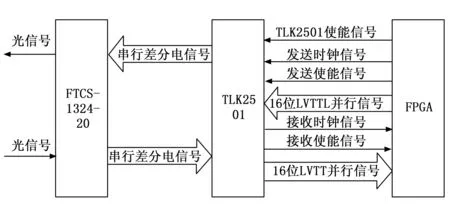

光纤通信模块由高速串并转换芯片 TLK2501和SFP光纤模块FTCS-1324-20组成,数据在光纤中以串行方式传输,经过转换芯片后变为并行信号传递给FPGA,结构图如图4所示。TLK2501是一款千兆位级收发器,可以支持1.5~2.5 Gbps的串并转换,芯片内部分为接收数据转换区和发送数据转换区两部分[14]。

图4 光纤模块框图

因为反射内存网中各个节点是采用GE研制的反射内存卡,GE卡的TLK2501芯片采用106.25 MHz时钟发送,为了保持通信的稳定可靠性,同样选择106.25 MHz时钟作为母板TLK2501芯片的发送参考时钟,此时TLK2501的数据传输速率位2.125 Gbps。

板间通信模块用来实现母板与子板的通信连接,包括一对GTX信号,一个复位信号,两个状态指示信号。GTX高速通信采用的是IBERT 7 Series GTX IP核,该IP核实现用户层数据与8B/10B编码方式的串行GTX数据的相互转换,在使用时仅需要配置参考时钟,通信速率等设置即可实现高速串行通信。配置IP核时,选择设置参考时钟为156.25 MHz,数据输入为32位并行输入,GTX的通信速率可以达到3.125 Gbps。在PCB设计过程中,GTX差分线走线完全遵循等长等间距的规则[15]。

状态显示模块是实现RS232串口与上位机的通信,使用MAX3223芯片实现串口差分信号与单端信号的转换。另外使用Python+pyqt设计了人机交互界面,实现对系统的监控,监控信息包括:各个功能子板的连接状态、反射内存接口的连接状态、各个接口的数据流量情况。

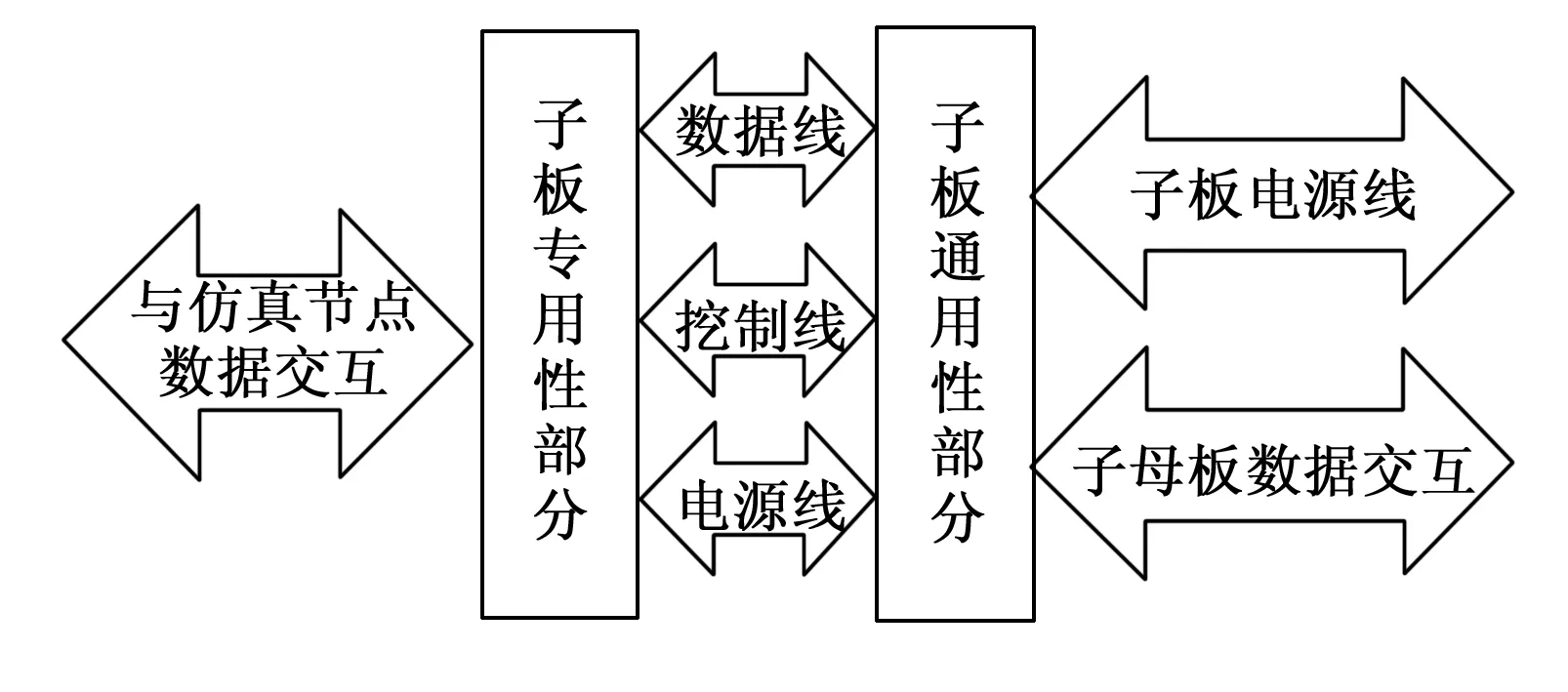

2.2 子板结构设计

功能需求上需要完成包括ARINC429、RS422、LVDS、数字IO四种通信总线以及AD数模转换功能。由于LVDS信号常伴随着TTL信号使用,用于判别LVDS信号所代表的信息段含义,因此在设计时,将 LVDS接口与IO接口设计在同一块子板上。

因此共设计出四块子板,分别实现上述4种功能。四张子板均是通过XMC接口与母板进行GTX通信,在设计过程中有较多通用部分,主要区别在于各个子板实现的接口类型不同。子板结构如图5所示,实物如图6所示,依次是LVDS与IO接口子板,ARINC429接口子板,RS422接口子板,AD采集子板。

图5 接口模块子板结构示意图

图6 接口模块子板实物图

2.2.1 子板通用部分设计

子板通用部分设计主要包括电源部分、FPGA芯片及其外围电路、子母板连接器设计,其中电源模块总电源采取12 V电压,其是通过XMC接口从母板取得,再通过LTM4644四降压型稳压器转换出1.2 V、2.5 V、3.3 V、5 V电压给FPGA及其余接口芯片供电。该芯片可支持同时输出四路不同电压,并且每路的最大电流值可达4 A,输出的供电精度误差在33 mV。

FPGA最小系统采用Xilinx公司的FPGA,具体型号是XC6SLX45T-2CSG324I,该型号有四对GTX专用引脚,普通IO引脚有100多个,足以满足通信需求。子板采用的配置电路与母板有所不同,使用的是 Master SPI 配置模式(即主SPI配置模式)。主 SPI 配置模式同样可以支持 JTAG 配置模式,与母板采用的主BPI配置模式相比,两种配置模式仅在程序存储芯片的选择上不相同,主SPI配置模式中FPGA和Flash 之间采用的是串行数据线连接,FPGA固化程序的加载速度相比BPI配置模式较慢。在设计中,子板的FPGA程序的复杂程度小于母板,不需要采用BPI配置模式提升FPGA 固化程序的加载速度,因此子板最小系统存储芯片选择的是128Mbit的SPI Flash芯片 N25Q128A13ESE40G。

在通信领域,板卡间通信速率主要取决于连接器的质量与性能[16]。采用XMC接插件,该类型接插件最高可达8 Gbps的通信速率,可以满足子母板高速通信需求。

2.2.2 子板专用部分设计

子板专用部分设计主要是FPGA与外部不同接口信号的通信设计。

LVDS信号为3.3 V的低压差分信号,其本质上是在差分线之间产生330 mA的微小电流,通过附加100欧姆的终端电阻实现 3.3 V的电压差。因此LVDS信号的收发需要分别采用专用的驱动器和接收器实现,而不能直接连接FPGA的引脚。开关量的输入输出都是符合TTL电平标准,而 FPGA 的引脚采用的是LVTTL电平标准,因此需要采用芯片实现TTL电平标准与LVTTL电平标准的转换,作为FPGA与外部开关量信号之间的数据交互的桥梁。因此LVDS与IO接口子板采用DSLV047、DSLV048 电平转换芯片,实现LVDS信号两路发送两路接收,采用74ACT244实现TTL数字IO信号的输入输出。

ARINC429属于广播方式单总线,节点之间的数据交互采用78 Ω、非平衡的屏蔽双绞线作为传输介质,双极性归零码作为数字量表示方式,可以连接一个发送者和最多20个接收者。ARINC429接口子板以 HOLT公司出产的ARNIC429总线底层通信控制芯片HI3585PQI为核心设计而成。芯片的组成部分有发送模块、接收模块和控制模块3个模块[17],主要功能是通过SPI总线实现对芯片控制寄存器的配置,状态寄存器的读取以及 ARNIC429 数据、Label值的读写。

RS422子板采用MAX3077芯片实现RS422差分信号与单端信号的转换。该芯片具有一个接收器和一个驱动器,能够实现 RS422 差分信号和单端信号之间的转换。而且MAX3077E的驱动器压摆率不受限制,可以支持高达16 Mbps的传输速率。

AD子卡用于实现模拟电压采集与输出的功能,采用AD9280、AD9708实现AD、DA数据的转换,两芯片均为8位精度。设计中选用AD9280芯片2 V 输入模式,即电压的采集范围是0~2 V。因为设计中对模拟量的采集范围要求是-10~+10 V,因此需要通过AD9280芯片搭配电压调理电路,以满足采集范围的要求[18]。为保证模拟量输入在电压调理电路前后的电压值不因为分压特性而下降,需要在设计时尽可能的增大输入阻抗和减小输出阻抗。因此在设计中利用运放高输入阻抗低输出阻抗的特性,采用运放构成电压调理电路,将-10~+10 V的电压采集范围映射到0~2 V 之间。

3 固件设计

3.1 母板固件程序设计

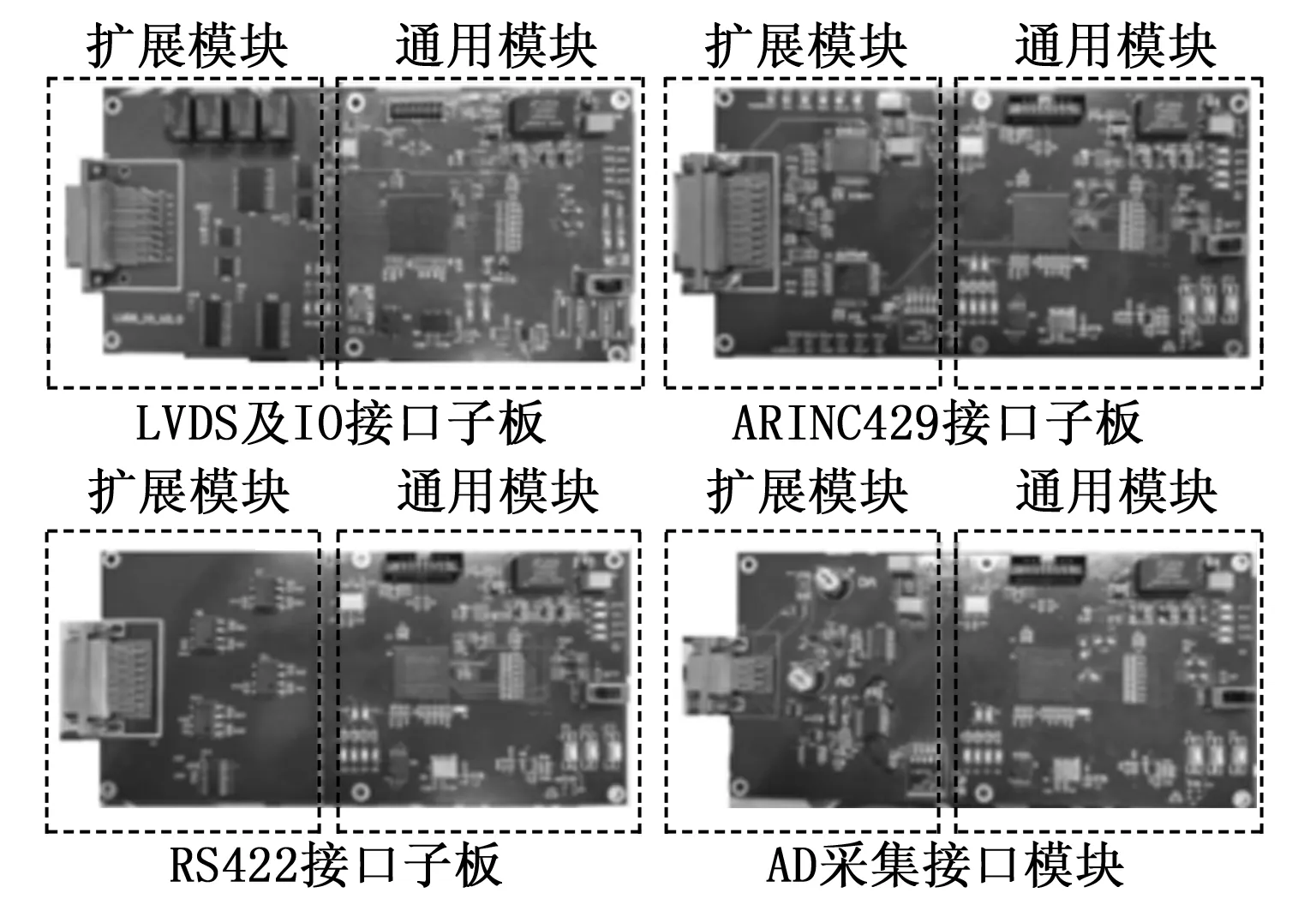

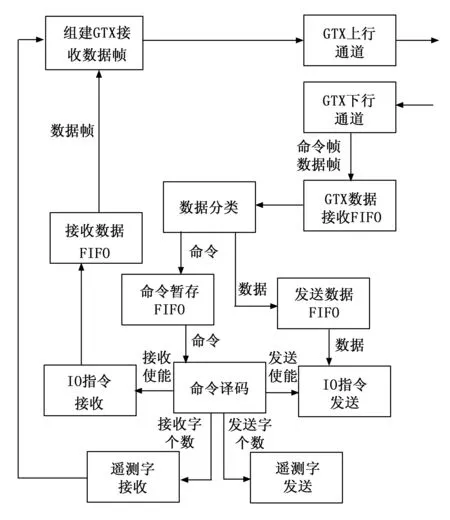

母板FPGA程序主要包括3个组成部分,第一部分负责与反射内存网络通信,包括解码反射内存帧,将FPGA本地需要上传的数据按照反射内存协议进行编码;第二部分负责处理FPGA本地帧消息,负责对子板数据的读写,包括判断当前本地帧归属的子板接口序号,循环扫描子板数据接口状态。第三部分负责处理GTX帧数据,包括对接收到4个子板的GTX帧数据进行处理,以及将发送给子板的FPGA本地帧转换为GTX帧,母板程序如图7所示。

图7 母板程序结构图

图8 自定义GTX帧格式

本设计在解码存储反射内存网络信息过程中是调用母板FPGA的RAM硬核资源作为节点的共享内存。因为FPGA的存储资源不足以支持存储反射内存网络中所有的数据信息,而且远距离智能IO接口系统作为一个节点加入到反射内存网络中后,读写的反射内存信息都存储在反射内存网络中的某一段地址中,因此FPGA只需要存储这一段的地址信息,并将更新其他地址的数据帧信息转发到下一个节点。

反射内存网络帧共包含128 bit,依次分别是地址位(32 bit双字)、类型判别(8 bit,用来判断帧类型:数据帧以及命令帧)、ID号(8 bit)、固定码1(16 bit)、数据位(32 bit双字)、固定码2(16 bit)、校验码(16 bit)。

FPGA对接收到的反射内存网络帧进行解码,根据地址信息定位对应的子板接口信号,4个子板接口对应的基地址分别为 0x0h、0x20000h、0x40000h 和 0x80000h,通过基地址判断出子板接口序号后,将偏移地址部分映射到8bit的子板寄存器地址。根据类型判别判断是命令帧还是数据帧。

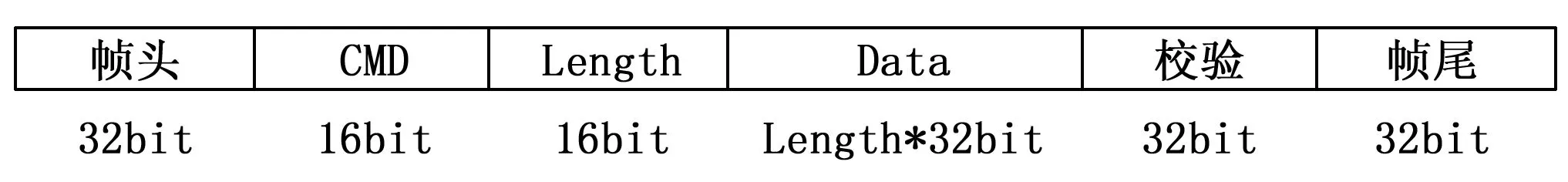

子母板间的通信采用自定义的帧格式,自定义的GTX帧格式如图9所示。为保证通信过程中传输数据不出现错位、丢数等问题,在设计GTX帧时在帧的首位分别添加帧头0xAAFF0055和帧尾0x55FF00AA,用以在判断当前GTX帧是否发送成功。CMD 表示一个命令字,母板或子板的FPGA固件程序会根据该位的数值执行相应的操作。Length表示帧数据的长度,若长度不符则丢弃该帧数据。Data表示帧数据,长度由帧数据长度Length决定,为Length*32 bit,用来承载需要传递的数据。

图9 LVDS子板程序框图

分析系统中涉及到的总线协议时,发现RS422以8 bit为发送数据的最小单位,但是GTX帧消息由于使用官方IP核的原因,需要以32 bit为发送数据的最小单位,所以可能会出现发送数据信息不满足32 bit,无法构成GTX 的一个数据位的情况。为解决这个问题,将不满足32 bit的数据信息通过高位补0的方式填充为32 bit,然后在CMD中控制32 bit数据的无效字节个数。母板向子板发送的下行CMD 命令中包含读写命令、数据有效位数和命令操作的寄存器地址三部分信息。

为确保每一个指令和数据都正确的从母板传输到子板,每当母板向子板发送一个GTX帧后,都需要子板向母板返回一个 GTX返回帧表示GTX帧是否发送成功。子板向母板发送的GTX返回帧中,CMD命令操作状态和寄存器地址两部分信息。当下行命令发送正确或错误时,GTX返回帧中的 CMD命令字[15:8]bit为0或1;当下行命令请求访问子板某个寄存器地址的值时,GTX返回帧返回该数据值,CMD命令字[15:8]bit为2。

3.2 子板固件程序设计

子板程序设计主要内容包括接收母板发送过来的GTX数据帧,通过FPGA解码重组转发给接口芯片;FPGA接收到接口芯片上传的数据并将其转换为GTX帧发送给母板。

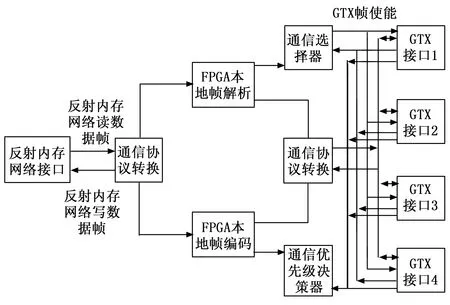

3.2.1 LVDS子板程序设计

LVDS接口子板的FPGA程序主要包括四部分功能,分别是GTX帧收发、数据分类、LVDS遥测字收发和IO通道指令收发。其程序如图9所示。

在接收到GTX帧消息后,根据帧消息中的寄存器地址判断是命令信息还是数据信息,命令信息主要包括LVDS遥测字的收发使能,收发遥测字个数,IO指令的收发使能以及收发数据的清零,每一条命令信息都对应一个特定的寄存器地址。LVDS遥测信号在接收过程中,是以帧的形式接收的,并伴随着采样时钟,每一个遥测帧由多个遥测字组成。每一个LVDS遥测字都包含26 bit的信息,从低位到高位依次是起始位0、8位地址信息、16位数据信息和1位奇偶校验位。

LVDS遥测信号输入存在因干扰导致数据丢失,影响遥测字接收数量的可能。因此在设计遥测信息接收模块时,利用FPGA并行处理的特性,设计了用于识别遥测字丢失的功能。每一个遥测帧之间的时间间隔最少为4 ms,遥测帧中每一个遥测字的时间间隔最多为10个遥测时钟周期(遥测时钟为 13 MHz),大约为1 μs。通过这个判断条件,设置计数模块,每当接收完成一个遥测字后开始以125 MHz的系统时钟重新计数,若计数值超过500(即4 μs)还未收到下一个遥测字,则表示接收过程中丢失遥测字。

3.2.2 ARINC子板程序设计

ARINC429 接口子板的FPGA程序主要包括三部分,GTX帧收发、数据分类和 ARINC429总线数据收发。基本功能与LVDS子板类似。不同之处是需要将GTX 帧发送的寄存器地址和数据译码为满足协议芯片HI3585配置和读写规则的数据。总控芯片FPGA与HI3585通过SPI总线通信,SPI通信协议包括CS、SCLK、MOSI、MISO四个信号。FPGA则负责GTX帧与SPI通信格式的互相转换。

ARINC429接口子板中采用的系统时钟为125 MHz的高频时钟,当FPGA中组合电路过于复杂时更易发生亚稳态的现象。因此控制模块在FPGA中对状态机编码时,采用了独热码的编码技术,即任一个状态编码中只有一位二进制数为1,其余各位都为0,如1_0000_0000。上述编码经过FPGA编译后得到的集成电路中,N个D触发器就可以实现N个状态的状态机,可以降低状态机在状态转换时出现亚稳态的概率。

3.2.3 RS422子板程序设计

RS422接口子板程序同样包括以上3个部分。RS422接口数据由11 bit组成,包括1位起始位,8位数据位,1位停止位,1位校验位。在接收RS422数据时,为防止干扰毛刺的影响,采取三次采样取众数的方法。根据系统时钟125 MHz计算出RS422信息中每一位串行数据需要占用的时钟周期个数n,例如1 MHz的波特率需要占用125个系统时钟。在采样时钟周期中选取n/2+1、n/2和n/2-1这3个时刻进行三次采样,进而提高了系统采样的可靠性。

3.2.4 AD采集子板设计

AD采集接口子板程序中包含GTX帧收发、数据分类和AD采集滤波3个部分。其中程序的关键部分在于AD采集滤波模块。常用的滤波算法包括中位值滤波法和算数平均滤波法。中位值滤波法是通过连续采集15个数据,并将15个数据排序得到中间值,此中间值即为采样结果[19]。但是这种方法需要对包含8 bit信息的15个数据排序,会采用大量的比较器,占用FPGA过多的资源。算数平均滤波法,通过连续采集16个数据,并计算出16个数据的平均值即为采样结果。这种方法在计算平均值时借用了二进制除法的思想,通过将16个数据的和右移四位实现除以16的运算,适用于FPGA的运算逻辑。但是当这16个数据中出现一个过冲击数据时,虽然经过算数平均,但是依然会对结果造成影响。

滤波方法采用防脉冲干扰平均滤波法,该方法综合了上述两种方法的优点,通过连续采集18个数据,判别并去除其中的最大值和最小值,并将剩余的16个采集数据进行平均,得到的算数平均值即为最终的采样结果。这种方法一方面避免了偶然发生的脉冲性干扰的影响,另一方面滤除了随机性的干扰信号。这样既避免了偶然发生的脉冲性干扰的影响,又滤除了随机性的干扰信号。

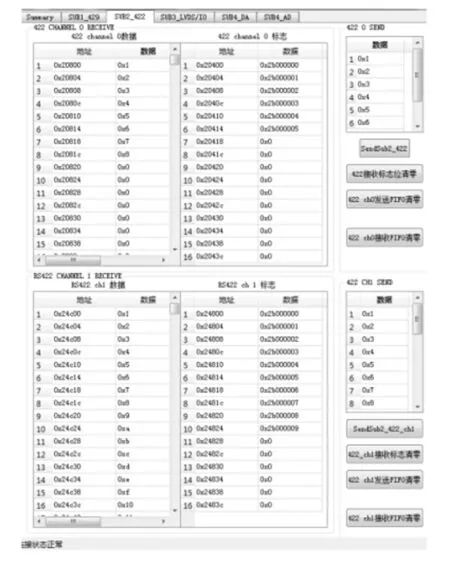

4 上位机软件设计

上位机软件配合串口实现对系统状态及数据的监控显示。界面采用python编写,实现母板与上位机的232串口通信,实时显示光纤以及各个子板的连接状态,各个子板收发数据显示。进入软件后首先查询光纤及各个子板连接状态,当连接正常后,启动系统。这里选取RS422子板为例,其人机交互监控界面如图10所示。

图10 RS422子板测试

5 性能测试分析

智能IO系统是为了解决分布式仿真测试中数据通信的问题,最重要的是实现系统数据通信的低延时。

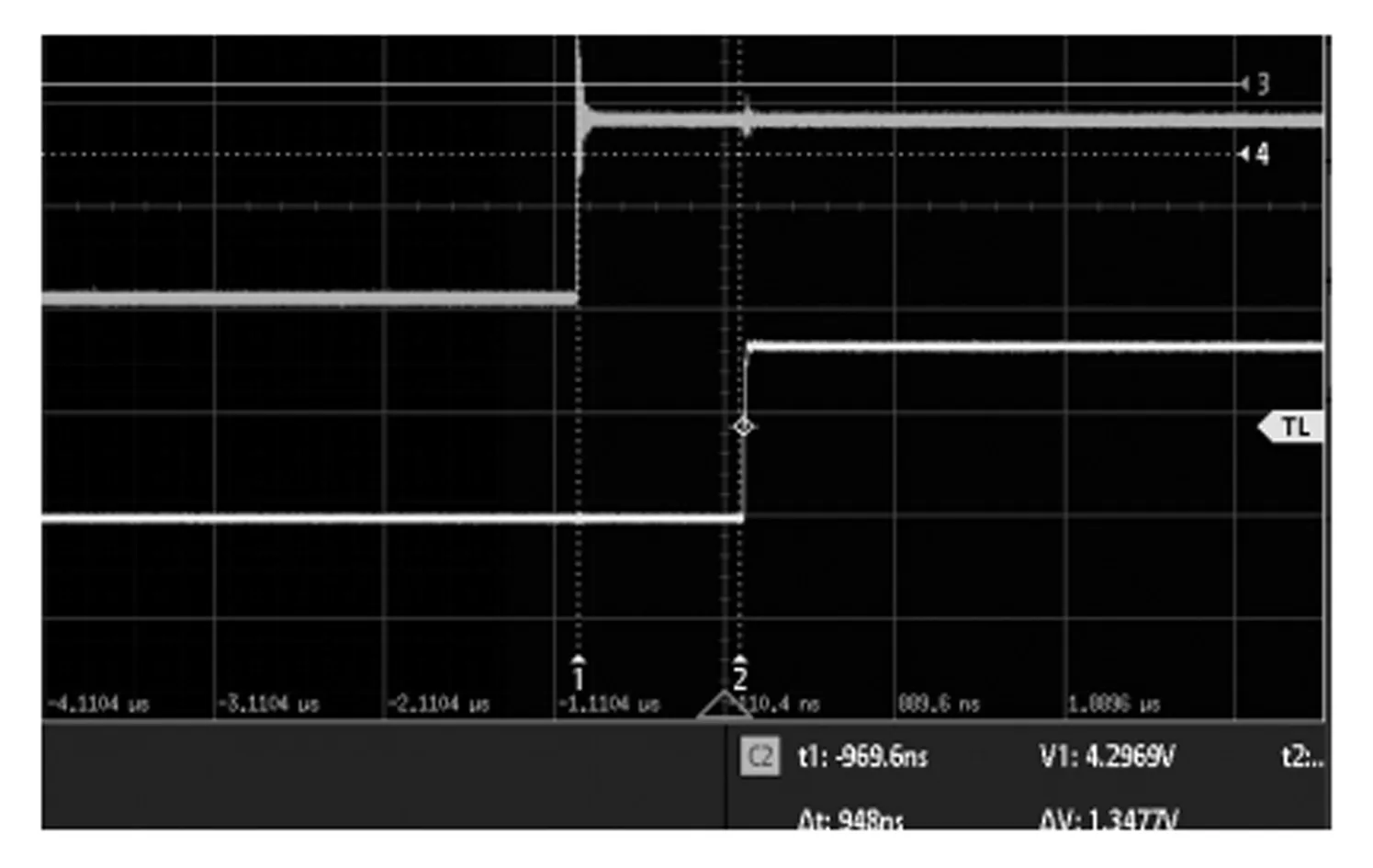

整个系统的延时时间包括光纤的传输延时以及数据处理延时。传输延时是由节点间距离决定,每千米距离传输延时大约为5[20]。处理延时是光信号与对应接口电信号的转换延时。现对该系统处理延时性能进行评估,测试选取422子板测量,其他子板测量方法相同。测量方法是将母板开始接收反射内存卡的光纤数据这一时刻记为T0,母板接收到光纤数据后,对反射内存数据进行译码并组建成GTX帧,再通过GTX发送给422子板,子板收到GTX帧后经过译码、数据缓存后发送到422通道,将准备发送第一个422字节的时刻记为T1,数据处理延时。

处理延时的测量有两种方法,方法一是示波器测量,方法二是使用FPGA计数测量。示波器测量的方法是选取FPGA的A、B两个IO输出端口,在T0时刻A端口电压置高,T1时刻B端口置高,通过示波器测量A、B两个端口置高的时间间隔即为处理延时,如图11所示。FPGA计数测量方法采用125 MHz时钟作为基频,在T0时刻从0开始计数,T1时刻停止计数,每一个数实际代表8 ns时间,最后的计数值乘8则为处理延时。示波器测量方法易有测量误差,并且多次测量时较为费时费力,采用FPGA计数测量,可以将每一次的计数值存入ROM中随时查看,可以较快完成多次测量。本次测量方法选择的是FPGA计数测量。

图11 示波器测量图

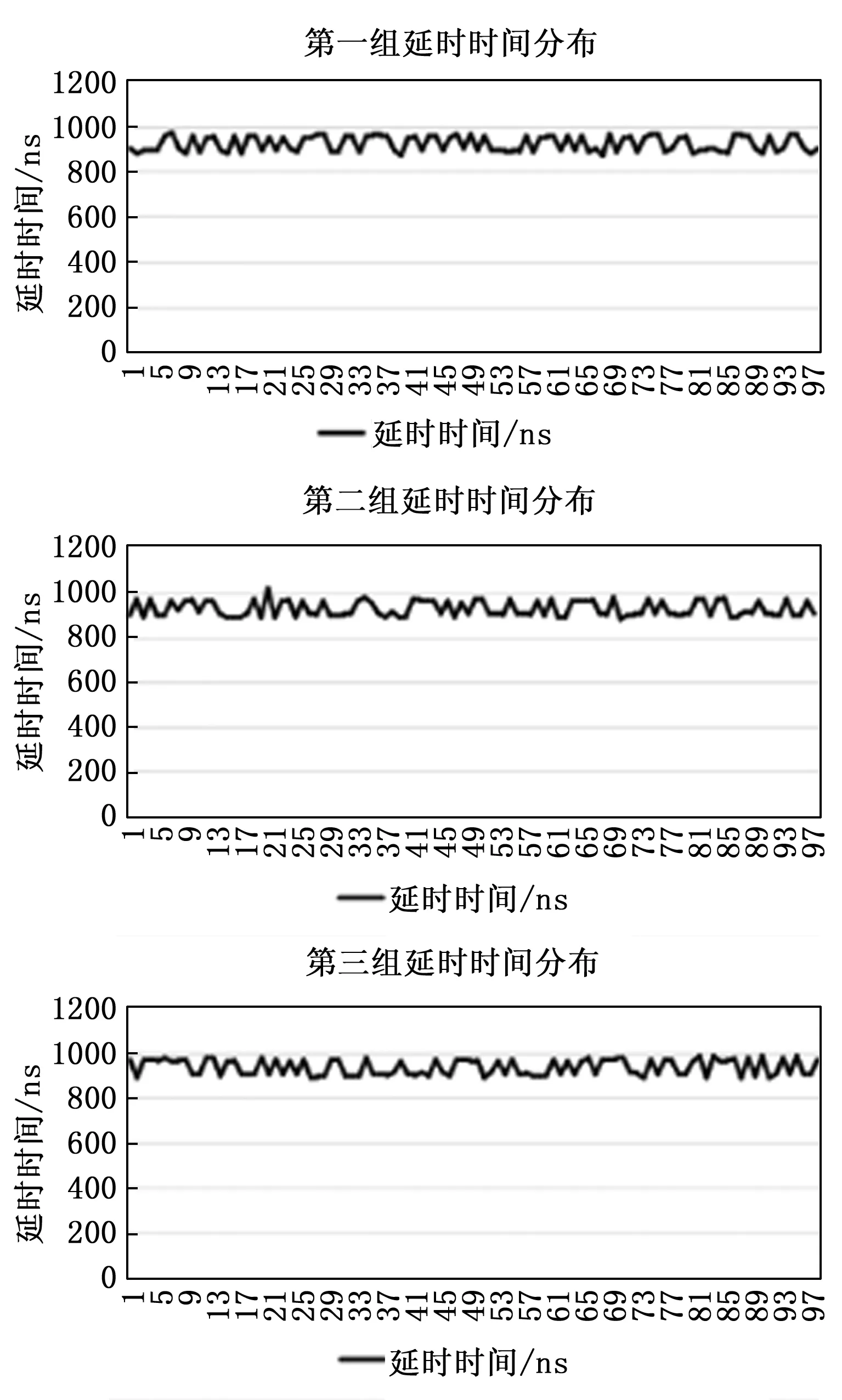

随机测试三组延时数据,每组测试100次,结果如图12所示。延迟时间稳定于800~1 000 ns内,远低于光纤数据的每千米延时时间,可以满足使用需求。

图12 延时数据分布图

6 结束语

本文设计了一种面向反射内存网络远程通信的高速光电转换接口单元,其中的多功能接口模块采用了与多种专用子板组合的模块化、可扩展硬件架构形式,实现了数字IO、LVDS、RS422、ARINC429、模拟量等多种硬件接口功能。

通过实验测试,该单元有较低的数据处理延时,并且可处理多种电信号类型,实现了多种电信号接口的集成,对于远距离分布式仿真系统中各节点数据处理交互的实时性有显著提高。同时设计了人机交互监控界面,可以实现对系统状态以及节点处理数据的观察。