一种侦干探多功能一体化微系统设计

肖国尧, 廖桂生, 柯华锋, 李 帅, 全英汇

(1. 西安电子科技大学电子工程学院, 陕西 西安 710071; 2. 西安电子科技大学雷达信号处理全国 重点实验室, 陕西 西安 710071; 3. 中国空间技术研究院通信与导航卫星总体部, 北京 100094)

0 引 言

随着雷达、电子战等电子信息系统新技术和新体制的发展,以及先进封装技术的出现,将侦察、干扰、探测、通信等功能一体化[1-3],是未来电子频谱作战的必然手段。为了满足系统中所有功能组件的可任意调配、性能参数可被编程,实时动态调配装备平台上的各种资源,使得作战资源的配置更加优化,提升交战的有效性、战术应用的活性以及系统整体性能的鲁棒性,从而符合该要求的柔性构造在信息化装备平台中被提出[4]。柔性构造是实现侦干探一体化的最优途径,能提升信息化装备对于复杂战场环境的适应能力。

近年来,许多研究机构、高校和公司都围绕着一体化的概念提出了不同的设计方案,文献[5]提出了一种基于随机脉冲重复间隔(pulse repetition interval, PRI)捷变的雷达通信一体化共享设计方法,意在波形设计上融合多种功能来减少电子设备的体积和提高频谱利用率。文献[6]研制了高密度的相控阵T/R组件,减小相控阵面厚度和减轻阵面的重量,有效降低了星载或者弹载系统的载荷体积和重量。文献[7]基于微组装混合集成技术设计了一种具备雷达/侦察/干扰一体化收发前端,提高了作战威力。文献[8]介绍了一种数字信道化技术的侦察干扰一体化处理单元,实现对宽带信号的收发,完成对雷达信号的数字移频干扰。

对于无人机载、弹载综合电子系统领域,多功能信号处理平台的灵活性、便携性、实时性以及小型化等特点尤为重要,也是未来主要发展的重要技术方向[9]。随着雷达信号带宽、接收通道数量、工作模式种类等不断增长,对其的实时处理能力、运算密集度、高速数据传输等性能提出了更高的要求,面临体积、重量、功耗、通道等多方面的严峻挑战。而现阶段信号处理系统仍为分立器件搭建,常见如3U、6U标准VITA第2代传输接口(VIAA P2 express, VPX)模块与机箱,系统集成度低、体积庞大且互联复杂、冗余,对应于信息化装备中的侦察、干扰、探测等信号处理系统与装备平台的功能是一一对应的。各功能系统相互之间独立性强,软、硬件资源利用率较低,难以实现侦察、干扰、探测等多功能综合处理,无法满足未来复杂电磁频谱环境的应用需求。

为了能很好地解决信号处理系统上述存在的问题以及侦干探一体化柔性构造技术的问题,“微系统”是一个非常好的技术突破点[10-12]。微系统技术融合了微电子、微机电和微光电技术,采用统一的硬件系统架构、共享/复用计算单元以及标准化软件知识产权(intellectual property,IP)的思路,通过将处理器、控制器、转换器以及各种接口等进行集成设计,构成一体化软、硬件多功能集成系统,并采用微纳制造及微集成工艺实现系统结构的微型化,具有高集成度、微小型化、低功耗、高可靠性、高效率等优点。微系统技术上的新材料、新方法、新工艺等技术变革必将对系统研发和制造带来颠覆性影响,微系统具备从信息获取到分析决策,再到指令执行等完整电子信息系统功能,是实现单一或多种用途电子信息系统的综合性前沿性技术,也是一种能更好地解决多功能一体化与柔性化构造的关键技术[13]。

针对侦干探多功能一体化技术发展需求,本文着重研究与分析了侦干探一体化集成的可行性,开展全新架构的侦干探多功能一体化微系统设计研究,并提出了一种侦干探多功能集成微系统设计新方法,采用异质异构混合系统集成思想,将侦干探多种功能的信号处理单元核心部组件。如数模转换器(digital to analog converter, DAC)/模数转换器(analog to digital converter, ADC)、高性能处理器、大容量存储器等不同功能、不同工艺、不同材料芯片,通过系统级封装(system in package, SiP)、三维堆叠、多芯片封装等集成技术手段,进行微型化集成设计,形成信号处理SiP硬件模块。同时,基于该SiP模块平台,开展侦干探一体化综合处理软件设计、实现与验证。最后,形成侦干探一体化的多功能集成微系统。

该微系统可为侦干探多功能信息化系统应用提供灵活、便捷以及软件化、标准化、模块化的信号处理系统平台,且大幅缩短了系统的研发、验证和迭代周期,大大缩减了信号处理系统的体积和重量。同时,采用异质异构混合系统集成思想,将金丝引线键合(wire bonding, WB)、集成无源元器件(integrated passive device, IPD)、重新布线层(re-distribution layer, RDL)以及三维堆叠技术等多种封装工艺技术进行集成、混合应用,共同实现复杂系统的可靠集成。该微系统设计技术在架构、性能、工艺实施等方面具有较大优势和应用前景。

1 微系统整体架构设计

在传统的侦察接收机中,基于低通采样结构的数字接收机[14-15]接收较高频段的信号时,存在不满足奈奎斯特采样定理的缺点,无法对信号进行有效恢复。基于带通采样结构的数字接收机[14-15]由于需要使用可调谐带通滤波器实现对整频带进行时分侦收,在某一时刻支持特定的频带进行处理,导致灵活性和实时性都无法满足高精度和高性能的要求。基于中频带通采样结构的数字接收机[16]由于前端的模拟部分较多,结构设计最为复杂,不适合在小型化中使用。而信道化接收机[17-22]不仅能满足对高频段信号接收的需求和结构实现简单的优点,还因具有高灵敏度、大动态范围、同步信号检测以及全概率接收信号等理想的特点被广泛的应用于各个领域。

在现有的干扰系统中,由于受到体积、功率等因素的限制,无法实现对宽带雷达信号的高速采样和对天线收发的高度隔离,而采用的传统转发干扰方法[23-25]需要将全部时长的雷达信号接收后,才进行调制转发。该种方法所形成的假目标远远落后于真实目标,容易处在距离波门之外,无法形成有效的干扰。对于间歇采样转发干扰,由于其独特的“欠采样”和收发分时特性,对雷达信号进行间歇性采样,不仅大大降低了信号处理的高速采样要求,还能解决天线收发的隔离问题,对装备在小型化设备上提供了可能。并且切片转发的时宽带宽小,易于进行调制和多种模式的组合等工程实现,极大地丰富了干扰的样式。同时,间歇采样转发干扰作为一种针对脉冲压缩雷达的干扰样式,其本质与雷达信号具有部分相干特性,从而可以产生与目标信号相似的相干假目标串,达到影响雷达对目标的正常检测效果。有研究表明,间歇采样转发干扰对发射信号为线性调频信号、相位编码信号、V-调频信号的脉冲多普勒(pluse Doppler, PD)雷达、合成孔径雷达(synthetic aperture radar, SAR)、逆SAR(inverse SAR, ISAR)体制和多输入输出(multiple input multiple output, MIMO)雷达均能达成有效的干扰[26-27]。

对于探测功能系统,MIMO雷达通过发射正交波形获得波形分集增益,对比技术已经成熟并应用较广的相控阵雷达,在参数估计能力等方面具有较大提升[28-29]。而MIMO雷达对于信号处理系统的需求是具备同时多发多收处理功能,所以在小型化上实现MIMO雷达的信号处理,微系统是一个很好的实现方向。

本节先对信道化侦察、间歇采样转发干扰、主动MIMO雷达探测功能的信号处理算法与实现进行分析,再提取侦干探多功能的公共计算单元/因子,并结合重构/复用的软件设计与先进封装技术,提出了一种侦察、干扰、探测多功能信号处理一体化软件设计与小型化集成设计新技术,形成具有侦干探多功能软、硬件信号处理能力的微系统。该微系统具有一定的适用性,且在资源受限(体积、性能、功耗)应用场景中,有着巨大技术优势与应用前景。

1.1 一体化软件架构设计

1.1.1 侦察功能信号处理分析

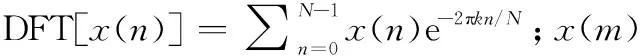

在侦察信号处理过程中,传统的接收机射频(radio frequency, RF)前端复杂,不利于系统的小型化应用,随着RF直采技术、大带宽高采样率模数转换器件的发展,RF数字化已是大势所趋。本文采用多相滤波器结构[30-33]的大带宽信道化技术实现侦察功能的数字接收机。如图1所示,采用大带宽ADC将一定频带内的RF信号全数字化,得到x1(n),再经数字下变频和多倍抽取器得到零中频和降采样处理后的宽带信号x2(n),采用多相滤波器将宽带信号x2(n)划分为N个均匀信道以及进行N点并行快速傅里叶变换(fast Fourier transform, FFT)处理,最后得到单个信道的基带信号,该信号模型可表示为

Ymi(k)=DFT[x(m)(-1)ρejπρ/K]|m=mi

(1)

图1 信道化信号处理流程Fig.1 Channelized signal processing flow

多相滤波器组可使得滤波运算和信号处理速率大大地降低,同时仍能满足灵活性、实时性和高性能需求。该结构采用数字化处理方式,减少RF链路,使得接收机系统更简单,便于小型化、标准化。

1.1.2 干扰功能信号处理分析

间歇采样转发干扰,由于其独特的“欠采样”和收发分时特性,对雷达信号进行间歇性采样,不仅大大降低了信号处理高速采样的要求,还能解决天线收发的隔离问题,对装备在小型化设备运用上提供了可能。并且切片转发的时宽带宽小,易于进行调制和多种模式的组合等工程实现,极大地丰富了干扰的样式。本文重点关注间隙采样直接转发干扰、间歇采样重复转发干扰以及间歇采样随机相位调制重复转发干扰3种干扰模式,并建立信号模型[26,34-37]如下:

(2)

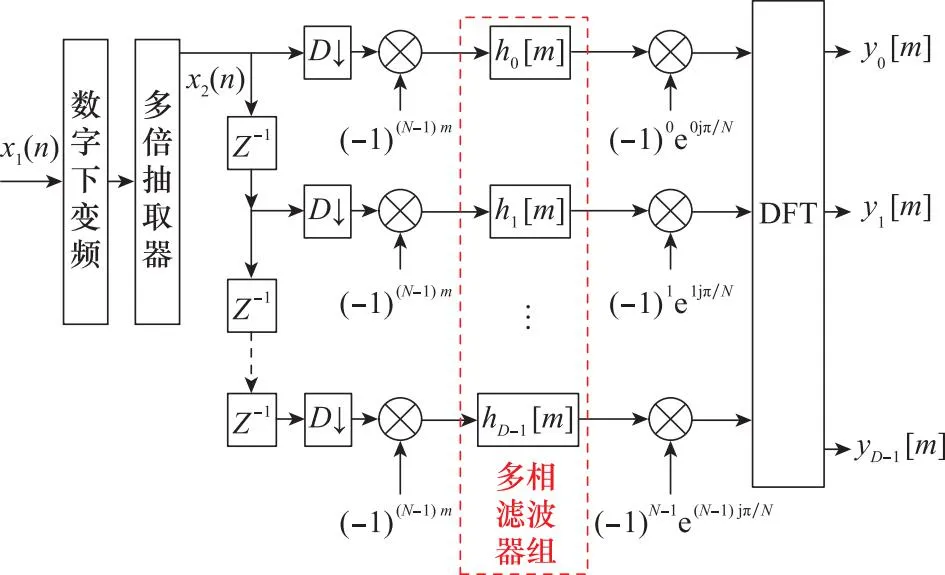

式中:T表示采样时长;Ts表示采样周期,且Ts=MT,M为当前脉冲串转发次数;ε(t)为一个码元持续时间;φ(n)为随机相位码元序列。从该模型可得出,当M转次数为1时,对应的干扰模式为直接转发干扰,当码元随机序列φ(n)皆为同相时,干扰模式就从随机相位调制重复转发干扰变为重复转发干扰。则可认为前两种干扰模式为随机相位调制重复转发干扰特殊情况,通过该信号模型,可得出干扰功能的完整信号处理流程如图2所示,通过配置相关模式切换输出路径、控制转发次数,部署对应的干扰策略,使得功能模块的实现更加简便。

图2 侦干探一体化综合处理软件架构设计Fig.2 Integrated processing processing software architecture design for reconnaissance jamming and detection

1.1.3 探测功能信号处理分析

探测功能与传统的MIMO雷达信号处理方式类似,接收上位机下发引导信息,装订波束指向与采样波门起始位置,采集N路天线前端输出的MIMO回波数据,将回波数据下变频到基带后,对基带回波信号经过多倍抽取器获取需要的处理采样点数。根据波束指向对抽取后的回波数据做接收数字波束形成,将N路回波数据合成一路,这一路数据中会携带N个正交分量。通过组匹配滤波器将接收波束形成后的数据中的正交分量分离出来,得到N路脉冲压缩结果。将N路脉冲压缩结果再进行一次等效发射波束形成,等效发射波束形成权系数为接收波束形成权系数的共轭,得到最终的合成数据。在同一方向连续接收M次回波数据,得到一个相干处理间隔(coherent processing interval, CPI)的等效发射波束形成结果,在做动目标检测(moving targets detection, MTD)、恒虚警率(constant false alarm rate, CFAR)检测与目标凝聚等目标检测,获取目标的距离与多普勒信息[38-42]。使用单脉冲比幅测角方法得到方位和俯仰的鉴角曲线,通过比对获取目标的空间角度信息。最后,将目标的距离、多普勒与角度信息上报给上位机[43-44],探测信道处理流程如图2所示。

1.1.4 多功能一体化软件架构

为了将上述3种信号处理功能融入到同一种系统框架,使得具备自主多任务规划、软硬件协同、认知外部环境并动态配置电路功能,满足在极高时序约束、更小体积空间、更多功能等特点的条件下实际使用需求。本节将按照不同功能类型进行信道划分,再提取信道间的共同计算单元,结合重构/复用的软件设计思路,可设计出适合微系统的侦干探一体化综合处理软件架构,如图2所示。

在红色虚框中,根据运算实时性和消耗资源的需求,将上述实框中功能模块单元规划到DAC/ADC、现场可编程门阵列(field programmable gate array, FPGA)和ARM(advanced RISC machine)处理器这3个硬件单元中。然后进行统一调度,分别发挥不同软件功能,以便能高效地利用系统有限的接口、逻辑和运算资源。在可编程逻辑单元中,可以设置时序模块产生侦察、干扰和探测的收发逻辑控制,完成对数据解包模块和数据打包模块的数据传输职能,以及对间歇采样周期、采样时长和采样数据完成编号的流水线控制。数字下变频、抽取和数字上变频和插值4个共用IP模块,可以根据各个信道的不同参数进行调用,完成收发的时段的频谱搬移和处理速率匹配.有限脉冲响应(finite impulse response, FIR)滤波器组可以设置成低通、高通、或者是多相滤波器模式,根据各自信道的需求完成调用。N点FFT蝶形运算可实现对数据从时域变到频域的处理,最大可支持64点并行运算。波束形成算法IP、脉冲压缩IP、相位调制模块、序列编号模块和存储区调用模块都是作为专用模块完成相应功能的数据处理。在多核处理器中,通过数据交换网络可完成接收可编程逻辑端打包传输过来的数据,也可以将上位机下发的数据包发送到相应的功能信道。DAC/ADC控制单元可以实时地调度多路转换器进行收发处理,同时检测各路转换器的工作状态。以太网收发控制单元可以完成与上位机进行通讯和数据传输,通过上位机参与到软件的参数设置和功能模块调度。多核交互单元和存储数据调用模块可以完成多核之间的数据互传,实现多核并行处理控制和数据共享。MTD运算单元、CFAR检测率运算单元、单脉冲测角运算单元、目标凝聚运算单元、门限判决运算等模块作为对应信道的专用信号处理模块调用。

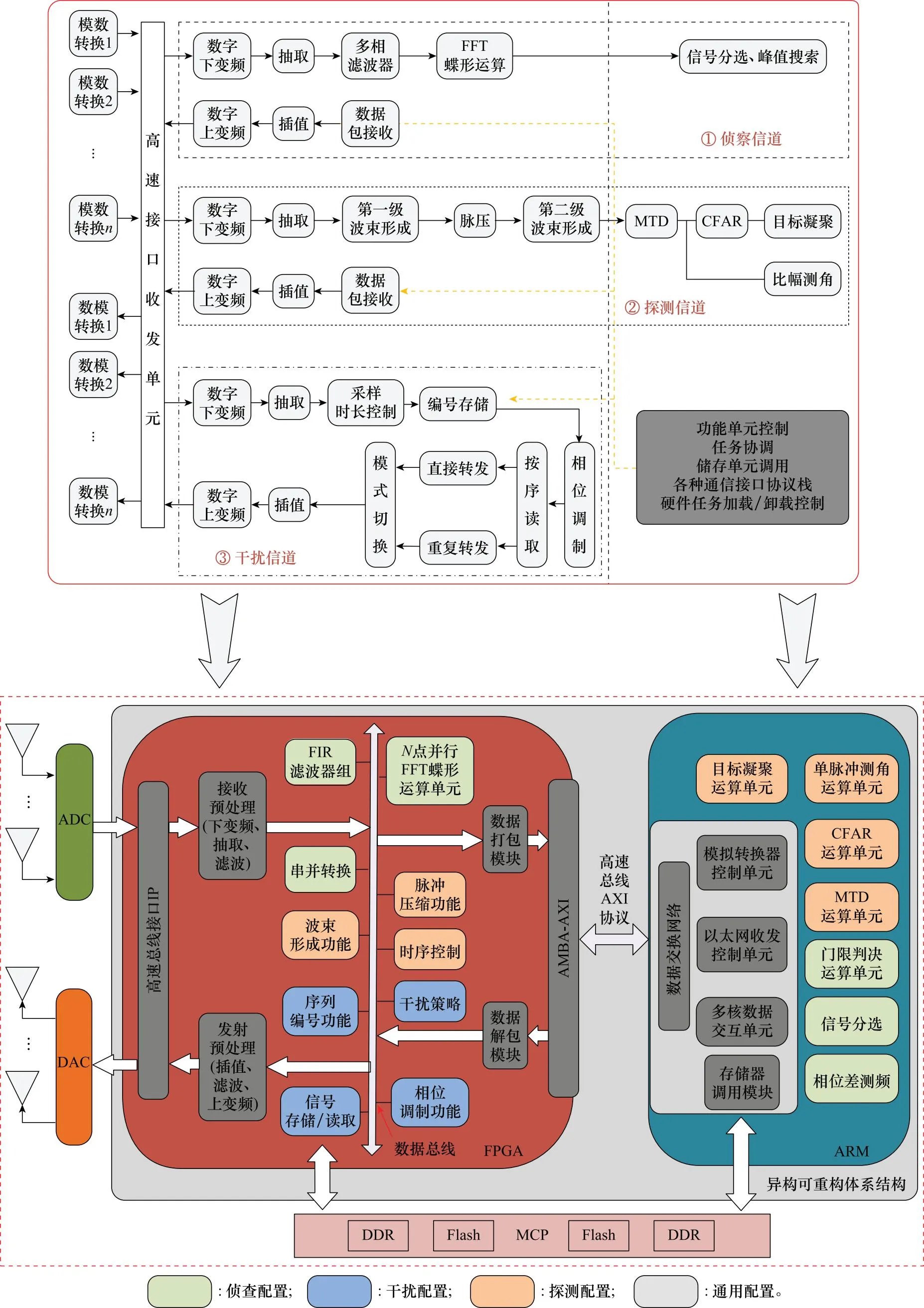

1.2 多功能集成设计

根据侦察、干扰、探测一体化综合处理软件架构设计中软硬件资源的需求,结合高中频、RF直采能力的信号处理技术以及多核处理器与可编程逻辑资源融合的异构可重构计算体系结构,探索了侦干探多功能一体化集成的可行性与新型架构技术。本节提出了一种可实现侦干探多功能信号处理能力的微系统硬件结构,如图3所示。通过先进系统级封装技术手段,将信号处理系统核心单元部组件,如DAC/ADC、ARM、FPGA、主控处理器(main control processor, MCP)等,进行共封装集成设计,形成具有侦干探多功能综合处理能力的微系统芯片。在该微系统芯片上,实现如图2所示的软件架构,将侦干探一体化进行功能拆分,根据各个核心组件的特性,合理利用有限资源,各个核心组件分别进行相应的软件配置。相比传统结构,可实现更高波段、更高吞吐量、更低延时和更佳性能功耗比,同时适用于侦干探多功能系统,具有多功能、可重构、微型化、轻量化以及灵活、便捷等特点与优势。

图3 多功能集成微系统结构Fig.3 Multi-functional integrated microsystem architecture

微型化集成受散热、尺寸以及封装成本与工艺难度等诸多因素影响,并非所有分立器件均适用于微型化集成。本文在考虑上述因素外,还需满足侦干探多功能一体化综合处理能力需求,结合微型化、多功能、高性能以及现阶段已有芯片技术,将高性能ADC和DAC、高性能处理器ARM、大规模FPGA、大容量数据缓存器DDR4 SDRAM(double-data-rate fourth generation synchronous dynamic random access memory)、程序存储器Nor FLASH、时钟芯片、线性稳压电源(low drop out, LDO)以及IPD(intelligent power device)电阻、电容等不同种类、不同工艺、不同材质的芯片和元件,通过三维堆叠等先进系统级封装技术手段,进行集成设计,构成信号处理SiP芯片。核心芯片选用Xilinx公司最新一代UltraScal+系列—RFSoC芯片,该芯片集成RF直采能力的ADC、DAC、多核ARM以及大规模FPGA等,ADC/DAC/FPGA/ARM间的高速互联采用先进的微控制器总线体系结构(advanced microcontroller bus architecture, AMBA),直接在芯片内部相连,很好地解决了外部接口占用空间、IO等资源问题,且集成度高,节省额外的互联线路开销,具有更高吞吐量、更低延时和更佳性能功耗比。该芯片无论体积尺寸、功能密度,还是异构计算架构、计算性能以及能耗比,均适用于微型化集成系统设计。

同时,为了提高系统集成度,降低设计难度、工艺难度和成本,将大容量数据缓存器DDR4 SDRAM、程序存储器Nor Flash以及外围电路如匹配电阻、去耦电容和参考电源等裸芯片、元件通过三维堆叠、引线键合等手段进行集成设计,构成具有独立功能的单颗存储系统芯片。最后,再将独立封装的存储系统芯片、RFSoC芯片以及外围电路和阻容等进行二次封装集成,构成信号处理SiP芯片[45-50]。

2 存储系统集成设计

为了更好地提升系统集成度与简化集成难度,降低工艺复杂度,提升良率,针对信号处理微系统集成中的存储系统集成设计,提出了一种全新的多功能存储系统集成方案:将DRAM芯片、Flash芯片、终端匹配电阻、滤波电容以及参考电源芯片等全部集成在一个微小封装内,构成一颗具备通用能力的存储系统芯片,该芯片同时具备数据缓存、程序存储等功能。除了具有更高集成度之外,该存储系统芯片可将72 bit位宽系统分为32 bit位宽和40 bit位宽(带ECC(error checking and correcting)校验8 bit)两组独立存储器,单芯片可以支持32 bit、40 bit、64 bit以及72 bit这4种不同位宽存储系统应用,另外支持32 bit和40 bit或32 bit和32 bit同时使用,且多片芯片并联使用可扩展更高存储位宽,如128 bit等,具有更强的灵活性和扩展性。

互联拓扑结构对DDRx SDRAM的系统应用至关重要,往往在布局之前,甚至是系统设计初期就要优先考虑。本文在集成设计时,结合系统特点和需求,优先对拓扑结构进行规划与论证分析,并通过建模和仿真验证指导存储系统的拓扑结构设计,从而确保设计的可行性与正确性。

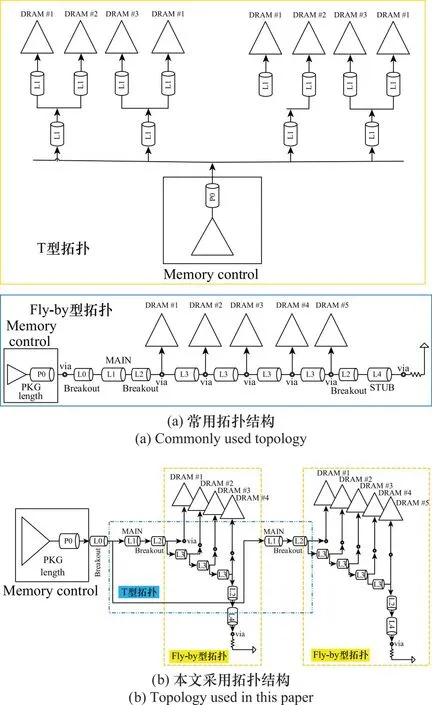

多片DDRx SDRAM颗粒互联设计中,重点为其拓扑结构设计,常用拓扑结构主要有以下两种:Fly-by结构和T型结构,如图4(a)所示。本文提出的存储系统芯片主要设计难点在多片DDR4 SDRAM的堆叠设计与互联拓扑设计,综合Fly-by、T型拓扑结构的优缺点,本文采用Fly-by与T型结构结合的共同拓扑结构和DDR4 SDRAM多片堆叠设计,很好地解决了小面积、低层数的基板布局布线设计以及堆叠芯片键合互联带来的新问题。本文采用的拓扑结构与堆叠设计模型示意图如图4(b)所示,9片DDR4 SDRAM分为两组进行堆叠,其中一组为5层堆叠(40 bit位宽),一组为4层堆叠(32 bit位宽),两组共同构成72 bit位宽(带ECC功能)。

图4 存储器集成拓扑方案对比Fig.4 Comparison of memory integration topology schemes

采用上述拓扑方案,通过对拓扑结构与堆叠键合的联合模型构建、仿真和分析,充分验证该拓扑结构和键合方案的可行性。按照键合线最大长度200 mil、键合线阻抗61 Ω、最大速率3.2 Gbps,进行数据线、地址线、控制线以及时钟线的信号仿真。如图5所示的仿真图中,各信号线眼图效果良好,数据线与地址线的眼宽均满足需求,同时数据线一个UI宽度312.5 ps,地址线一个UI宽度625 ps,反映了数据线和地址线均可在3 200 Mbps速率下正常传输,且有较大设计余量,可补偿在工程实施过程中引入的误差,提高容错率,提升成功率。

图5 存储器集成仿真测试Fig.5 Memory integration simulation test

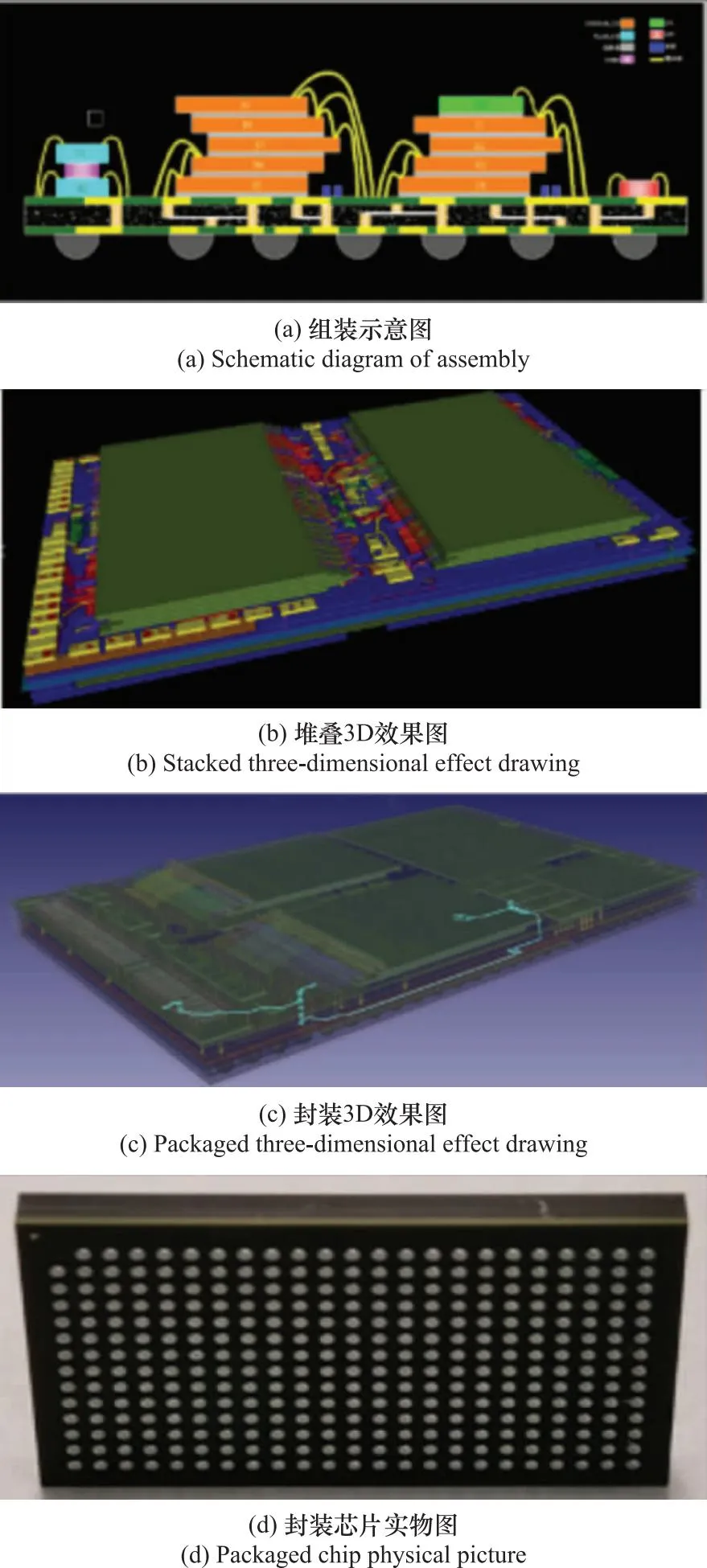

DDRx SDRAM采用两组分开、错位堆叠方式,数据线、地址线等采用金丝引线键合,每组片间地址与控制信号线采用级联引线键合方式,构成Fly-by拓扑结构,终端匹配电阻IPD芯片叠层在最上方。同时,多片Nor Flash也采用堆叠方式,示意图如图6(a)所示。图6(b)和图6(c)分别为DDRx SDRAM堆叠设计三维图、存储系统组装设计三维图。根据工艺种类,需逐步完成组装:① 阻容元件贴装;② 平铺器件粘接、键合;③ 堆叠芯片粘接、键合;④ 塑封、成片;⑤ 植球。最终完成形态如图6(d)所示。

图6 储存器集成效果图Fig.6 Memory integration effect drawing

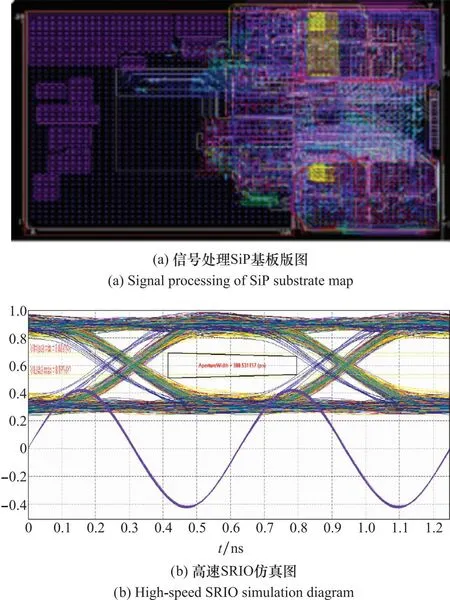

传统分离器件搭建同等大小容量的储存器与本文集成储存器所需面积对照如表1所示,传统分离器件构成的存储系统占用面积最小约2 85 mm2,而本文集成后面积为260 mm2,相比之下面积节约87.5%,且设计应用更加简单、便捷,优势明显。

表1 等容量储存器所需面积对比Table 1 Comparison of area required for equal capacity packets

3 微系统集成设计

采用两次集成设计方案可以大大降低信号处理SiP集成设计复杂度与难度,但在二次集成设计中仍然面临模数混合信号隔离、ADC/DAC通道隔离、高速信号链路处理等难点问题,为解决该类问题,主要设计方法如下:

(1) 模拟信号区与数字信号区、模拟电源区与数字电源区尽可能隔开,减小信号串扰;

(2) 模拟信号、高速信号周围采用地做屏蔽处理,确保传输链路干净;

(3) 模拟信号、高速信号管脚分布周围,尽可能用接地管脚隔离处理;

(4) 严格阻抗控制,尽可能缩短模拟信号、高速信号的传输路径;

(5) 结合封装布局进行仿真,通过仿真结果分析,进行设计优化。

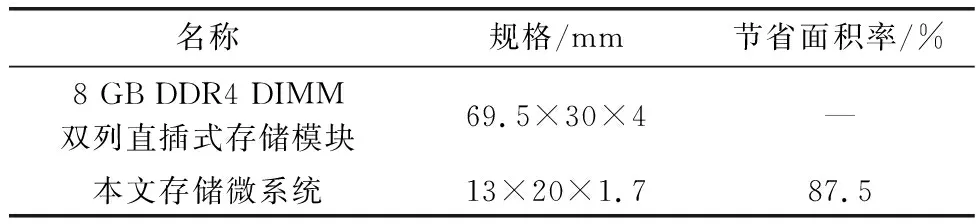

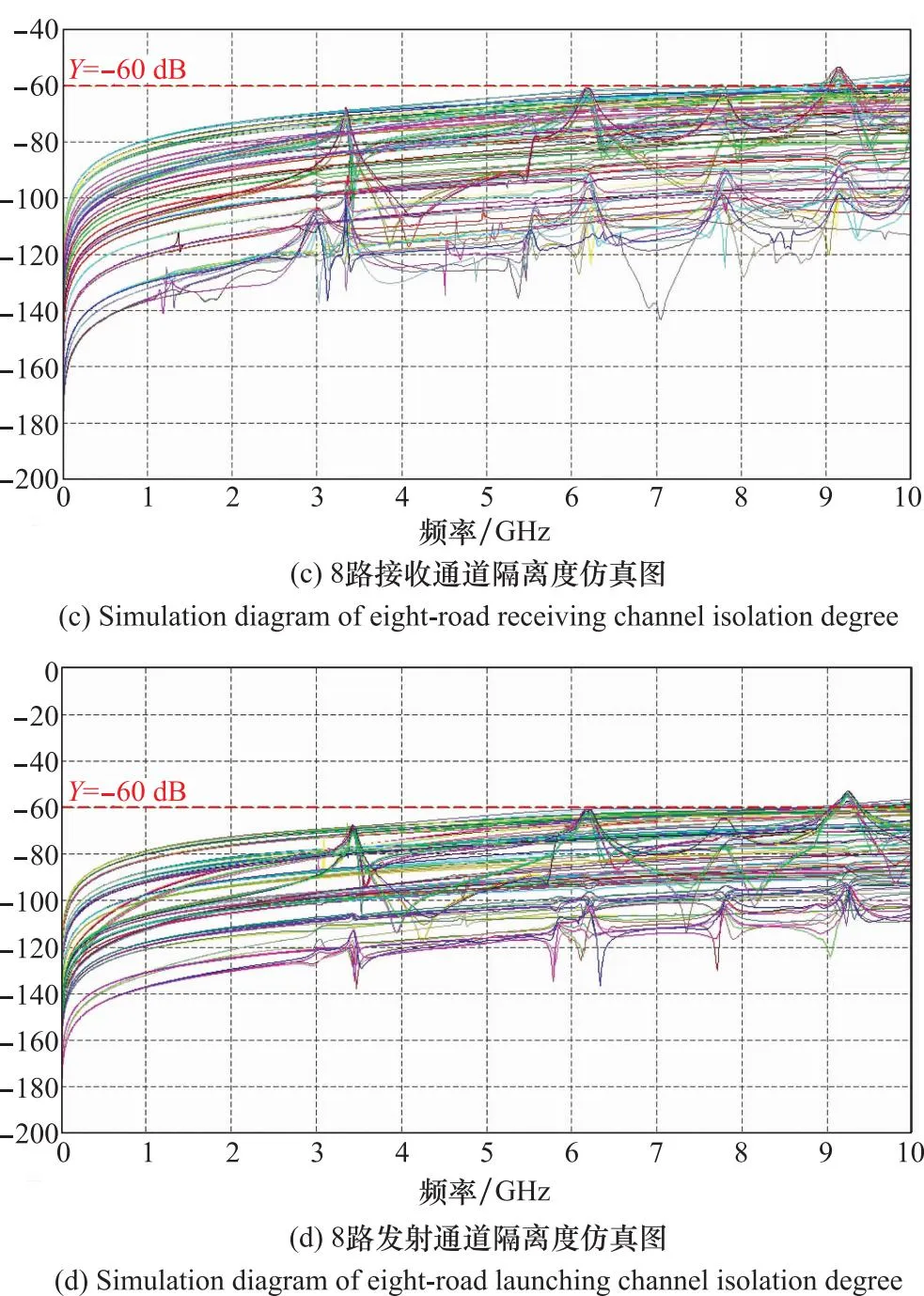

信号处理SiP基板设计版图如图7(a)所示,为了能更好地将信号互联和扇出,高速串行通信(serial rapid IO, SRIO)测试仿真图如图7(b)所示。本文采用14层基板布局方案,通过增加地层和电源层,对关键信号扇出和电源分区做了较好的设计保护。图7(c)和图7(d)分别为接收通道与发射通道的通道隔离仿真结果。

图7 信号处理SiP基板高速接口仿真测试Fig.7 Simulation test of signal processing SiP substrate high-speed interface

仿真时,选择其中一通道作为输入/输出测试通道,同时其他通道保持静默状态,测试频段范围从DC扫频到10 GHz,并观测通道变化情况,计算通道隔离度值:

(3)

式中:V1代表的是仿真中给到激励通道幅度大小;V2代表静默状态通道的最大值。

可见,通道间隔离度优于60 dB,满足信号处理系统应用需求。

散热设计也是信号处理SiP设计中的一大重点。经过评估,如采用全塑封封装方式,核心芯片热量无法被传出,将会直接影响芯片工作性能和系统稳定性。为此,本文采用高导热率金属材料作为信号处理SiP的封装壳体,壳体与芯片之间通过高导热胶进行填充,同时在壳体与基板粘接处预留微通孔,用于释放冷热环境下产生的应力,最终得到信号处理SiP集成芯片如图8所示。

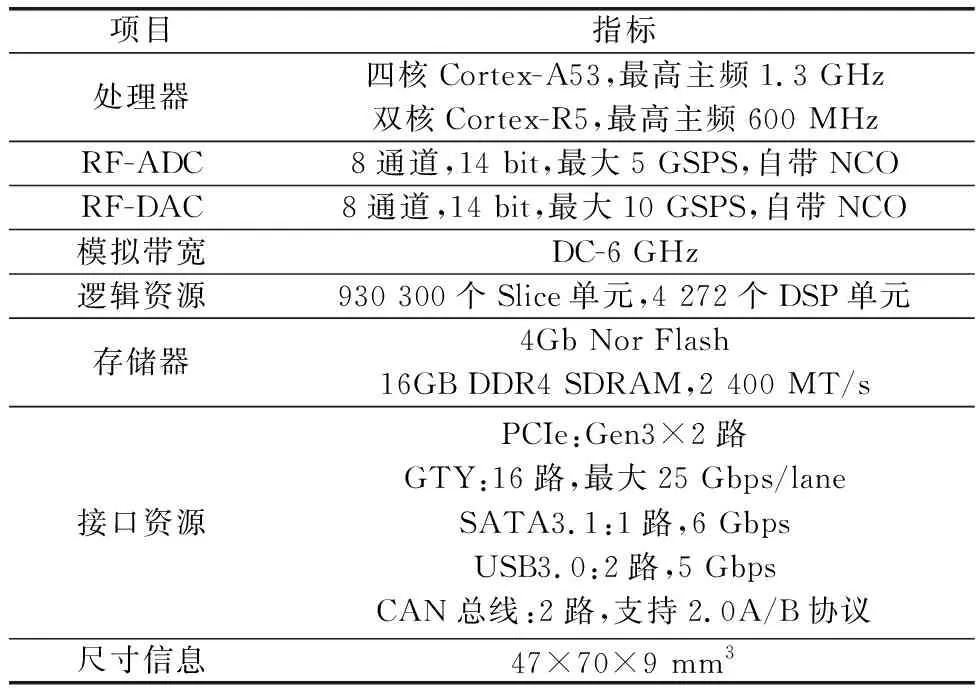

集成的信号处理SiP芯片技术指标参数如表2所示,可满足一体化软件功能中的侦察、干扰、探测信道的收发通道数量要求和信号带宽需求,以及丰富的逻辑资源应用于信号处理算法功能实现和相关信息的提取。还有多个高速接口资源匹配到软件系统用于扩展通信、控制和数据大带宽传输功能。

图8 信号处理SiP集成芯片Fig.8 Signal processing SiP integrated chip

表2 信号处理SiP芯片技术指标Table 2 Signal processing SiP chip technical indexes

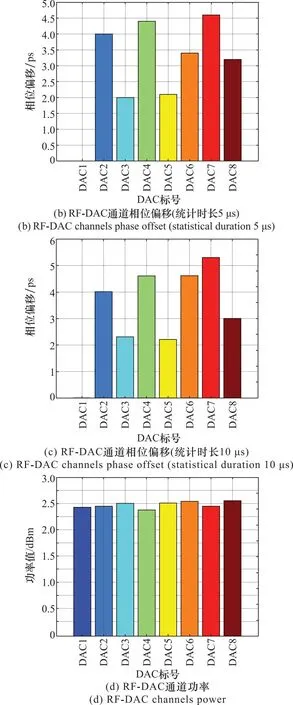

4 收发通道性能参数测试

信号处理SiP接收通道的无杂散动态范围、信纳比以及有效位数值的高低反映了接收通道性能的好坏,对于后续数据处理中算法实现产生了重要影响。对8路接收通道同时输入1 GHz的正弦信号测试得到的结果如图9(a)中的ADC性能测试曲线所示。可以看出,8路接收通道的有效位数变化不大,平均处于8.77 bit。同时,无杂散动态范围(spurious-free dynamic range, SFDR)约为66.43 dBc,信噪失真比(signal to noise and distortion ratio, SNDR)平均值约为55.82 dB,接收通道的性能较好,与期望效果基本符合。另外,对8路发射通道输出3 GHz的正弦波进行功率和相对相位偏移统计分析,测试结果如图9(b)中的DAC性能测试所示,8路发射通道输出功率偏差较小,其最大延迟时间不大于6 ps(DAC1通道作参考),输出相位一致性较好,满足大带宽MIMO、相控阵以及数字阵系统应用需求。系统使用时,仅需确定前端RF组件的延时时间即可实现系统校正,简化了系统校正的测试流程和复杂度。

图9 多通道收发模拟转换器性能测试Fig.9 Performance test of multichannel transceiver analog converter

5 实验测试

根据集成信号处理SiP芯片性能参数以及一体化软件功能架构,本文多功能测试系统采用如图10所示的微系统专用Socket测试环境,实现3个功能同时进行收发自回环测试。首先,对多通道模拟转换器进行使能,其中侦察功能配置为一发一收测试通道,对2 GHz带宽内的信号进行侦收。其次,干扰功能配置为两发一收测试通道,进行3种间歇采样转发干扰策略的切换。然后,探测功能配置四发四收测试通道,对设定目标完成相关信息的识别。

图10 系统测试环境图Fig.10 System test environment diagram

对于侦察功能测试,上位机根据如表3所示的信号参数生成10个不同频点叠加的波形数据,经过多倍插值器和数字上变频将输入信号经过发射通道输出的频谱如图11所示,中心频率为1 GHz,占用带宽为2 GHz。再由采样率为4.096 Gsps的ADC将该信号接收回来,经由数字下变频和2倍抽取后变为零中频的宽带复信号。

表3 发射波形信号列表Table 3 List of transmitted waveform signals

由表3可以得知,信号的带宽最大为40 MHz,所以将接收回来的数据频带可以划分32个信道,每个信道占用的带宽为64 MHz。将宽带复信号通过32个多相滤波器组和32点FFT处理后,得到的信道侦收结果如图12所示。在结果中,除了将设定的信道号与发射波形一一对应之外,还能看到信道6、17和26也存在信号,缘由是划分的32个多相滤波器组的子滤波器通带只有32 MHz,信道5、16和25中的信号带宽与载频相加,超过了滤波器的通带范围,导致信号进入了临近信道。所以,后续通过门限判决将泄漏的信号剔除,从而正确侦收到10个信号。

图11 DAC输出大带宽信号频谱Fig.11 DAC outputs large bandwidth signal spectrum

图12 信道化处理结果Fig.12 Channelized processing results

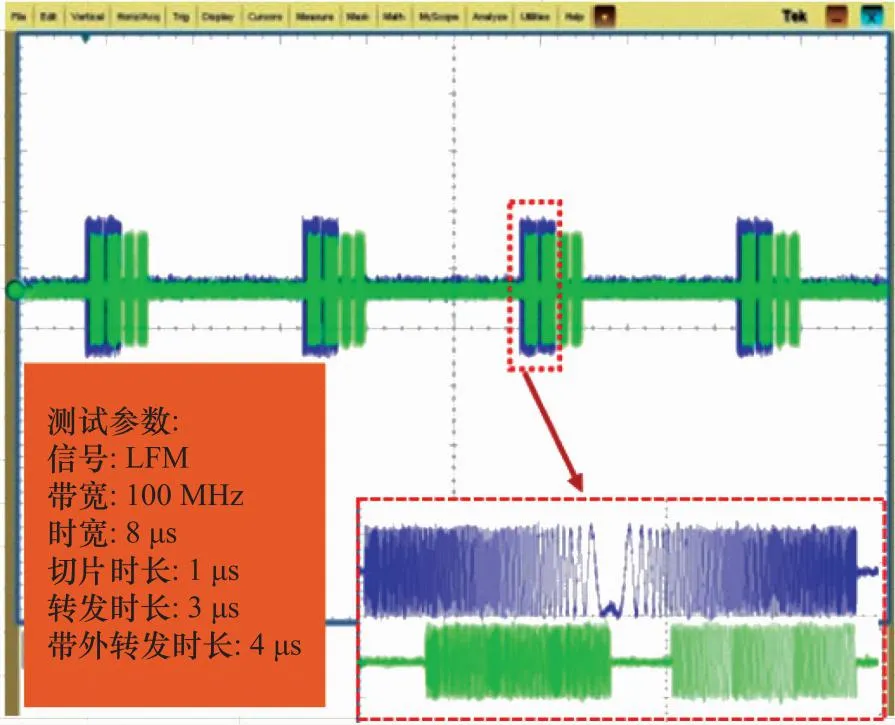

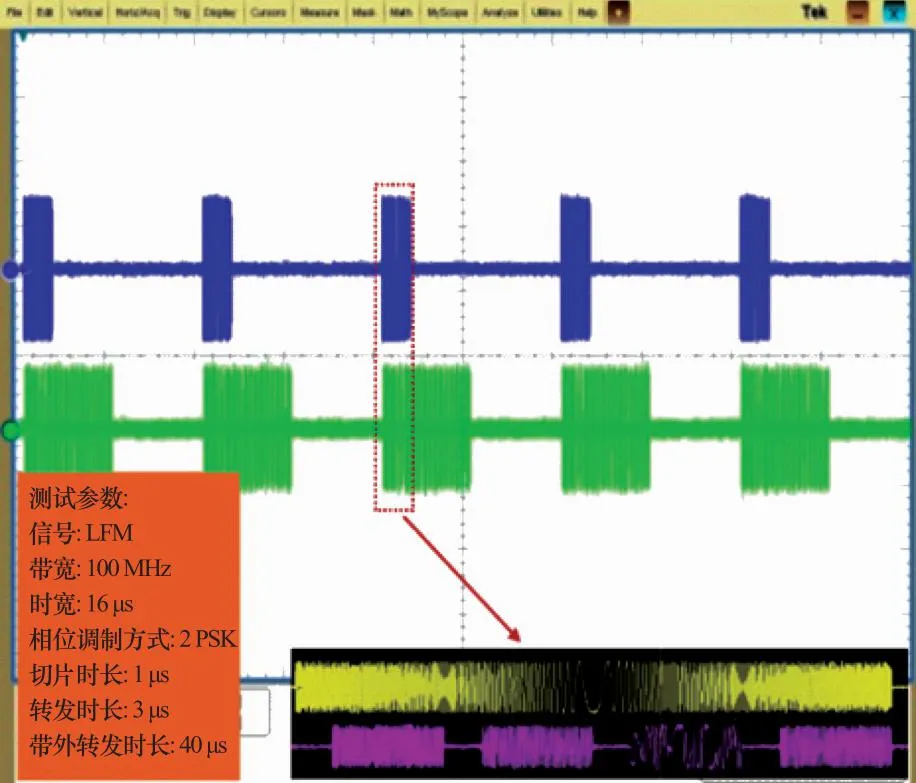

对于干扰功能测试,上位机将相关参数和发射波形数据下发到FPGA端,并完成参数装订,后续只需要更改相位码元序列和转发次数即可完成干扰模式的切换。波形数据通过一路DAC完成插值和数字上变频自回环到一路ADC,采集的数据完成抽取和下变频后,经过序列编号和储存后,由相关干扰模式将编号数据再经由另一路DAC完成干扰数据的输出。同时,为了增加干扰覆盖范围,在脉冲之外自由组合转发已编号切片数据。采1 μs转发1 μs的间歇采样直接转发干扰如图13所示。采1 μs转发3 μs的间歇采样重复转发干扰如图14所示。并且附带脉冲外转发4 μs,为采1 μs转发3 μs并带有随机2PSK相位调制的间歇采样重复转发干扰和脉冲外转发40 μs如图15所示。

图13 间歇采样直接转发干扰Fig.13 Intermittent sampling directly transmit jamming

图14 间歇采样重复转发干扰Fig.14 Intermittent sampling repetitive transmit jamming

图15 间歇采样随机相位调制重复转发干扰Fig.15 Intermittent sampling random phase modulation repetitive transmit jamning

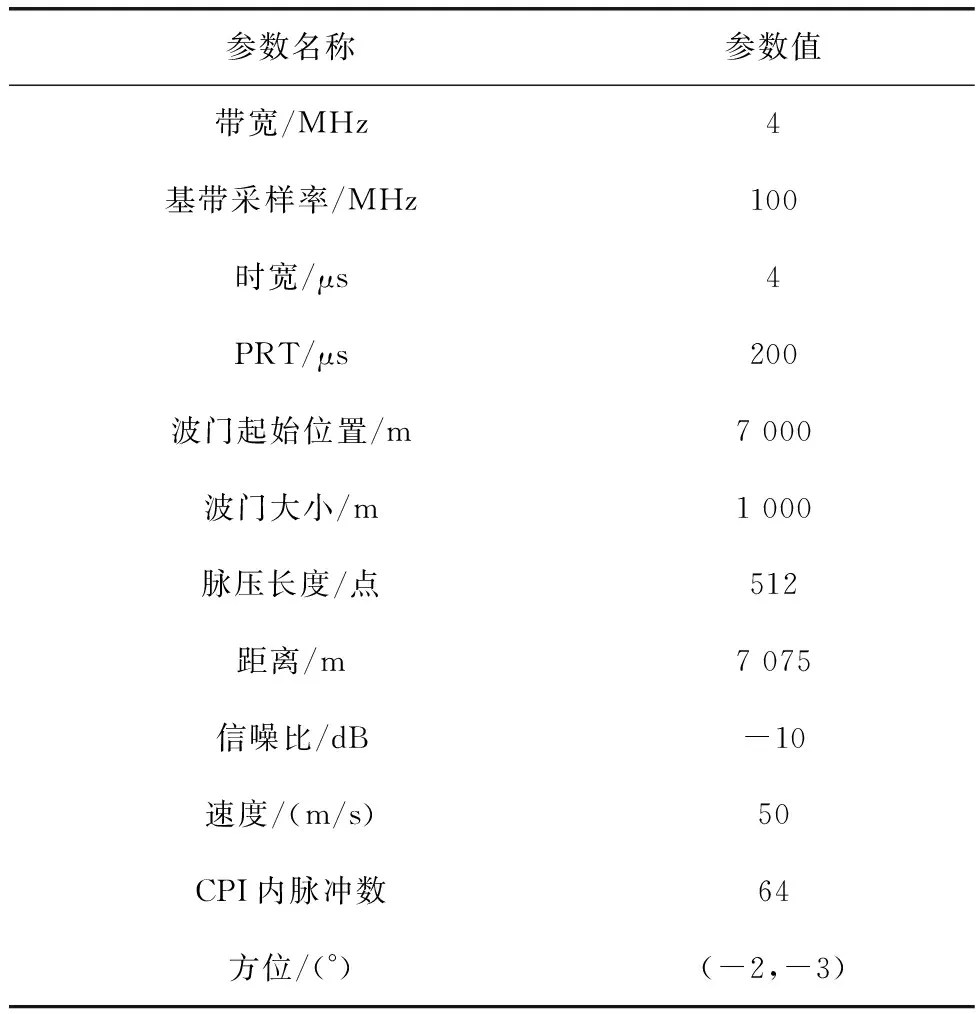

对于探测功能测试,主动MIMO雷达相关测试参数如表4所示。

表4 探测功能目标参数设置Table 4 Detection function target parameter settings

首先,四路DAC将四路正交的波形发射到天线阵元,再由ADC采集天线阵元接收回来的四路数据,经由在FPGA端两级波束形成和脉冲压缩处理,再由ARM端完成目标识别算法,最后得到的目标信息结果如图16所示。可以看出,得到的目标速度、距离和方位信息与设定信息一一对应。

图16 主动MIMO雷达探测测试结果Fig.16 Active MIMO radar detection test results

所以,软件一体化在硬件一体化的基础上更进一步地节省了系统的空间需求,能够带来更具有灵活性、便携性的性能优势。

6 结 论

本文从3种功能软件一体化需求出发,提出了一种新的集成硬件微系统实现多功能方案,通过对后摩尔时代下的多种先进封装技术(如三维堆叠、金丝引线键合、IPD、RDL等)进行混合集成应用,将多通道RF直采的DAC/ADC、FPGA、ARM以及多功能储存芯片MCP等器件进行共封装集成设计,形成具有性能高、体积小以及多功能的信号处理SiP芯片,并针对该芯片完成了多通道ADC和DAC的隔离度、幅相一致性、无杂散动态范围和有效位数等相关性能参数的测试验证。最后,基于该芯片构建了侦察、干扰和探测多功能一体化软件应用场景,并完成验证。结果表明,本文研究的侦干探多功能一体化微系统可灵活实现多功能一体化功能,并兼有体积小、重量轻以及多功能、高性能的优越性能,验证了方案的可行性与工程应用价值,具有较好的应用前景。