一种天文图像的光纤传输系统的设计*

李汉青,李彬华,王春荣,金建辉

(昆明理工大学信息工程与自动化学院,昆明 650051)

在天文成像观测领域,由于所传输的图像数据量大,多采用Camera Link、GIGE、网络和光纤等方式。每一种方式都有其优点和局限,比如Camera Link带宽可达7140Mbps,但传输距离限制在10m以内,不能应用于远程传输。利用Gig EVision技术可以在1000Mbps的速率下传输100m,如果需要更远的距离则可以使用中继或光纤媒介[1]。通过10/100M的普通TCP/IP网络传输,其局限性是速率比较低。以一个2k×2k相机实验为例,在不使用网络加速手段时,将采集到的一幅图像上传至计算机大约需要70s的时间。国家天文台曾有人通过网络加速的方法,使传输速率得到较大提升,可以达到70~80Mb/s[2]。此方法大大提高了传输的时效性,但是,可靠性随之降低。因此,采用网络加速的方法在某些时候并不适用。为兼顾传输时效性和传输距离,可以采用“USB+光纤”的方式,先用USB接口转光纤接口的设备将数据转化为光信号以适合在光纤中远距离传输。在计算机端,再用光纤接口转USB接口的设备恢复为原始的图像信息,通过USB接口上传到计算机[3]。

天文图像传输所采用的通信系统大都是针对整个观测系统的特点而开发的专用系统,通用性稍差。结合一个正在研制的天文用CCD相机系统的要求,并参考UCO/Lick CCD相机的光纤传输电路,开发出一种可满足当前课题要求的天文图像光纤传输系统。本文介绍该系统的结构、硬件和VHDL设计思想和实现的技术。

1 传输系统设计总体思想

整个系统要实现的功能是将CCD相机采集的图像数据通过光纤信道快速上传到计算机。在相机端,要将图像数据进行编码和电光转换,并送入光纤信道;在计算机端,要将接收到的图像数据光电转换和解码,并通过PCI总线发送到计算机。整个系统主要以数据的光传输为基础来构建。因此,在系统设计时,需要首先考虑光纤的选型,其次是PCI总线接口芯片、编码/解码器件、电光/光电转换器件和作为控制用的FPGA等关键性元器件的选择。

光纤分为多模光纤和单模光纤,其通信模式、通信速率、通信距离以及纤芯大小与所使用光波的工作波长均有很大差异。总的来说,单模光纤频带宽、传输容量大,传输距离长,一般不用光放大就能以10Gbit/s及以上速率传输几十千米。多模光纤的带宽、容量以及传输距离不及单模光纤,速率一般在10Gbit/s以下,距离一般在1~2km,但其芯径粗、数值孔径大,连接时不必精确对准,操作方便简单。基于以上分析和课题具体要求,选择多模光纤。

图像数据上传到计算机端后,需要经过PCI总线接口芯片送到计算机存储器中。在比较PCI9042和CY7C09449这两片常用的芯片之后发现,CY7C09449支持DMA功能,可以作为PCI主设备发起传输,并且其内部有一个16KB共享双口RAM,能增强设计的灵活性[4]。因此,PCI接口控制器采用CY7C09449。对于编码/解码器件、电光/光电转换器件,参考Lick CCD相机的电路,使用CY7B923/933和HFBR1119T/2119T。FPGA采用ALTERA公司的EP1C6Q240,它有近6000个逻辑单元、185个用户I/O、92160比特存储器和两个PLL,能满足设计所需的资源。

根据以上分析,本系统需要在相机端和计算机端各设计制作一块电路板,分别命名为BOARD_A和BOARD_B,均采用4层板设计。BOARD_A主要由数据缓冲器、FPGA、编码器、电光转换器以及配置芯片和电源模块组成。FPGA实现对数据16bit/8bit转换以及对编码器的控制。BOARD_B由光电转换器、解码芯片、大容量FIFO、FPGA、PCI接口芯片以及配置芯片和电源模块组成。各模块和信号流程图如图1。

图1 传输系统模块及其信号流程图Fig.1 Block diagram of the transmission system

2 传输系统的电路设计

2.1 FPGA周边电路的设计

FPGA的外围电路主要包括电源电路、配置电路、用户IO接口以及数据/信号缓冲器。选用的FPGA器件需要1.5V和3.3V两个电源,其中1.5V的电源为FPGA内部的PLL和逻辑单元供电,3.3V的电源给FPGA的IO供电。分别采用LMS1585ACT-1.5和LM1085-3.3两种集成稳压器。FPGA提供足够的IO引脚,但使用时要考虑布线要求,如布线长度和复杂度等,所以需要根据芯片的布局(即位置)选用合适的IO引脚。

对FPGA进行编程和调试的接口可以使用JTAG接口,也可以采用AS接口。JTAG接口可以用来调试EP1C6,下载速度快,而且支持在线调试,但它不能用来编程配置芯片,如EPCS。AS接口可以用来编程EPCS芯片,同时也可以用来调试。具体过程是首先编程EPCS,然后通过EPCS配置FPGA,运行程序。EPCS芯片有高达十万次的重复编程能力,能满足调试需要。因此,为了简化电路,该设计中只采用AS接口。其与EP1C6的电路连接采用了串行配置器件EPCS1&EPCS4说明书中的方案。

需要注意的是,当使用AS模式时,EP1C6的模式选择引脚MSEL0和MSEL1要置0。另外,为了方便调试,要在QUARTUSII软件中选中DEV_CLRN选项,使能此引脚。当这个脚被置低,所有的寄存器都会被清零[5]。在EP1C6的DEV_CLRN管脚上接一个低电平复位电路,以此作为该器件的复位管脚。

2.2 编码/解码电路和光发送/接收电路的设计

编码/解码器使用CYPRESS公司的CY7B923/933-SC芯片。该芯片的传输速率最高可达330Mbps;具有8B/10B编码、10-bit解码能力;兼容光纤、同轴电缆、双绞线等介质;使用+5V单电源供电,除正常的工作模式外,还有内置的自测模式。在工作之前,可以先进入自测模式,检测整个光纤链路的通信。此外,自测模式还可以用来粗略估算系统的误码率。

光发送/接收器使用HP公司的HFBR-1119T/21119T。该芯片用于50μm和62.5μm的多模光纤,工作波长为1300nm,可以以266MBd的速率传输1500m[6]。

最后,参考CY7B923/933、HFBR-1119T/21119T的说明书上推荐电路,并结合系统要求,设计的编码/解码电路和光接收/发送链路的原理图如图2。

图2 光发送/接收电路原理图Fig.2 Schematic diagram of the transmitter and receiver

3 FPGA的设计

FPGA在系统中的主要作用是对编码器和解码器进行控制、产生PCI接口控制器的驱动波形、生成在不同时钟域之间数据传输所需要的FIFO以及对FIFO进行控制。FPGA的设计在Quartus Ⅱ开发环境下使用VHDL语言和电路原理图相结合的形式完成。

在光发送端:当检测到锁存器的锁存信号CCLK有效,说明数据已到来,使能锁存器将16bit数据锁存到两个8位锁存器中,然后分两次写入FIFO。当检测到FIFO半满时,CY7B923使能信号ENA和FIFO读请求RDREQ有效,数据读出。FIFO的读时钟采用CY7B923输出的时钟RP以保证FIFO和编码器同步。由于RP在编码器的ENA有效后才输出,即半满之前FIFO读时钟无效,用来指示空状态的RDUSED信号一直为0,也就是一直为空,就一直不能触发读出。因此,FIFO的读时钟要一直有效。鉴于此,在CY7B923使能信号ENA和FIFO读请求RDREQ有效前,采用FPGA内部时钟作为读时钟,ENA和RDREQ有效后读时钟采用编码器输出时钟RP。

此外,为便于调试,在发送端的FPGA中还实现一个产生模拟图像数据的模块。该模块产生一个2080×2048个像素,每一行的第N个像素都用16bit的N的二进制表示。

在光接收端:当FPGA接收到CY7B933的准备好标志信号RDY有效,表明数据已准备好,此时使FIFO芯片SN74V293写请求有效。读时钟采用解码器的输出时钟。当FIFO到达约定值时,产生PCI接口芯CY7C09449的驱动波形,向其内部的双口RAM发送数据,当RAM中数据达到8KB时,触发DMA传输。通过PCI总线将数据传送到PC。

4 系统仿真和实测结果的分析

4.1 数据生成模块的仿真与测试

模拟数据生成模块产生的是一幅2080×2048个像素的图像,共2080行、2048列,每行的像素值从1到2048依次递增,即每行的输出从0000000000000001到0000100000000000递增。图3是数据生成模块仿真波形的一部分结果。数据输出端口dout为2048时,对应的是某一行的最后一个像素,下一时刻dout输出值为1,则表示是下一行的第一个数据。从图中可以看出,输出数据是依次递增的,这说明设计模块内部逻辑是正确的。

图3 数据生成模块仿真波形Fig.3 Simulated waveform of the data-generating module

图4是在FPGA的IO引脚上实测模拟数据输出的波形。图中从上至下的波形依次为,时钟信号CLK、FIFO读请求信号RDREQ、八位数据信号d7~d0。读请求高有效,在CLK的下降沿读出。从波形中看出,在相邻4个读请求有效时,读出的数据依次为:00000111,00011101;00000111,00011110;00000111,00011111;00000111,00100000。即相邻的4个像素值为0000011100011101;0000011100011110;0000011100011111;0000011100100000,依次递增。实测结果显示,输入到CY7B923的数据是连续的,与仿真的结果相同,表明Board_A板上的模拟数据发送模块产生的数据正确。

图4 写入CY7B923的数据波形Fig.4 Waveform of the data written into the CY7B923

4.2实测结果

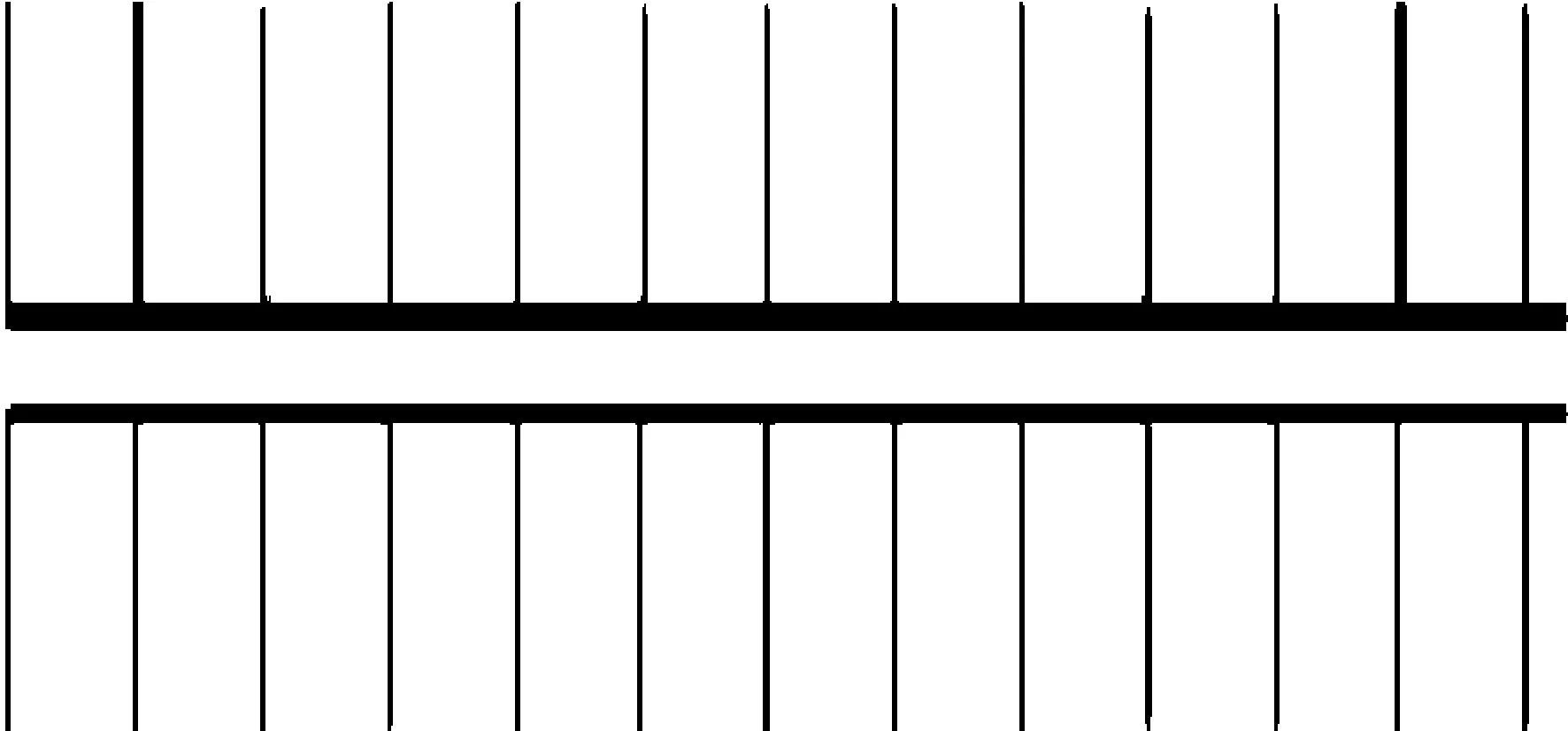

用示波器在BOARD_A的FPGA输出端和BOARD_B的PCI接口芯片之前,测试某一时刻的波形,如图5。

图5 BOARD_A发送和BOARD_B接收的数据Fig.5 Data transmitted by the BOARD_A and received in the BOARD_B

图5中,上面8位是接收端的波形,下面8位是发送端的波形。从图中波形可以看出,数据在经过编码、并串转换、电光转换、光纤传输、光电转换、串并转换、解码等一系列动作之后,接收端实测的数据与发送端的一致,表明整个传输系统工作正常。通过示波器还可以看出,在接收端产生了一个确定的传输延迟,延迟量约500ns。这个延迟主要由编码/解码、电光/光电转换产生。此外,中间的74AC541缓冲器也会产生约10ns的延迟。

4.3 自测模式下的误码率估算

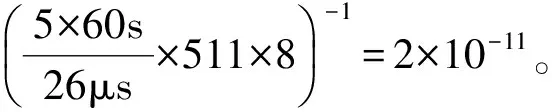

误码率估算借鉴文献[7]中的方法。对于本系统来讲,具体实现的方法是将CY7B923的BISTEN、ENN和CY7B933的BISTEN引脚置为低电平,选择自测模式。在该模式下,CY7B923产生循环发送的伪随机序列,每循环为一组,共511个字节。在一个循环中,读脉冲RP产生一个周期的低电平,RDY产生一个高电平。CY7B933的读时钟引脚CKR输出的20MHz时钟作为FIFO的写时钟。接好光纤上电后,用示波器检测相关引脚,波形如图6、图7。

图6 RDY、RP和CKR信号波形Fig.6 Waveforms of the RDY, RP,and CKR

图7 RDY和RP信号波形(脉冲)Fig.7 Waveforms of the RDY and RP

5 结束语

本文结合一个天文用CCD相机项目,设计出一种用于图像数据传输、抗干扰能力强、带宽高的光纤传输系统。介绍了系统硬件电路和FPGA的设计方案和实现技术,对FPGA数字部分进行了仿真并给出部分模块的仿真波形,对系统的重要模块及整个通信链路进行实测,同时估算了误码率。分析表明,所测结果正确,估算误码率也较低。目前,硬件工作基本完成,正在进行PCI驱动程序的设计工作。

致谢:感谢国家天文台叶彬浔研究员、宋谦研究员,他们在本项目研究之初提出过一些建设性的意见和建议。

[1] 北京凌云光子技术公司.http://vision.lusterinc.com/episteme/framegrabber.html.2009-11.

[2] 段之昱.天文CCD相机控制系统的软件研究[D].中国科学院研究生院硕士学位论文,2006-11.

Duan Zhiyu.A study of Control and Acquisition Software of an Astronomical CCD Camera[D].Master dissertation of Gradnate University of the Chinese Academy of Sciences,2006-11.

[3] Wei Mingzhi,Stover Richard J.A USB 2.0 computer interface for the UCO/Lick CCD cameras[J].SPIE,2004,5499:476-480.

[4] CYPRESS Company.128Kb Dual-Port SRAM with PCI Bus Controller(PCI-DP).2002.

[5] Altera Corp.Cyclone Device Handbook.2008.

[6] Agilent Technologies.Inc Fiber Optic Transmitter and Receive Data Links for 266 MBd Technical Data. 1999.

[7] 郑剑锋.水下远程数据有线传输技术研究[D].中国科学院研究生院博士学位论文,2004.

Zheng Jianfeng.Researches on Underwater Long-Distance Cable Data Transmission Techuology[D].Ph D Dissertation of Graduate University of the Chinese Academy of Sciences,2004.