MSC8122TVT6400及其最小应用系统设计*

王厚磊 张友爱 于 奇

(中国船舶重工集团公司第722研究所 武汉 430079)

1 引言

在通信、雷达、声纳等电子系统中,对数字信号处理模块的性能要求越来越高,传统的方法是利用并行处理技术,选用多片DSP构成并行处理系统,这种方法的缺点是对外部总线的依赖性太强,易产生总线瓶颈,还有布板较复杂,功耗也比较大。选用多核DSP既可以提高数字信号处理的性能又能避免以上的缺点。

MSC8122TVT6400型DSP是飞思卡尔公司生产的一款四核数字信号处理器,该处理器能多核并行处理。运算速度是同一代单核DSP的四倍,且有成本低、功耗小、性能高、外设集成度高,数据以及程序存储量大的优点。它采用内核1.2V供电,外设3.3V供电,功耗只有2W,每个内核主频为400MHZ,4个内核共有 1.6GHZ,可达6400MMACS每秒的运算能力[1],是高速数据处理和大量数据处理时理想的选择。

2 MSC8122TVT6400简介

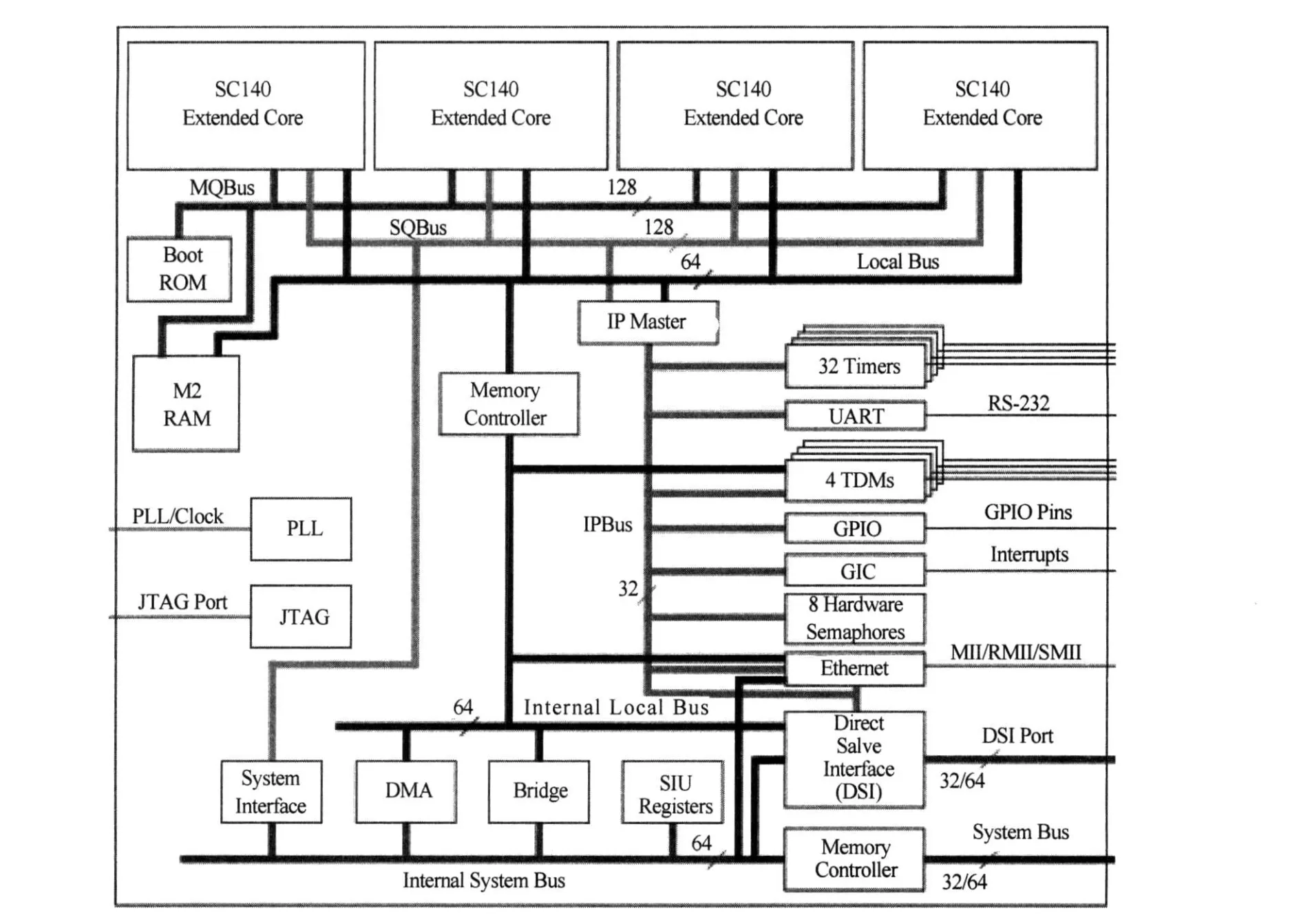

飞思卡尔公司的 MSC8122TVT6400四核DSP,利用的是Motorola和 Lucent共同开发的StarCore 140内核的扩展核,每个StarCore140扩展核由一个StarCore140核、224KB的内部存储器和扩展的QBus系统组成。StarCore140内核是第一个低功耗高性能具有特大指令字组(VLIW)结构的16位定点DSP内核。StarCore140核有四条16位数据通路,每一条有一个组合的ALU/MAC资料栏单元(BFU),每一个BFU包含一个40位柱式移位器,两条32位地址总线和两条64位数据总线,用来传输数据。128位程序总线能在一个周期内检索八条16位指令[2]。

图1 MSC8122TVT6400的内部结构

如图1所示,MSC8122TVT6400内部集成了4个StarCore140扩展核,提供1.43MB内存(4×224KB M1及476KB M2)、一个高宽带外部存储器接口、1组丰富的高级外围设备(包括10/100Mbit/s以太网控制器)和高吞吐量处理器。各个内核由SQBus、MQBus和 LocalBus连接,MQBus共享公共内存资源,SQBus主要是用来响应外部中断。SQBus和 MQbus都工作在 StarCore140内核频率,允许数据线进行128bit读操作和 64bit写操作。一个高效的仲裁器决定哪个StarCore140内核使用MQbus和SQBus,通过一个像停车场一样的机制,仲裁器决定最后获胜者取得 MQbus和SQBus总线的使用权,一直到另外一个StarCore140核开始另外一次请求。LocalBus主要负责外部主机和各个外设接口与内核的通信,此外各个内核的M1存储器也是通过通过LocalBus实现直接存储器传输(DMA)的。

MSC8122 TVT6400有高性能(每秒64亿次乘累加)和低功耗(功耗仅为2W)的特点,可以减少系统的DSP数量和那些高成本高功耗的辅助ASIC和FPGA,同时低功耗和单芯片的设计有助于减少实际应用系统体积及缓存散热问题。

3 最小应用系统

根据数据终端处理机的需求,以MSC8122TVT6400为核心构建数字信号处理最小系统板,系统电路图可按以下几个模块设计:复位电路;时钟生成电路和400M主频设计;电源模块设计;存储器模块;数模/模数转换模块;JTAG仿真接口;以太网接口;串行口;系统框图如图2所示。

图2 系统整体框图

3.1 时钟电路的设计

向DSP提供时钟一般有两种方式:一种是利用DSP内部提供的晶体振荡器电路,即在DSP的X1和X2管脚间引入一个晶体来启动内部振荡器;另一种是外部时钟源直接接入X2/CLKIN引脚。本设计采用了外接时钟源的方法。

外接一个25M时钟源为DSP提供时钟。时钟配置模式由MODCK[1-5]决定;设计中这样配置:MODCK[1-2]=11,MODCK[3-5]=000。这时五个因数 PLLRDF=1,PLLFDF=2,PLLODF=2,PLLTP=7,BUSDF=4;这样CLKIN=25M,内核时钟400MHz,总线时钟100MHz。

内核时钟与总线时钟,两个时钟同步且相位相同[3]。其中内核时钟为Starcore140扩展核提供时钟,包括SC140内核;M1、M2内存 ;PIC;LIC;指令高速缓存;写缓存。总线时钟为外部接口提供时钟,包括系统接口单元(SIU);直接存储器传递(DMA);直接从接口(DSI);时分多址接口;定时器;串行口;GIC;以太网口。

3.2 复位模块

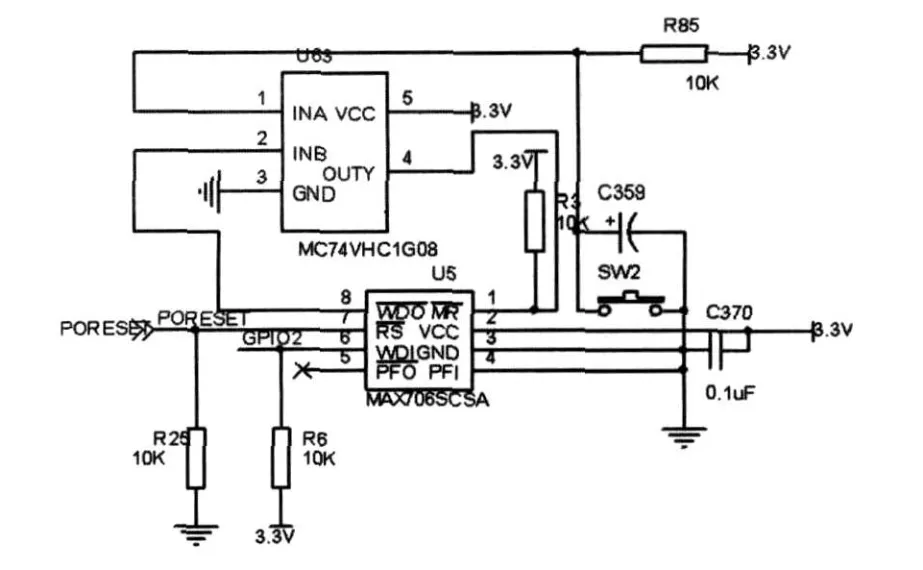

MSC8122TVT6400复位管脚有三个上电复位(PORESET),硬件复位(H RESET),软件复位(SRESET)。在电路设计中对芯片的上电复位用看门狗电路复位,硬件复位作为输出,复位JTAG口。复位采用上电复位电路,由电源器件给出复位信号一旦电源上电系统便处于复位状态,为使DSP初始化正确,应保证 MSC8122TVT6400的VDD和VDDH稳定16个时钟输入周期之后再使用上电复位管脚。

复位电路如图3所示,DSP的GPIO2向WDI输入交替的01电平,当程序出现跑飞,如果大于1.6s没有电平输入,WDO就输出一个200ms的低电平复位信号,把它和手动开关经相与后输出到手动复位管脚,作用是当有手动按下开关或是WDO有复位电平输出,都会使MAX706SCSA的复位管脚输出复位信号,使DSP芯片复位。

图3 看门狗复位模块

图4 电源模块设计

3.3 电源电路设计

DSP芯片MSC8122TVT6400内核电压3.3V,I/O电压1.2V,本设计采用5V电压源供电,用电压转换芯片LM20145进行电压转换。它能连续输出电流高达5A,是可调频同步降压稳压电压转换芯片,采用恒流模式控制电路,对各种输出电容能稳定工作,器件的输入电压为2.95V到5.5V,内部有过压保护(OUP)和过流保护(OCP)。

电源模块设计连接图如图 4所示,下面的LM20145芯片的PGOOD输出连到上面一片LM20145的使能端口,内核上电后下面LM20145的PGOOD管脚输出一个低电平信号,输入到上面LM20145的使能端,上面的LM20145开始工作输出外围电路需要的3.3V电压。这样能保证内核先上电,外围后上电,进而使DSP芯片正常工作。

3.4 外部存储器和flash的设计

本设计的总线时钟频率是100MHZ,外部存储器的存取速率应略大于总线的时钟频率,才能够同步内核的工作[4]。设计选用 HY57V561620T-H作为DSP的外部存储器,这片SDRAM的动态存储空间 32Mb×16Bit,正常的时钟频率是133MHZ,满足总线时钟的要求。

DSP的自举方式采用外部 flash自举,选用16MB的flash存储 Bootload程序,把程序通过JTAG口写入flash,当电路板再次上电是DSP通过flash自动配置DSP的内部寄存器实现自举。选用flash芯片S29GL016A,存储空间16MB。

3.5 串行口设计

串口的发送和接收管脚分别是 DSP的GPIO27-28,该管脚通过IPBUS与外部主机、四个内核相连,外部主机通过LOCAL BUS与IPBUS相连,而四个内核通过SQbus连到IPBUS上。串口配置由五个寄存器完成,所有的串口配置寄存器要配置进IPBUS的地址空间[5]。

因为MSC8122TVT6400内部集成有并串转换的电路,所以在外部只需要接一个电平转换芯片,将MSC8122TVT6400中SCI接口的 T TL电平转换成RS-232电平,即进行串口电平转换,然后用DB9连接器外接就行了。本设计采用了MAX3232芯片,功耗低,集成度高+3.3V供电具有两个接收和发送通道,在本设计中只用了一个通道,剩余的那个通道用于扩展功能备用,V+与V-,C+与 C-用0.1uF的电容相连,这样利用MAX3232把DSP外围电平转换成 RS-232电平[6]。

3.6 其他部分的设计

1)以太网口设计,MSC8122TVT6400芯片本身支持三种模式MII,RMII,SMII.能够支持多种物理指令。本设计选用的是 MII模式,用LXT971A实现的物理层转换,10M/100M自适应的以太网数据传输[7]。

2)系统设计了外部模拟信号输入端口,可以对模拟信号进行数模转换然后再对生成的数字信号进行数字信号处理,选用 TI公司的TLV320AIC10双向转换芯片,设置合适的采样频率,由 Fs=MCLK/(256*N),可设置 N=2,MCLK=4.096MHz,可得采样频率为32kHz。从在这里输入音频信号,DSP可对其进行调制解调等算法运算。

4 集成开发环境及系统测试结果

软件开发平台采用Codewarrior,VC6.0用于单帧调试时对照使用,Codewarrior是由Metrowerks公司开发的适用于飞思卡尔DSP和MCU产品开发的交叉编译器。本课题采用的是CodeWarrior forStarCore,即专门用于采用StarCore核的DSP产品开发配套软件集成开发环境[8]。CodeWarrior提供一套灵活的及高效的软件开发组件,包括工程管理器、编辑器、搜索引擎、源代码浏览器、软件编译和连接器以及调试器等。CodeWarrior界面如图5所示。

图5 CodeWarrior界面

系统平台搭设完成后对各个模块进行了调试,经多次努力终使各个模块均能正常工作,下面是串口和网口的调试过程。

串口配置由五个寄存器完成,所有的串口配置寄存器要配置进IPBUS的地址空间,SCIBR决定波特率;SCICR决定传输长度,传输中断,传输模式,奇偶校验等;SCISR是串口状态寄存器,内核通过查询状态寄存器的状态位来控制发送和接收过程;SCIDR数据寄存器,主要是暂存要传输的数据,SCIDDR是串口数据方向寄存器。

根据需要采取Run Mode传输模式,由波特率计算公式UART band rate=System clock/(16×SCIBR[12-0])得波特率11520bps,不设奇偶校验位。

串口配置程序如下:

;SCI Baud-rate Register

SCIBR equ 0x1000

;SCI control register

SCISR equ 0x1008

;SCI Status register

SCISR equ 0x1010

;SCI Data Register

SCIDR equ 0x1018

;SCI Data Direction Register

SCIDDR equ 0x1028

在PC端运行串口调试助手,该软件可以在网上免费获得,软件运行后根据实际运行环境进行配置,经测试,模块转发数据正常。

网口的调试,直接支持IEEE Std.802.3标准协议的以太网接口是MSC8122TVT6400重要特点,需配置的寄存器有以下几类:通用控制及状态寄存器、FIFO控制及状态寄存器、发送控制及状态寄存器、接收控制及状态寄存器、MAC寄存器、MII配置寄存器、MIIGSK寄存器、RMON计数器、RMON寄存器、无用信号功能寄存器、模式匹配寄存器、数据结构体。

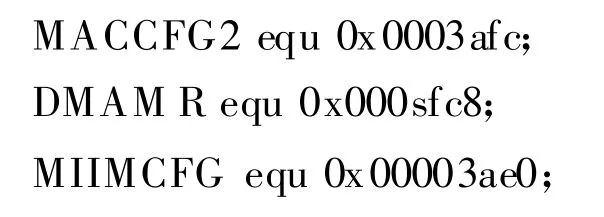

这里我们选择MII模式,传输速度为10M/100M自适应,设计中只需对三个寄存器赋值,

MACCFG2=x0003afc,导入长度设为7,无长度检测,无padding和CRC状态,MAC CRC激活,半双工方模式。

DMAMR=x000sfc8,发送数据的轮流检测频率为512个时钟,乱序缓冲描述轮流检测激活,报警模式优先级设为高级,报警模式的缓冲描述符取来优先级设为中级。MIIMCFG=x00003ae0;MII模式激活,生成导入位初始化,总线时钟被8分频。

经测试网口模块收发数据正常。

5 结语

本文设计的 MSC8122TVT6400最小系统经过实验,表明具备了数据采集、与PC通信及实时数据处理等功能,具有一定的实用价值。此外根据不同的信号处理需求,还可对该最小系统的功能开发验证实验进一步完善:如增加CPCI总线功能及数字信号处理功能等,对于通用I/O(如键盘、液晶)及扩展外存的实现进一步深入研究,可将该最小系统功能升级成为通用DSP系统,从而可更广泛地满足各类复杂工程需求。

[1]Freescale Semiconductor.MSC8122 Data Sheet.Rev.16,12/2008

[2]Freescale Semiconductor.MSC8122 Reference Manual.Rev 3,2005,4

[3]Freescale Semiconductor.MSC8122/26ADS Reference Manual,2005

[4]张雄伟,陈亮,徐光辉.DSP芯片的原理与开发应用[M].北京:电子工业出版社,2003

[5]李朝青.PC机与单片机 &DSP数据通信技术选编[M].北京:北京航空航天大学出版社,2003

[6]赵红怡.DSP技术与应用实例[M].北京:电子工业出版社,2006

[7]范寿康,康广荃,尹磊.Freescale 16位DSP原理与开发技巧[M].北京:机械工业出版社,2006:106~145

[8]Code Warrior Help[Z].Mtorola Inc,2002:106~135