基于FPGA的直序扩频系统的同步设计

张波涛,马艳娥,李剑,胡冠华,邢磊

(中北大学 信息探测与处理技术研究所 太原 030051)

0 引言

扩频通信技术因为具有较强的抗干扰、抗噪声、抗多径衰落能力、较好的保密性、较强的多址能力和高精度测量等优点,在军事抗干扰和个人通信业务中得到了很大的发展。在扩频系统中,对扩频码的同步捕获又是一项关键的技术,近年来受到了广泛的关注和研究[1]。

1 伪随机码捕获

对于常规数字通信,接收端有了相干载波,即可解调出基带数字信号,然而对于扩频信号,首先要完成解扩才能进行解调。接收机若要把伪码扩展的信号解出,接收方就必须能产生一个与发方一样的伪码序列(保证最大相关值),而且该本地伪码速率、相位要与接收到的伪码保持一致[2]。对于约定好的收、发方用同一个伪码很容易办到,但是,如果要从解扩相关器中得到传送的信息,仅仅保证一样的码型是远远不够的,因为即使相同的伪随机码,当相位差大于一个码片时,它们的相关峰就完全消失。所以扩频信号的同步是扩频通信的关键技术,其性能的好坏直接影响到系统。

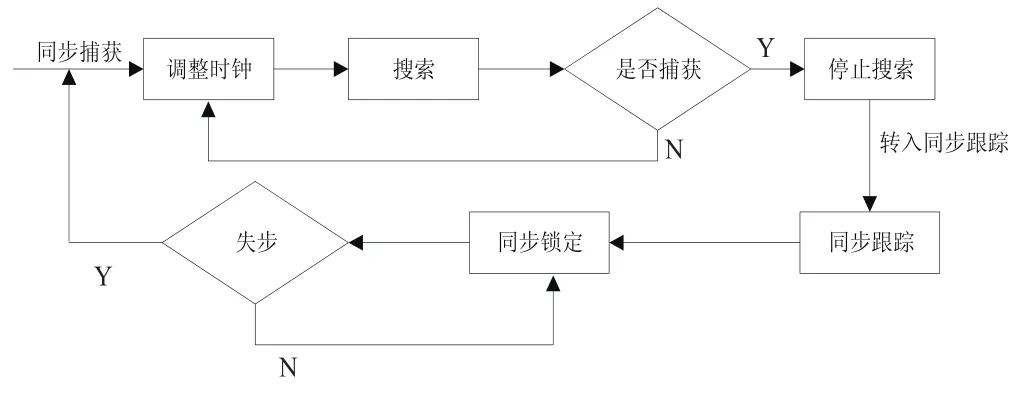

伪随机码同步流程图如图1所示,首先是同步捕获(又称粗同步),主要是捕获伪码。接收机在一开始并不知道对方是否发送了信号,因此需要有一个搜捕过程;其次是同步跟踪(又称精同步),一旦完成捕获后,则进入跟踪过程,即继续保持同步,不因外界影响而失去同步[3]。

图1 伪随机码同步流程图

2 匹配滤波器的基本原理

匹配滤波器是一种无源相关技术,它可以快速地实现相关器的功能。这里的“匹配"是指滤波器的传递函数为所传输信号的复共轭函数。与串行捕获法相比。匹配滤波器捕获的最大优点是捕获时间短,可以快速完成扩频信号的解扩和解调,且数字化容易实现。在理想情况下,数字匹配滤波器(DMF)捕获系统最多只需要一个扩频序列周期的时间,就可检测出同步相位,实现扩频序列的捕获。

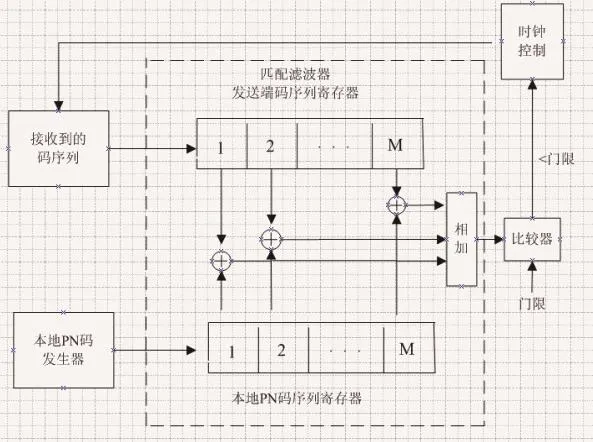

匹配滤波器的基本结构如图2所示。主要由3部分组成:移位寄存器、乘法器和多输入加法器组成,这是一个类似于FIR数字滤波器的结构。

图2 数字匹配滤波器结构示意图

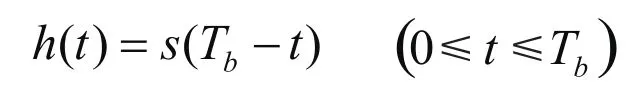

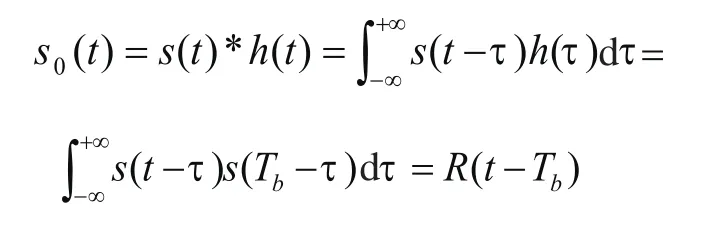

滤波器的输出s0(t)是输入信号s(t)和滤波器冲激响应向h(t)在时间域的卷积积分。在0-TD的时间间隔内,匹配滤波器的冲激响应为输入信号的时间反转,即:

则其输出波形为:

R(t)为输入信号的自相关函数,因此匹配滤波器可以看成是一个相关器,但一般相关器必须经过时间为T的积分,才能得到一个相关值,而匹配滤波器的每个时间点上都能输出一个相关值,因而是一种快速的相关器件[4]。

当处理基带信号时,设输入的伪随机码序列为:

其中ak为周期为N的伪随机码序列的序列值,(n) 为冲激序列。

3 匹配滤波器法的设计与实现

在前面已经提过,扩频通信系统解扩的关键技术是扩频信号的同步,其性能的好坏直接影响到系统的性能和可靠性,码同步的关键又是在PN码捕获方法[5]。

当扩频码周期较长时,采用常规方法就需要较多抽头的FIR滤波器,这样的滤波器实现起来比较困难,而且占用资源较大,其硬件复杂度会随着扩频码的长度成倍增长。因此,将匹配滤波器在FPGA中以一种简单有效的方法来实现是一个关键。基于上面思想,用FPGA来实现的数字匹配滤波器由两组延迟移位寄存器、乘法器、算术累加器和一组系数寄存器构成。

具体的设计思想如下:

第一步设计一个本地相关器,在该相关器中设置一个移位寄存器存放本地PN码,设置另一个移位寄存器用于存放接收的扩频信号,并以每次时钟到来移位一次的方式将新接收到的扩频信号移入。

第二步是进行同步判决,其相关值的计算可通过乘法器运算结果的累加来实现,进而判断是否同步。每步进一个时钟,就通过累加器得到自相关函数的峰值,将此累加结果与门限值相比较,当本地PN码与接收PN码相关匹配时,相关值输出大于门限值,说明捕获成功。

第三步是在捕获到同步信息时启动本地序列生成器,以生成与发端扩频序列同频同相的本地序列,以便进行解扩处理输出原始的数据信号。

在前面的两种串行捕获方法中,相关器在每一个时钟周期只对一位PN码进行相关,并且在一定的时间内将所有相关值相加,捕获过程中本地PN码的相位是变化的。而在匹配滤波器中,每一个时钟周期内都要将N位PN码进行相关,并将相关结果相加,在捕获过程中本地PN码的相位是静止的。

为了使系统能适应更高的速率,也可以分四路同时进行相关值的运算,这样可在适当增加一定硬件复杂度的情况下换取系统更快的捕获速度[6]。

为了防止虚警造成的假同步,通常捕获系统都会增加同步验证电路,即在初次捕获成功后进行一次或多次的同步检验,因此在并行捕获的基础上可以扩展一种双驻留数字匹配滤波捕获方法,该方法是单次驻留数字匹配滤波器的一种扩展使用,它克服了原来快速捕获系统中由于虚警导致系统进入检测阶段后失去对原来接收码元的跟踪的缺陷,提高捕获系统的可靠性,进而缩短捕获时间。

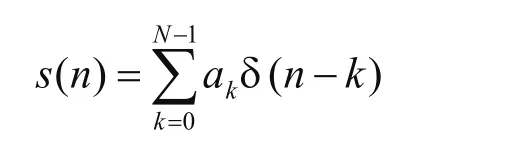

双驻留数字匹配滤波器捕获方案如图3所示。整个捕获过程被分成了两个阶段,第一阶段称为匹配阶段(即第一次驻留),第二阶段称为验证阶段(即第二次驻留),第二次驻留的窗长度是第一次驻留的窗长度的扩展[7]。

图3 双驻留数字匹配滤波器捕获法的原理图

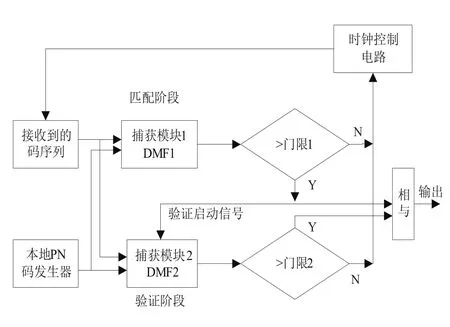

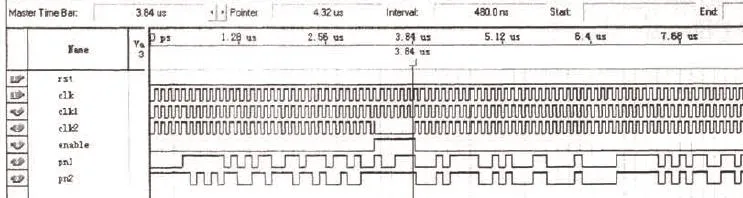

接收到的码序列先流入捕获模块l的数字匹配滤波器DMFl中,当相关值超过了门限值时,它就会触发捕获模块2中的数字匹配滤波器DMF2进行验证;否则重新调整相位进行新一轮捕获。直到两个捕获模块的输出都大于门限,则系统完成对码序列的捕获。因为双驻留数字匹配滤波器也是单次驻留数字匹配滤波器的扩展实现,因此在本论文中仅对单次驻留数字匹配滤波器的伪码捕获进行设计并仿真,仿真结果如图4所示。

图4 伪码捕获仿真图

在仿真图中,clkl是接收序列pnl的时钟,clk2是本地序列pn2的时钟,enable是控制本地序列pn2停止的信号。图中可以看出,当本地PN码与接收信号中的PN相关不匹配时(本仿真实验中相位相差6个码元长度),本地序列pn2在捕获期间相位是静止的,而接收序列pn2在时钟作用下滑过本地PN码,当经过6个时钟周期后,经过匹配相关,相关和大于门限值,即接收PN码与本地PN码相位相同,再启动本地PN码进行同步相位移动,即实现了捕获[8]。

4 结论

本文论述了采用数字匹配滤波器法,在QuartusII软件平台上实现直序扩频系统中伪随机码的同步捕获,仿真结构证明,匹配滤波器法对伪码进行快速捕获是一种行之有效的方法,

[1]何世彪,谭晓衡.扩频技术及其实现[M].北京:电子工业出版社,2007.

[2]占月红,杨红乔,范十明.伪码同步技术研究及其实现[J].电子科技,2008,21(1):42-26.

[3]李涛,孙基国.扩频通信系统中扩频码并/串快速捕获的数字化实现[J].应用科技,2004,31(1):1-4.

[4]张鲲.扩频通信接收与发射[D].济南:山东大学,2006.

[5]Viterbi A J.Spread Spectrum Communications:Myths and realities[J].IEEE Communications Magzine,2002,5:34-41.

[6]Shin Oh-Soon,Lee K B.Differential ly coherentcombining for double—dwell code acquisition DS-CDMAsystems[J].IEEE Trans.Commun,2003,51(7):1046-1050.

[7]金西.VHDL与复杂数字系统设计[M].两安:西安电子科技大学出版社,2003.

[8]朱维勇,栾铭.EDA与数字系统设计[M].北京:机械工业出版社,2004.