TD-LTE系统中数据转存技术的研究及实现*

陈发堂,叶 剑

(重庆邮电大学,重庆 400065)

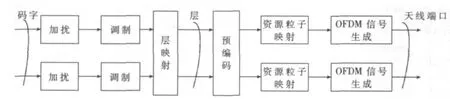

TD-LTE无线终端测试平台以FPGA+DSP+ARM为核心,TD-LTE系统中下行基带OFDM信号生成在FPGA中处理。考虑到FPGA要处理其他算法和逻辑控制,且内部存储器容量有限,所以大容量的基带OFDM信号生成后,需要应用DDR2 SDRAM存储,然后通过射频发送。下行物理信道的一般处理流程如图1所示[1]。

图1所示为下行物理信道的基带信号生成一般流程:首先,将物理信道上传输的每一个码字中的编码比特进行加扰、调制、层映射、预编码后生成复值调制符号,其次将其映射到资源粒子上,最后在每一个天线端口上产生时域OFDM基带信号。

图1 下行物理信道处理一般流程

以前的文献大多以研究DDR2 SDRAM内部指令处理和对接口信号完整性及内部结构进行分析为主,文献[2]主要针对后期流水线视频处理的DDR2 SDRAM控制器的设计,而在TD-LTE系统中DDR2 SDRAM控制器设计及优化的文献资料较少。本文以TD-LTE无线综合测试仪为平台,以研究DDR2 SDRAM控制器的设计为基础,实现DDR2 SDRAM正确转存大容量数据,并验证调试及优化。

1 系统框架

图2 TD-LTE物理层开发平台中FPGA应用框架

在TD-LTE无线终端综合测试仪的基带板设计中,ARM支持的接口比较丰富,主要用于完成操作系统及协议、应用等功能;DSP芯片实现配置功能,完成物理层流程及主要算法,充分发挥其寻址方式灵活、通信机制强大的优点;由FPGA芯片并行处理数据量大、重复性强、速度要求高的数字信号。TDLTE物理层开发平台中FPGA应用框架如图2所示。

根据系统结构中的逻辑任务划分,Turbo译码、同步控制、解预编码、Viterbi译码、OFDM基带信号生成和系统定时等算法都在FPGA中完成,内部运用高级高性能总线(AHB)实现各个模块连接。本文主要研究网络端下行发送链路中DDR2 SDRAM的应用。首先,DSP发送资源映射后的数据,经过多通道缓冲串口(McBSP)发送给FPGA,在FPGA内部,按照TMS320C6455芯片的McBSP协议,利用Verilog HDL语言模拟一个McBSP接口,完成数据接收;然后,调用 IFFT模块生成基带信号,DDR2控制器模块控制基带信号写入DDR2 SDRAM;最后,在控制读出使能信号拉高后,从DDR2 SDRAM中控制读出,传送到RF控制模块,数据经过数/模转换,从射频发送出去,这样就完成了下行OFDM基带信号的发送流程。从射频接收数据,完成解基带信号过程,数据接收过程与发送基带信号类似,只是数据传输方向相反。

2 DDR2 SDRAM控制器的设计

2.1 DDR2 SDRAM特性

DDR2 SDRAM是JEDEC规范的一种新型高速率、大容量的双速率同步随机存储器,在时钟上升沿和下降沿,同时进行数据的传输。DDR2 SDRAM虽然具有高带宽、低功耗和大容量特性,但对于控制器接口设计的时序和延迟提出了更高的要求,使接收端的时序调整和信号完整性分析更加困难。DDR2 SDRAM支持如下特性:

(1)片内匹配终结(On-Die-Termination)。采用ODT技术将许多外部的匹配电阻移到芯片内部,不仅节省了大量的PCB板上面积,而且可以避免信号间的干扰。

(2)突发长度(BL)为 4或 8。突发长度(BL)是指在同一行中相邻的存储单元(列)连续数据传输的数量。DDR2 SDRAM的读/写访问是基于突发的,支持长度为4和8的突发长度。

(3)列地址选通(CAS)时延。DDR2 SDRAM支持 3、4、5的CAS时延(CL)。CL是读指令和输出数据的第一个输出比特之间的时钟延迟。

(4)Bank管理。FPGA芯片内部不同的Bank一般具有不同的电气特性。良好的Bank管理有利于资源的有效利用。

2.2 DDR2 SDRAM接口设计

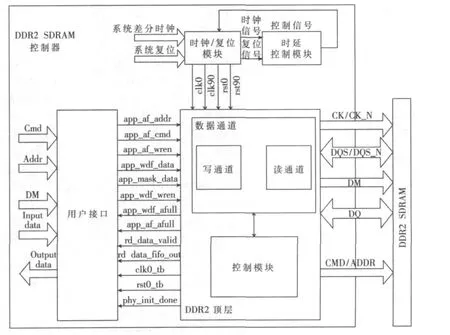

DDR2 SDRAM控制器结构主要包括用户接口、控制模块、数据通道、时钟/复位模块及时延控制模块,其结构如图3所示[3]。

图3 DDR2 SDRAM控制器总体结构

用户接口模块中,主要包括指令逻辑模块、读/写地址FIFO、读/写数据FIFO等模块[5]。其中,对DDR2 SDRAM读/写操作的转换由指令逻辑模块完成。读/写数据FIFO和读/写地址FIFO用来完成数据的缓冲和同步。

控制模块产生DDR2存储接口和用户接口所需的所有控制信号,控制操作由DDR2 SDRAM的内部控制信号完成。控制信号主要包括ddr2_ras_n行地址选择[2]、ddr2_cas_n列地址选择、ddr2_we_n写使能信号等指令。通过各种指令的组合完成相应的指令,控制DDR2 SDRAM在各种状态间跳转,完成相应的读/写操作和其他操作。

数据通道模块主要完成与用户接口及DDR2 SDRAM之间的数据交互。控制模块翻译用户指令,对存储器触发特定的指令。例如,当app_af_cmd信号为000时,翻译为写指令,从用户接口进入的输入数据,通过写通道写入DDR2 SDRAM存储器中。类似地,当app_af_cmd信号为001时,翻译为读指令,DDR2 SDRAM存储的数据依次通过读通道、用户接口的输出数据端口读出。

时钟/复位模块输入的系统时钟是差分时钟,差分时钟通过一个单端输出的缓存器,输出的是相位相差90°的clk0和 clk90,输出的复位信号至少持续 25个时钟[4]。时延控制模块的主要作用是减小温度、电压变化造成时钟/复位信号不稳定的影响。

3 硬件实现及优化

3.1 测试仿真

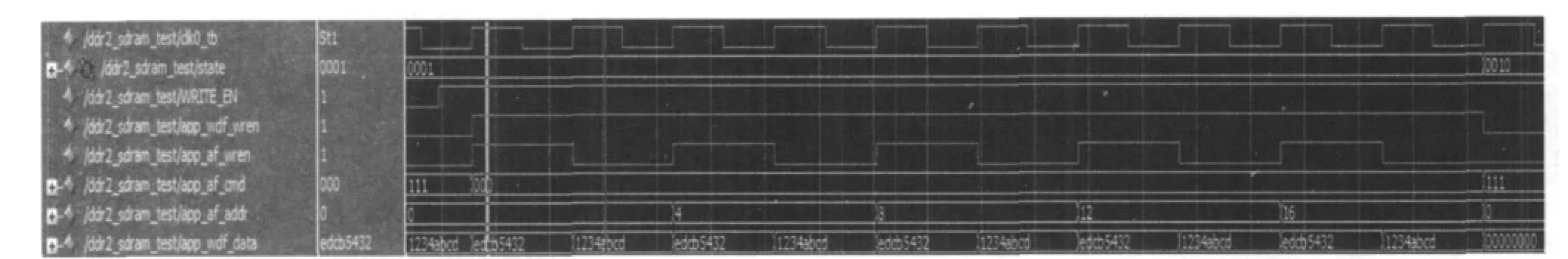

首先,利用 CORE Generator生成设计需要的MIG核,选择好芯片型号,封装和速度等级分别设定为ff136和-2,突发长度为4。在MIG基本应用的基础上开发顶层程序,根据TD-LTE无线综合测试仪下行传输大容量基带信号的设计要求,设计DDR2 SDRAM控制器。对DDR2 SDRAM数据写入仿真波形如图4所示。

图4是在Modelsim SE 6.5中截取的数据写入的仿真图,当state处于0001状态,同时WRITE_EN拉高后,app_af_cmd信号为000,表明可以向DDR2 SDRAM中写入数据,地址信号app_af_addr每次累加4,数据信号app_wdf_data交替发送测试数据 0xedcb5432和0x1234abcd,数据通过FPGA和DDR2 SDRAM之间的双向数据线ddr2_dq写入到DDR2 SDRAM中。

3.2 综合实现

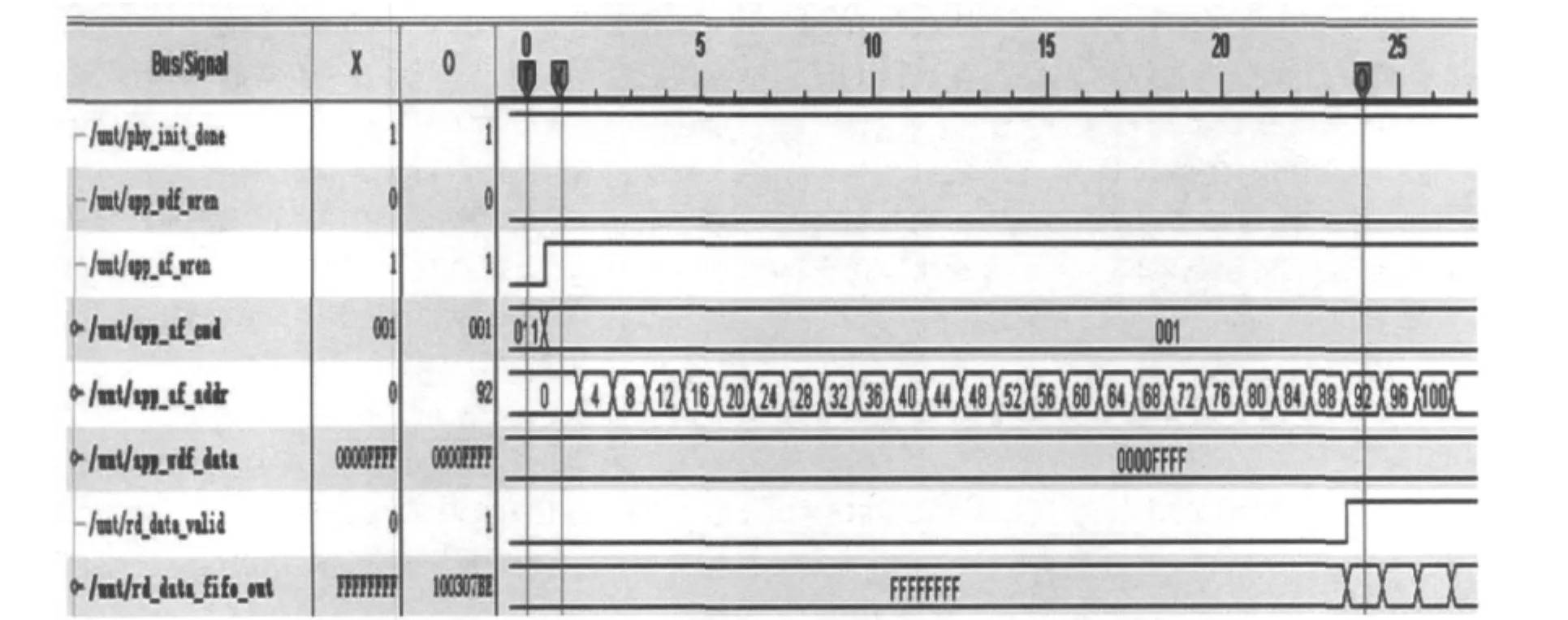

在Modelsim SE 6.5中完成测试仿真,当测试仿真准确无误后,完成综合实现,生成的比特文件下载到FPGA芯片中,进行板级调试与验证。通过在线逻辑分析仪,观测到的DDR2 SDRAM控制器读/写时序如图5、图6所示。

图5是在Chipscope中截取的一段DDR2 SDRAM写操作的时序图。在写使能信号触发的条件下,app_wdf_wren信号拉高,同时app_af_cmd信号为000指示写操作,在app_af_wren的上升沿写入地址,由于BL=4,地址每次累加 4,“X”和“O”竖线分别对应的是第一、二个 32 bit的数据(即 4个16 bit数据),每个地址对应4个16 bit数据。由于选用的DDR2 SDRAM具有2GB的存储空间,每一个TD-LTE下行帧的IFFT数据存储完就发送一次,数据量小于2GB,不用考虑会溢出的情况。

图6是在Chipscope中截取的一段DDR2 SDRAM读操作的时序图。在读使能信号触发的条件下,app_af_wren信号拉高,同时app_af_cmd信号为001指示读操作,每一个时钟沿写入一个读地址,每次地址累加4,在一段时延后,rd_data_valid信号拉高,指示有效数据输出,rd_data_fifo_out输出端口上依次输出对应地址的数据。“O”竖线处的数据对应的就是“X”竖线处地址的第一个32 bit数据,也就是图5中写入的第一个数据。

图4 DDR2 SDRAM数据写入仿真波形

图5 DDR2 SDRAM数据写入时序图(BL=4)

图6 DDR2 SDRAM数据读出时序图(BL=4)

3.3 设计优化

针对DDR2 SDRAM控制器验证调试时出现的异常/错误现象进行优化和改进:

(1)时钟触发不稳定。TD-LTE系统设计中,内部模块较多,由DSP提供一个100 MHz时钟作为多个模块的时钟,造成时钟触发不稳定,影响数据采样的稳定。

优化方案:在时钟触发不稳定的模块前,增加一个数字时钟管理模块(DCM),达到稳定时钟、精确数据采样的目的。

(2)不同时钟域之间数据传输。由于IFFT模块也在FPGA中完成,而IFFT模块的输出时钟和DDR2 SDRAM控制器输入时钟频率相位不同,造成数据采样的错误。

优化方案:在IFFT模块和DDR2 SDRAM控制器模块之间增加一个异步FIFO模块,这样OFDM基带信号就能正确写入到DDR2 SDRAM中。

(3)抖动现象。由于实际板子的影响,按下硬件信号复位时,发生了明显的抖动现象。

优化方案:在代码编写过程中,增加了去抖动程序,使代码更加优化。例如高电平复位时,将复位信号扩展为10个全为1的比特(10’h3ff)进行判断。

4 性能分析与结论

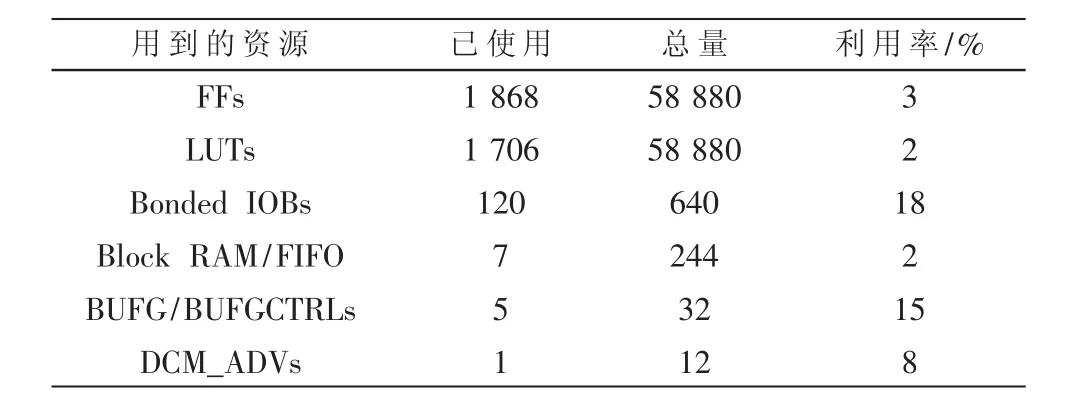

DDR2 SDRAM设计使用Xilinx公司的高性能软件ISE10.1[6],选择芯片为Xilinx公司Virtex-5系列的XC5SX95T(speed-2),DDR2 SDRAM的型号为MT47H128M16,2GB存储空间。综合实现时,利用Synplify Pro 9.6.1进行逻辑优化后,运行的最大时钟频率为281.021 MHz,按照本文的设计实现方法,资源占用量得到很大程度的减少,因而资源占用情况已比较合理,详细资源利用情况如表1所示。

表1 DDR2 SDRAM控制器资源利用情况

从基带板调试验证的结果看,大容量的OFDM基带信号存储到DDR2 SDRAM中,不仅节省了芯片内部的RAM存储空间,而且大大提高了数据处理速度和精度。读/写操作的实现是由DDR2 SDRAM控制器内部控制的,从写入数据和读出数据的一致性看,DDR2 SDRAM控制器的设计满足要求,为下一步数据的正确处理提供了可靠保证。该设计实例提供了仿真及实现具体流程,对于大容量高速高性能系统开发具有良好的参考和应用价值。

[1]3GPP TS 36.211 v9.0.0:Physical Channnels and Modulation(Release 9).2009(12).

[2]Wang Xuzhi,Ma Yanru.Design of DDR2 SDRAM Controller for Video Post Processing Pipeline[C].2009(12).

[3]Chen Shuangyan,Wang Donghui.An Innovative Design of the DDR/DDR2 SDRAM Compatible Controller[C].2005(10).

[4]Xilinx Memory Interface Generator(MIG)User Guide[M].UG086(v2.1).2008(9).

[5]须文波,胡丹.DDR2 SDRAM控制器的 FPGA实现[J].江南大学学报,2006(4).

[6]胡彬.Xilinx ISE Design Suite 10.x FPGA开发指南-逻辑设计篇[M].北京:人民邮电出版社,2008.