频率合成器中延时线锁频环的实现与应用

夏莹周勃

(1.常州信息职业技术学院江苏常州2131642.上海航天电子技术研究所上海201109)

频率合成器中延时线锁频环的实现与应用

夏莹1周勃2

(1.常州信息职业技术学院江苏常州2131642.上海航天电子技术研究所上海201109)

详细论述了延时线锁频环在频率合成器中的功能和应用,对锁相锁频环的传递函数和相位噪声单边带功率谱密度进行分析,并给出仿真设计。仿真结果表明,将延时线锁频环用于频率合成器中,能明显改善中远端的相位噪声。

频率合成器;延时线锁频环;相位噪声

0 引言

频率源的好坏直接影响微波系统的性能,是决定电子系统功能的关键设备。在频率合成器中,可根据环路的相位噪声数学模型来计算基底噪声,并参考压控振荡器(VCO)性能,获得最佳相位噪声。VCO的良好噪声特性将有利于改善频率合成器中远端的相位噪声。当VCO的性能确定后,可以将锁频环(FLL)与锁相环(PLL)结合使用构成锁相锁频环,实现对VCO相位噪声的优化。目前关于FLL改善PLL性能方面的研究大多只是从锁频环角度进行分析,得出FLL能改善VCO相位噪声的结论。本文将锁相环与锁频环结合,得出环路传递函数和相位噪声单边带功率谱密度,并给出了电路仿真,仿真结果表明,锁频环能明显改善频率合成器的中远端相位噪声。

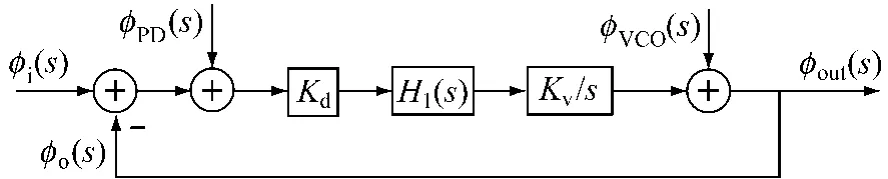

1 锁相锁频环原理

由锁相环理论可知,PLL输出的相位噪声特性与参考输入和环路的相位噪声有密切的关系。图1所示为PLL相位模型,Φi(s)为环路输入参考源的相位,Φo(s)为环路输出相位,ΦPD(s)为鉴相器噪声,ΦVCO(s)为压控振荡器(VCO)的相位噪声,Kd为鉴相器的鉴相灵敏度,H1(s)为环路滤波器传输函数,KV/s为VCO的积分特性[1]。

图1 PLL相位模型

图1的环路传递函数为

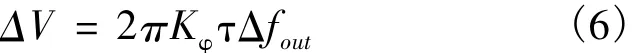

根据锁相环路传递函数的低通特性,有

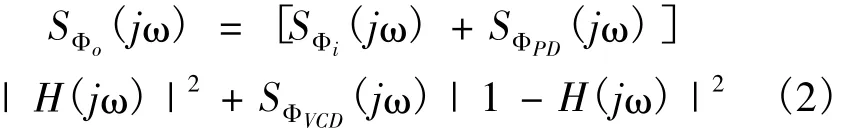

ω1为PLL环路带宽。从上式可以看出,锁相环对于输入参考源和鉴相器相当于“低通”滤波器,对于VCO相当于“高通”滤波器。如图2所示为PLL在锁定情况下的渐近相位噪声特性曲线[2]。

图2 PLL的渐近相位噪声曲线

当VCO的性能确定后,必须对VCO相位噪声进行优化,降低系统的相位噪声。可以将锁频环与锁相环结合使用构成锁相锁频环,实现对VCO相位噪声的优化。

锁频环主要由延迟线、移相器、混频式鉴相器和环路滤波器(LPF)组成,是一种高灵敏、低相噪的宽带鉴频器,如图3所示为锁相锁频环框图[3]。图3中,fi为输入参考频率,fout为环路输出频率,τd为延时线的延时时间。

当使用这种环路时,整个环路的带宽将降低到与环路噪声底部和更干净的VCO噪声新的交叉频率处。FLL带宽确定低于FLL带宽频率偏离的噪声底部。为了得到更低的噪声底部,可以进一步展宽带宽。但由于相位和增益余量问题,锁频环路带宽也不能太宽,因为可能会产生超出带宽点的相位噪声峰化。1 MHz左右的FLL带宽可以提供合适的噪声底部,并能避免超出带宽频率的噪声峰化[2]。

图3 锁相锁频环框图

延时线作为频率—相位变换器,使FLL实际成为一种鉴相器。为保证混频式鉴相器具有单调特性和宽频带工作,移相器必须提供这样的相移,保证混频器的两个输入相位差接近90°[4]。设φ为额定相移,得

VCO瞬时频率的变化将引起相位起伏,有

混频器的输出电压ΔV与源的频率偏差Δf,及相位检测器的常数Kφ成比例,且和fmτd之间具有周期性,即sin(x)/x的关系,fm为鉴相频率。当f≪1/2 πτd时,sin(πfτd)/(πfτd)≈1,可得

此时,混频式鉴相器可视为线性工作,ΔV将正比于Δφ。由式(6)可得FLL的数学模型,如图4所示[3]。

图4 FLL的数学模型

研究FLL输出的相位噪声,必须考虑VCO的相位噪声。设VCO的调谐灵敏度为KV,LPF为低通滤波器,传递函数为H2(s),可以得到FLL线性相位模型,如图5所示,其中Φm(s)为鉴相器噪声。

图5 FLL相位模型

因此,图3对应的锁相锁频环相位模型如图6所示。

图6 锁相锁频环相位模型

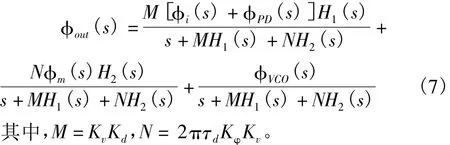

由图(6)可得环路的传递函数为

设ω2为FLL的环路带宽,由前述,FLL带宽为1 MHz左右较合适,远大于ω1,则式(7)对应的相位噪声单边带功率谱密度可近似为

从式(8)可以看出,环路输出的近端噪声依然主要由输入参考源和鉴相器相位噪声决定,远端取决于VCO的相位噪声,FLL环路主要改善了频率合成器的中远端相位噪声,Kφ和τd越大,锁频环的效果越好。

2 仿真设计

使用Agilent公司的Advanced Design System (ADS)进行仿真设计。频率合成器输出频率为1 GHz,环路分频比为100,VCO的相位噪声由ADS的相位噪声模块产生,参考频率为10 MHz,参考源的相位噪声特性如表1所示。

表1 参考源相位噪声特性

如前所述,FLL混频器的两个输入相位差应接近90°,为了不失一般性,同时为了验证τd越大锁频环的效果越好,将τd分别设定为10.2 ns和75.1 ns。调整移相器的相移,使混频器的两个输入信号正交,此时移相器相移分别为18°和54°,FLL环路滤波器带宽为1 MHz,锁相锁频环路仿真原理图如图7。

图7 锁相锁频环路仿真原理图

图8所示为PLL与不同τd时锁相锁频环输出相位噪声。从图8中可以看出,同PLL相比,锁相锁频环的中远端输出相位噪声得到改善;τd越大,相位噪声改善越明显,τd为75.1 ns时,相位噪声改善约19 dB。

图8 PLL与不同τd锁相锁频环闭合环路输出相位噪声

通过理论分析和仿真设计,延时线锁频环用于单环频率合成器中,可以明显改善频率合成器的中远端相位噪声,并且延时时间越长,效果越好。

[1]弋稳.雷达接收机技术[M].北京:电子工业出版社,2005:145-148.

[2]白居宪.低噪声频率合成器[M].西安:西安交通大学出版社,2003:205-208.

[3]马俊,方立军.现代频率合成中的锁频环实验研究[J].雷达科学与技术,2006(6):373-376.

[4]方立军,马俊,王元庆.现代频率合成中的分数分频与锁频环[J].现代雷达,2002(3):71-72.

Realization and Application of Delay Line Frequencylocked Loop in the Frequency Synthesizer

XIA Ying1ZHOU Bo2

(1.Changzhou College of Information Technology,Changzhou 213164 2.Shanghai Aerospace Electronic Technology Institute,Shanghai 201109,China)

The paper discusses the function and application of delay line frequency-locked loop in the frequency synthesizer in detail; analyzes the transfer function and the phase noise single sideband power spectral density of the loop in depth;and gives the simulation.The simulation results show that by using the delay line frequency-locked loop,it can improve the middle and far end phase noise in the single loop frequency synthesizer.

frequency synthesizer;delay line frequency-locked loop;phase noise

TN 74

A

1672-2434(2011)02-0017-03

2010-11-05

夏莹(1981-),女,讲师,从事研究方向:电子技术