一种高性能低电压全摆幅CMOS运放设计

潘学文

(湖南科技学院 计算机与通信工程系,湖南 永州 425100)

一种高性能低电压全摆幅CMOS运放设计

潘学文

(湖南科技学院 计算机与通信工程系,湖南 永州 425100)

采用CMOS 0.5μm 工艺设计了一种低电压全摆幅CMOS运算放大器,提出了一种新颖简单的电平偏移电路,为运放的输入级提供了良好的电平位移,当电源电压降至或者小于N 型与P 型管阈值电压之和时,也能使的运放在任何共模输入电压下可以正常工作,实现了输入级的Rail-to-Rail特性和恒跨导。采用Hspice软件仿真,在1.3v单电源供电下,直流开环增益达106.5dB,相位裕度为72°,功耗178.8μW。整个电路结构简单紧凑.适合于低电压应用。

CMOS;Rail-to-Rail;运放;电平偏移

0 引言

近年来,随着CMOS工艺的发展,器件的特征尺寸的减小,集成电路的集成度提高, 使得集成电路向着低压低功耗的方向发展[1]。为了适应低压低功耗的发展趋势,低电压、高功效、高性能的模拟电路单元的设计成为人们关注的焦点。而运算放大器作为模拟电路的最主要的组成单元,也受到越来越多的重视。电源电压的降低对运算放大器的最大影响就是输入和输出信号的动态幅度大大减小[2,3]。为了增加其输入、输出电压范围和信噪比,迫切需要设计具有rail-to-rail输入、输出能力的运算放大器。

对于运算放大器的设计而言, 传统的rail-to-rail 运放的实现主要是依靠互补的PMO S 和NMO S 的差分对来实现共模电压从0V 到电源电压的工作范围, 满足其工作条件的电源电压最小为(即N 型与P 型管的阈值电压和与负载进入饱和区电压之和). 当电源电压进一步降低时, 由于阈值电压和进入饱和区的电压都不会随着电源电压等比例降低, 这样P 型差分输入对和N型差分输入对的工作范围将无法重合, 从而导致在从的范围内运放不能正常工作[4-6]。此时,如果不提高工艺成本采用低阈值电压的输入差分对就必须对现有的电路形式进行改进。本文针对低电源电压运算放大器设计问题,,提出了一种新颖简单的电平偏移电路[7][8],当电源电压降至或者小于 Vsump,in时,也能使的运放在任何共模输入电压下可以正常工作,实现良好的性能。

1 电平偏移电路原理分析

运算放大器的输入级是运放的重要组成部分,其主要作用是放大输入的差分信号,同时有效抑制共模信号。共模输入范围是运放输入级的一个重要参数。当在输入共模电压范围内时,即使输入很小的差分信号,输入级都能正常工作。因此,在设计运放输入级时应使共模输入电压保持在共模输入范围内。此外,运放的其它重要性能参数如输入相关噪声、失调和共模抑制比等也都是由输入级决定的。

本文设计的电平偏移电路有电流偏移产生器

(Level-shift current Generator)和适配器(Adaptor)组成,其原理图如图一所示。在适配器中,P 型差分输入对和N 型差分输入对的输入端(和) 通过电阻连接到运放的输入端(iV+和iV−),N 型差分输入对的输入端在上端,P 型差分输入对的输入端在下端。电流偏移电路产生非线性电流(图1右侧),并通过电流镜电路复制到适配器,其在中间电压区域达到最大,而在接近0V 和电源电压时很小。因此,在电阻上的压降,即产生的电平偏移电平,在中间电压区域达到最大,而在接近0V 和电源电压时很小。对于运放的输入共模电压而言,电平偏移降低了N 型差分输入对的开启电压和提高了P 型差分输入对的截止电压。因此,当电源电压降低至甚至小于 Vsump,in时,合理的设置电流I和电阻R的大小,就能使得运放在任何共模输入电压能正常工作。

式中 Vi|cm为运放输入共模电压,Vi,n|cm和 Vi,p|cm分别为P 型差分输入对和N 型差分输入对的共模电压。

2 电路结构分析

本文所设计的总体电路如图2 所示,由电平偏移电路,输入级,中间放大级和输出级组成。 MS1-MS12、M7-M12和四个电阻R构成了电平偏移电路,其中MS1,MS2,MS3,MS4组成互补的PMO S 和NMO S 的差分对,其输入端接至运放的输入端,MS6作为P型差分对的电流源,其产生的电流为bpI ,通过MS5镜射至MS6,MS5作为为N型差分对的电流源,其产生的电流bnI ,通过MS7,MS8,MS9镜射至MS10,IB为一恒电流源。BI与6MSI 、10MSI 相加减得到非线性电流I。其中

图1 电平偏移电路原理图

图2 运放总体电路图

电流I经M7-M12组成的电流镜电路复制到输入级差分对输入端,流经电阻R产生压减,得到电平偏移。本文中IB=10μA,R=40K,采用CMOS 0.5μm 的工艺,其 Vthp为-0.95V, Vthn为0.73V,电源电压为1.3V。由公式(1)、(2)可知,对于运放的输入共模电压而言,N 型差分输入对的开启电压降至0.33V,P 型差分输入对的截止电压提高至0.55V,由此可知,运放可在任何共模输入电压下正常工作。

输人级由M1-M6管组成,工作在三个区域:当共模输人电压向0V方向变化时,PMOS差分对工作,输人跨导为当共模输人电压为电源中间值时,两对差分对都工作,输人跨导为当共模输人电压向电源电压方向变化时,NMOS差分对工作,输入跨导为,其中,分别是空穴和电了在沟道表面的迁移率, Cox是MOS管栅氧化层单位面积电容。设置合理的参数,使得 βn=βp且之和为常数,就能保证输入级的跨导基本保持恒定。

中间级采用适合低电压工作的低压宽摆幅共源共栅结构。折叠式共源共栅中间放大级构成加法电路,从差分对输出的电流进入此加法电路后,通过由M19、M20组成的电流镜实现双端到单端的转换,输出给下一级电路,输出级则采用较为传统的Class A类来得到轨至轨的输出,C1和C2为补充电容。

2 运放的仿真结果

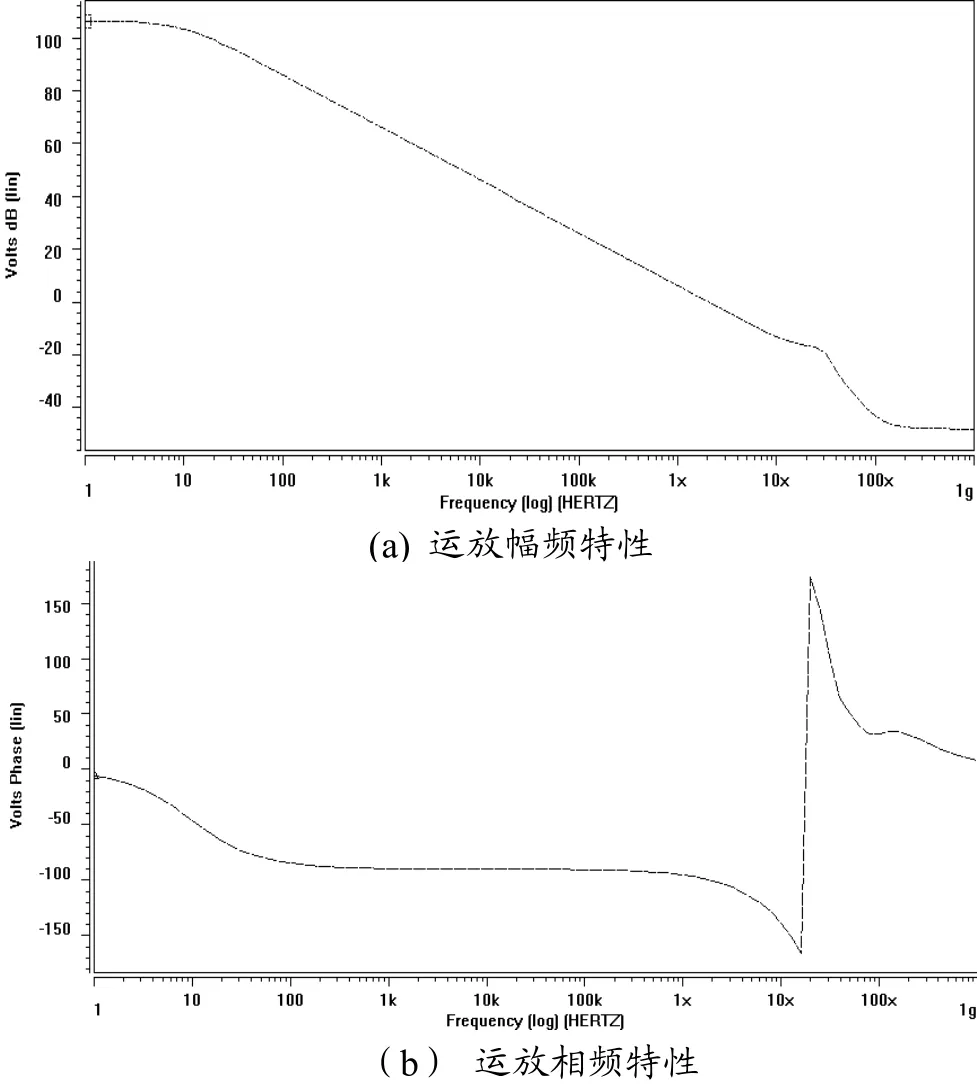

运用Hspice 仿真工具,采用CMOS 0. 5μm工艺以及Level49 的参数模型,对运算放大器进行了模拟仿真,得出了各种性能结果。将放大器接成开环结构,测量其频率响应,结果如图3所示。从图3中可以看出,其低频增益达到了

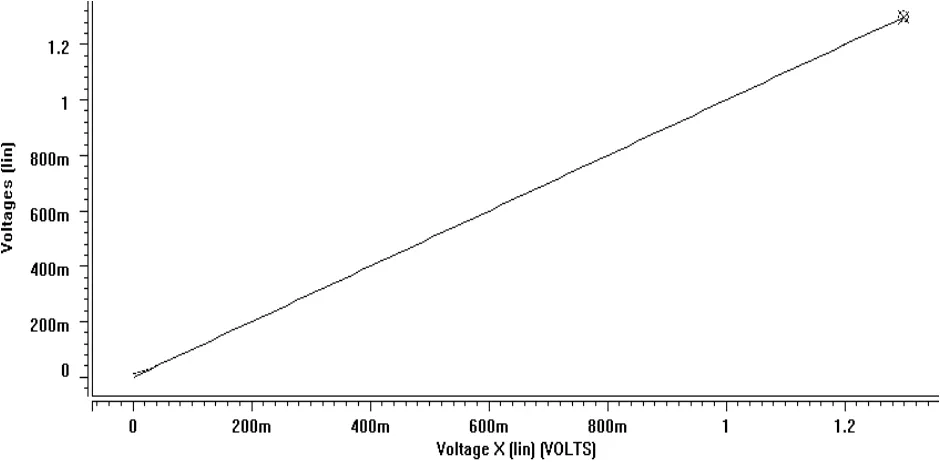

106.5 dB,相位裕度为72°,单位增益带宽为2.3MHz。将放大器接成电压跟随器的形式,测量其单位增益响应,结果如图4所示。从图4中可以看出,放大器的输入输出达到了整个工作电压范围。

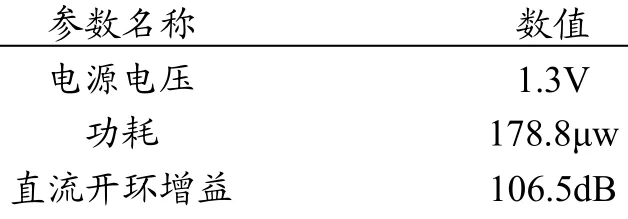

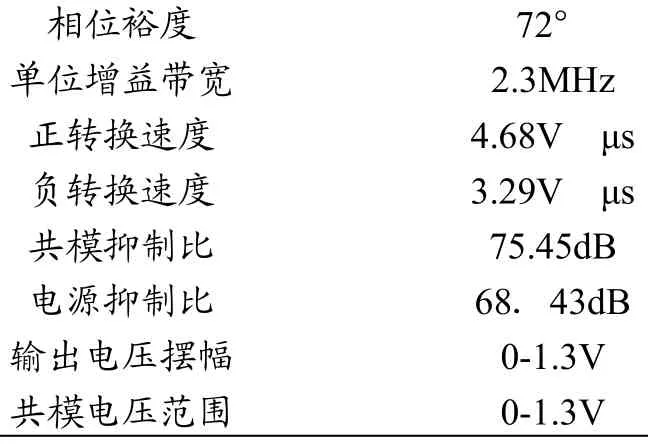

表1列出了具体性能参数。采用1.3V单电源供电,其功耗仅为178.8μw。

图3 运放的频率响应

图 4 运放单位增益响应

表1 性能参数

相位裕度 72°单位增益带宽 2.3MHz正转换速度 4.68V∕μs负转换速度 3.29V∕μs共模抑制比 75.45dB电源抑制比 68.43dB输出电压摆幅 0-1.3V共模电压范围 0-1.3V

3 结论

本文设计了一种新颖简单的电平位移电路,结构简单,易于实现,解决了阈值电压对电源电压和输入信号的受限问题,使得运放在任何共模输入电压能正常工作,并能保持输入级的跨导为常数,从而运算放大器电路的电路特性不随共模输入电压的变化而发生改变;中间级采用适合低电压工作的低压宽摆幅共源共栅结构;输出级采用传统的Class A类来得到轨至轨的输出。从仿真结果来看,运放具有很好的性能指标,可以适应低电压低场合的需要。

[1]毕查德·拉扎维著.模拟CMOS集成电路设计(陈贵灿等译)[M].西安:西安交通大学出版社,2003.

[2Huijsing J H,Member S,Langer K J.Low-Power Low-Voltage VLSI Operational Amplifier Cells[J].IEEE Transactions on Circuits and Systems,1995,42(11):841-850.

[3Langer K J,Huijsing J H.Low-voltage power-efficient operational amplifier design techniques-an overview[J].CICC Custom Integrated Circuits Conference[C].San Jose:IEEE,2003,677-684.

[4]林越,徐栋麟,任俊彦等.基于共模电平偏移电路新型CMOS低电压满幅度运放设计[J].半导体学报,2002,23(5):529-535.

[5]何红松.CMOS两级运算放大器设计与 HSPICE仿真[J].湖南科技学院学报,2007,28(12):28-30.

[6]Yukizaki Y,Kobayashi H,Myono T. Low-voltage rail-to-rail CMOS operational amplifier design[J].Trans. Inst. Electron.Inf. Commun. Eng[C].2006,89(6):402-408.

[7]Hwang C,Motamed A,Ismail M. Universal constant-gm input-satge architectures for low-voltage op amps[J].Circuits and Systems I:Fundamental Theory and Applicatios,IEEE Transactions on,1995,42(11):886-895.

[8]Duque-Carrillo J F,Ausin J L,Torelli G,et al. 1-V rail-to-rail operational amplifiers in standard CMOS technology[J].IEEE journal of Solid-State Circuits,2000,35(1):33-44.

TN402

A

1673-2219(2011)08-0029-03

2011-04-10

湖南科技学院校级课题研究项目(项目编号:09XKYTC014)。

潘学文(1983-),男,硕士,助教,研究方向:集成电路设计与仿真。

(责任编校:刘志壮)