高速采集系统的时钟端接设计与仿真*

白红蕊,马秀荣,白 媛,吴 健

(天津理工大学计算机与通信工程学院,通信器件教育部工程研究中心,天津 300384)

目前对高速采集系统的要求越来越高,紧耦合的LVPECL(Low-voltage Positive Referenced Emitter Coupled Logic)差分时钟能够更好地抑制其他动态网络的干扰,从而使其布线方式成为高速时钟信号的主要互连结构[1]。然而若不对差分时钟信号进行恰当的端接设计,时钟信号将会感受到阻抗突变,产生的反射噪声会导致时钟信号频率不稳定,采集的数据不准确[2-3]。因此合理的LVPECL 差分信号端接方法设计是确保高速采集系统可靠性的重要工作之一。

对于LVPECL 差分时钟信号的端接设计,国内外学者进行了大量的研究。文献[4]研究了单端PECL/ECL 典型的端接设计方法,但没有考虑交流耦合和差分PECL/ECL 信号的情况;文献[5-6]中研究了LVPECL 差分驱动直流、交流耦合的端接设计方法,但该方法只考虑差分信号阻抗匹配,而未考虑单端阻抗匹配,导致单端信号反射引起振铃现象,破坏差分时钟和其它信号的特性。在深入分析上述方法的优劣基础上,提出了一种改进的LVPECL 差分时钟信号端接设计,有效地抑制单端信号的反射噪声,为高速采集系统差分时钟的互连设计提供了一种新思路。

1 基于AD9254 的高速数据采集系统

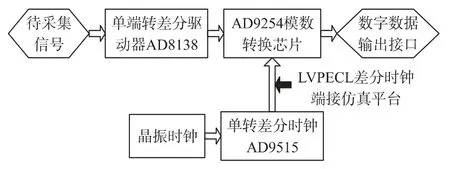

文中以基于AD9254 数据采集系统为仿真平台,在Cadence 环境下,分别对常用的交流耦合端接和改进的LVPECL 差分信号端接设计进行了仿真实验。基于AD9254 高速数据采集系统整体结构框图,如图1所示。一路待采集的信号通过差分放大模块后传送到模数转换芯片作为采样数据,另一路为温控晶振产生的时钟信号通过可编译调整的差分时钟模块后传送到模数转换芯片作为采样时钟。

图1 AD 高速数据采集系统整体结构框图

数模转换芯片采用美国AD 公司推出AD9254 150 Msample/s(每秒百万次采样)转换速率14 bit分辨率的模数转换器。时钟分配芯片采用1.6 GHz两输出,频率和延时可调的AD9515。时钟端接设计对应与框图中AD9515 驱动端和AD9254 接收端之间。只有合理的端接才能确保时钟信号的完整性。因此,下面对端接设计进行理论分析。

2 高速采集系统时钟端接设计分析

2.1 常用的交流耦合端接方法

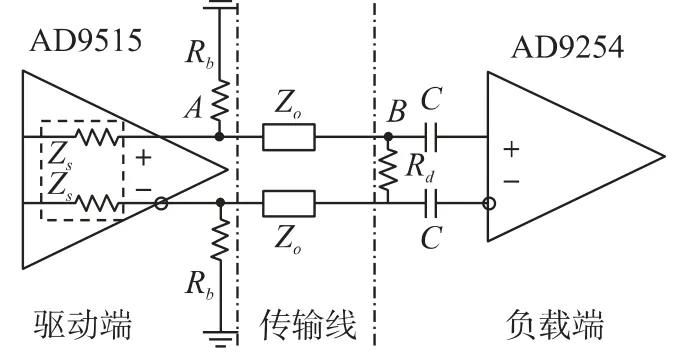

LVPECL 常用的交流耦合端接设计方法如图2所示。整个端接方法由驱动端、传输线和负载端3 部分组成。

图2 常用的交流耦合端接方法

驱动端部分的Zs为其单端等效输出阻抗,Rb为单端直流偏置电阻,它的作用是为LVPECL 单端信号的静态电平提供电流回路,满足标准负载电流IL的要求。已知LVPECL 信号输出正、负端的静态电平典型值均为VCC-1.3V(VCC为器件的电源电压),IL为14 mA。LVPECL 信号输出电压幅度为VLVPECL。故Rb一般近似采用:

传输线部分的Z0为传输线的特征阻抗。

负载端的C为隔直电容,Rd为差分端接负载,它的作用是对LVPECL 差分信号进行阻抗匹配,抑制差分信号的反射。Rd应为:

Rdiff为差分阻抗。

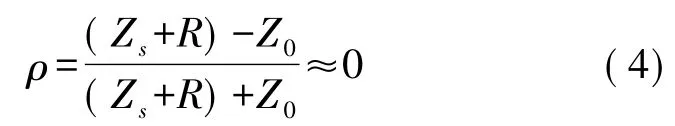

由图2 的分析可知,当输出阻抗Zs和传输线阻抗Z0不匹配时,反射系数ρ[7]可表示为:

故信号在图2 中点A 处感受到阻抗突变,从而在端接中引起了反射噪声,出现了振铃现象。

当反射噪声转化为差模噪声时就会破坏时钟信号的差分特性。虽然信号在图2 中点B 端接了差分阻抗,抑制差分信号的反射,但由于点A 处引起的反射噪声已经破坏信号的差分特性,故交流耦合端接方法中接收的差分信号并不能完全消除在点A处引起的反射噪声。

可见,常用的差分交流耦合端接方法只进行了差分输出阻抗匹配,而没有进行单端输出阻抗匹配,从而引起的LVPECL 单端反射噪声破坏了差分信号的差分特性。

2.2 改进的LVPECL 差分时钟信号端接方法

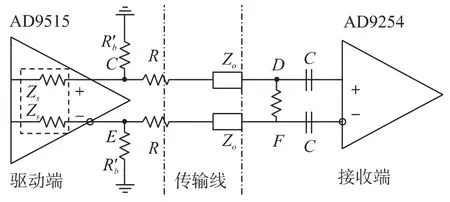

本文提出一种改进的LVPECL 差分时钟信号端接方法,将单端匹配设计引入到端接设计中,从而改善单端反射噪声的抑制效果。改进的LVPECL 差分时钟信号端接方法如图3所示。

图3 改进的LVPECL 差分时钟信号端接方法

与常用的差分交流耦合端接方法相比,图3 驱动端引入了串联阻抗匹配电阻R,它的作用是保证LVPECL 单端信号的Zs和R 的串联与Z0相匹配,使反射系数ρ 近似为0,消除反射噪声。当R=ZOZS时,

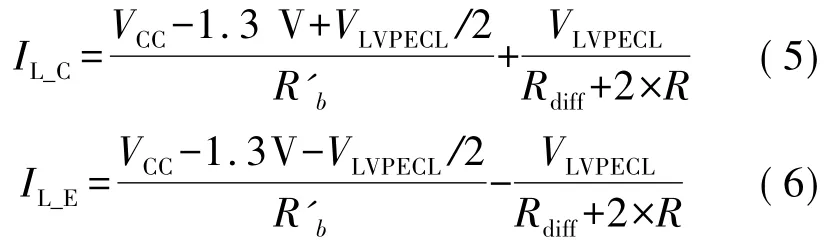

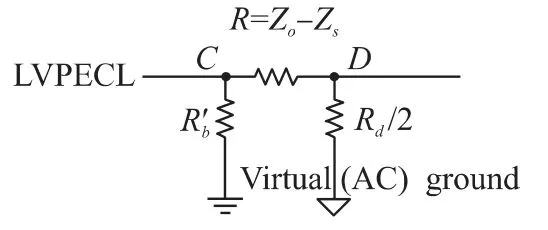

R′b为直流偏置电阻。因为R 的引入,使得R′b与图2 中Rb不同。已知C、E点输出的是差分时钟信号,假定某一时刻C点电压为相对高,IL_C、IL_E分别为流过C、E点的负载电流,根据电路结构可知:

根据上述公式可知IL_C>IL_E,为了确保电流最大时仍满足IL负载电流要求,因此R′b应为

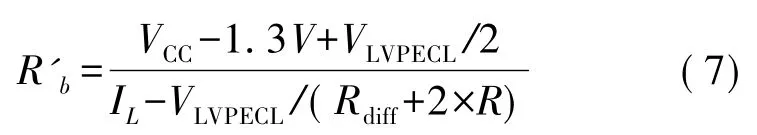

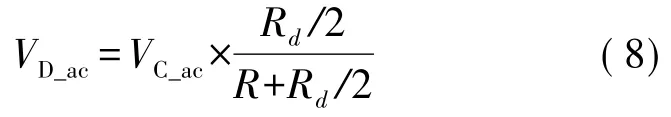

除此之外,R 的引入也使得端接设计构成一个电阻衰减网络,如图4所示。

图4 电阻衰减网络

LVPECL 差分时钟信号经过电阻衰减网络,和为图4 中C、D 的交流电压。则有

因此在设计端接方法的时候,R、R′b参数的选择不仅要考虑满足抑制反射的要求,同时要折中考虑VD_ac满足常用负载端输入高、低电平的范围要求,一般输入时钟信号高低电平的要求为0~0.8 V为低电平,1.2-VCC为高电平。

3 仿真参数确定和仿真平台搭建

3.1 仿真参数确定

AD9515 差分时钟信号配置为LVPECL 差分信号输出,传输线为差分微带线。

根据AD9254、AD9515 的封装,确定线宽W=10 mil;介质高度H=6 mil;覆铜厚度T=1.35 mil;介电常数Er=4.2;差分线宽S=6 mil。通过微带线特性和Polar_si9000 传输线场分析器求解[8-9],计算得出:Z0=51.01Ω;Zdiff=87Ω。

根据AD9515 IBIS模型可知其输出阻抗ZS≈8Ω,选取R≈40Ω,Rdiff≈100Ω,Rb=240Ω,R′b=200Ω。由以上参量可以确定≈0.555×VLVPECL,满足接收端输入差分时钟信号要求。通过负载端接收的差分信号过冲来衡量系统抑制反射噪声的能力。

3.2 仿真平台搭建

在Cadence SI 软件中建立图2、图3所示的拓扑结构。

首先,将验证后的IBIS(Input/Output Buffer Information Specification)仿真模型加载到Cadence SI仿真软件中。IBIS模型[10-11]是一种行为模型,通过V/I和V/T 曲线描述器件管脚的输入、输出的电气特性,而不涉及器件内部电路的组成。IBIS模型常用于板级信号完整性分析,通过仿真观察不同器件间传输线路中的信号完整性问题。

其次,根据图2、图3所示端接方法建立相应的拓扑结构。且由于芯片封装与基本元器件焊接需要一定的空间间隙,故在驱动端输出信号处和接收端接收信号处分别加入100 mil 的差分微带线。

然后,设置结构中的激励源采用100 MHz 时钟信号。差分微带线的参数按照§4.1 中的参数定义,其它器件参数根据图2、图3 中的参数确定。

4 仿真结果与分析

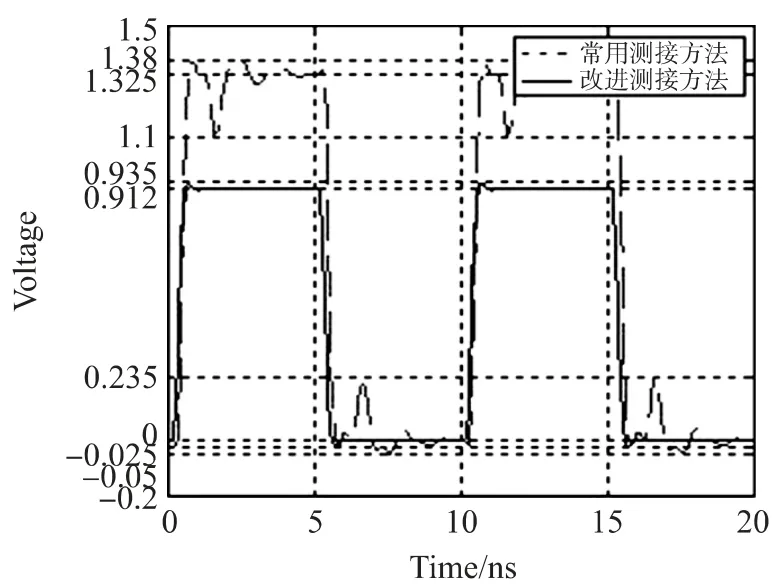

时钟信号频率为100 MHz、传输距离为200 mil时两种端接方法仿真结果如图5、图6、图7和表1所示,鉴于电压过冲量是衡量反射噪声的重要指标[12],用过冲做反射噪声抑制的衡量指标。

图5 常用的交流耦合端接的仿真结果

图6 改进的LVPECL 差分时钟信号端接方法

图7 接收的两路差分时钟信号差分后的信号

4.1 改进的端接方法对反射噪声的抑制仿真

图5、图6 中虚线DESIGN DOUTP22i和23i为驱动端AD9515 输出的两路差分时钟信号,点划线DESIGN DOUTP23i_DOUTP22i_diff为两路差分时钟信号差分后的信号;带星号的虚线DESIGN INP38i和39i为AD9254 负载端接收的两路差分时钟信号,两路差分后的信号如图7所示。图7 中实线为常用的交流耦合端接设计的仿真结果,虚线为改进的LVPECL 差分端接的仿真结果。相应的最大电压过冲见图中标注。

图5、图7 表明常用的交流耦合端接中驱动端输出的两路差分时钟信号差分后的信号(图5 中点划线DESIGN DOUTP23i_DOUTP22i_diff)和负载端接收的两路差分时钟信号差分后的信号(图7 中虚线)存在反射噪声,信号抖动明显;而图6、图7 表明改进的端接中相应的差分后信号(图6 中的点划线DESIGN DOUTP23i_DOUTP22i_diff和图6 中的实线)几乎没有反射噪声,信号抖动很小。

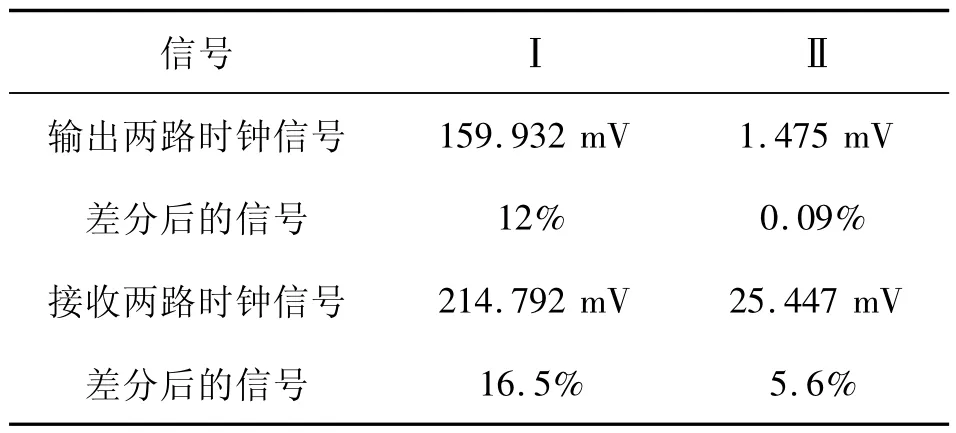

驱动端输出和负载端接收的两路差分时钟信号差分后的信号是关键信号。关键信号的过冲及其占相应信号电平峰峰值(Vp-p)的百分比,如表1所示。

表1 不同端接设计的仿真结果

表中“Ⅰ”代表常用的差分交流耦合端接,“Ⅱ”代表本文改进的LVPECL 差分时钟信号端接。由表1可以看出Ⅰ中输出信号存在反射噪声,破坏接收端信号差分特性,接收的差分后信号过冲214.792 mV,占Vp-p 的16.5%;而Ⅱ中几乎没有反射噪声,信号抖动很小,接收的信号差分特性良好,电压过冲在25.447 mV,占Vp-p 的5.6%,过冲比前者减少了10.9%。

由此可知,改进的端接方法可以很好地抑制反射噪声。下面分析不同传输距离和信号频率时,改进的端接方法对反射噪声的抑制情况。

4.2 不同传输距离下端接抑制反射噪声的仿真

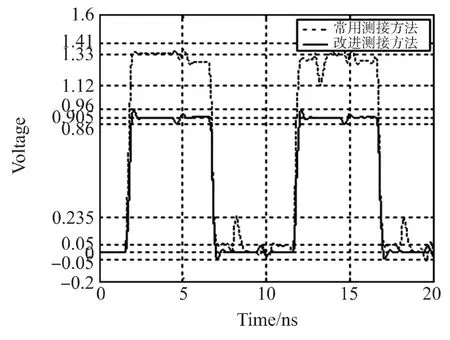

为了分析传输距离的增加会加大对对信号失真度完整性的影响,为验证改进的端接方式在不同传输距离下的反射噪声的抑制情况,本文对不同端接在传输距离分别为1200 mil、10 200 mil,信号频率为100 MHz 时进行仿真实验,仿真的结果如图8和表2。

图8 传输距离10 200 mil 时接收差分信号

表2 传输距离为1 200 mil、10 200 mil 的仿真结果

图8 中实线为常用交流耦合端接设计的仿真结果;虚线为改进的LVPECL 差分信号端接的仿真结果,实线和虚线分别代表相应端接负载端接收的两路差分时钟信号差分后的信号。

图8和表2 数据表明当传输距离增加时,负载端接收的差分后信号电压过冲有一定的增加但是变化不大,在表2 的Ⅰ中交流耦合中最小过冲为223.52 mV,占Vp-p 的16.8%;而在Ⅱ改进的LVPECL 差分时钟信号端接过冲最大为65.37 mV,占Vp-p 的7.3%。由此可见,当传输距离小于10 200 mil 时改进的LVPECL 差分时钟信号端接与交流耦合端接方法相比,能够更好地抑制差分时钟信号的反射噪声。

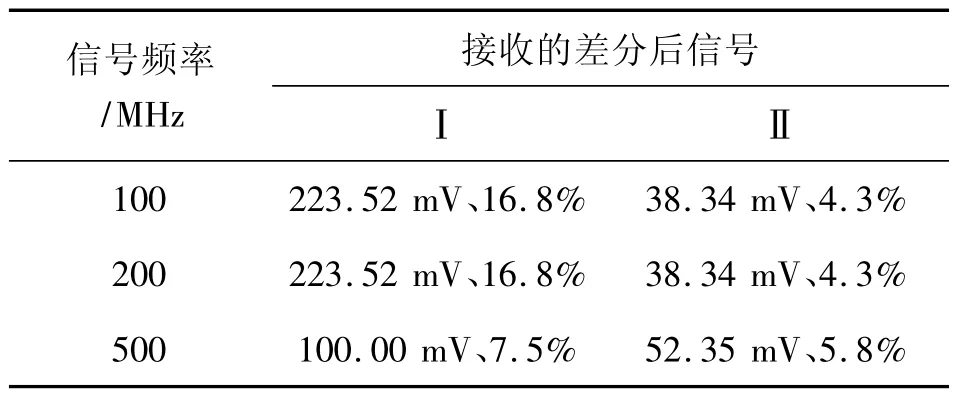

4.3 不同信号频率下端接抑制反射噪声的仿真

端接适合的频率范围是需要进一步分析的。因此,对文中提到的两种端接在信号频率分别为100 MHz、200 MHz、500 MHz,传输距离为1 200 mil 时进行仿真实验。接收的两路差分时钟信号差分后的信号(简称差分后信号)的过冲以及其占相应信号电压峰峰值(Vp-p)的百分比,如表3所示。

表3 信号频率为100 MHz、200 MHz、500 MHz 的仿真结果

当输入信号小于200 MHz 时负载端接收的差分后信号电压过冲基本保持不变,在表3Ⅰ交流耦合中约223 mV,占Vp-p 的16.8%,而在Ⅱ串联交流耦合中约40 mV,占Vp-p 的4.3%,与Ⅰ相比过冲占Vp-p 的百分比减少了12.5%;当信号频率在200 MHz~500MHz 之间时,Ⅰ中负载端接收差分后信号过冲随着频率增加逐渐减小至100 mV,最小占Vp-p的7.5%,而在Ⅱ中差分后信号过冲在52.35 mV 以下,最大占Vp-p 的5.8%。数据表明信号频率在500 MHz 以下时,与交流耦合端接方法相比,改进的LVPECL 差分时钟信号端接能够更好地抑制差分时钟信号的反射噪声。

5 结论

本文针对差分时钟信号在高速数据采集系统中存在的信号完整性问题,提出了一种改进的端接设计方法,进行了理论和实验仿真分析。通过基于AD9254 的高速数据采集系统实例对不同端接设计进行仿真,验证信号频率小于500 MHz、传输距离在10 200 mil 内时,常用的交流耦合端接中接收差分信号过冲在232.84 mV 以下,最大占Vp-p 的18.2%;而改进的LVPECL 差分时钟信号端接中接收到的差分时钟信号过冲在65.37 mV 以下,最大占Vp-p 的7.3%,过冲占比Vp-p 的百分比比前者减少了10.9%。因此,当信号小于500 MHz 时,与常用端接相比,改进的LVPECL 差分时钟信号端接能够更好地抑制反射噪声,改善了高速数据采集系统中差分时钟信号完整性问题,提高系统的稳定性和准确度。

[1]袁智勇,何金良,陈水明.印刷电路板差分线边缘布置的电磁兼容分析[J].电波科学学报,2004,19(6):689-693.

[2]郭土华,徐晓.基于高速嵌入式系统的信号完整性分析[J].电子技术应用,2011,37(1):55-57.

[3]陈建华,牛中奇.基于有限元法分析低电压差分驱动电路的辐射特性[J].微波学报,2008,24(3):61-66.

[4]Boni A.1.2-Gb/s True PECL 100K Compatible I/O Interface in 0.35-μm CMOS[J].Solid-State Circuits,IEEE Journal of,2001,36(6):979-987.

[5]鄢若韫,闫景富.数据传输系统中PECL 电平的接口设计[J].微计算机应用,2008,29(8):109-112.

[6]赵增辉,刘中友,彭圻平.高速差分信号的互连设计[J].无线电通信技术,2010,36(1):50-53.

[7]邓集杰,刘铁根,褚备,等.高速视频处理系统的信号完整性分析[J].电子测量与仪器学报,2009,23(6):34-41.

[8]Zhang M S,Li Y S,Jia C,et al.Signal Integrity Analysis of the Traces in Electromagnetic-Bandgap Structure in High-Speed Printed Circuit Boards and Packages[J].Microwave Theory and Techniques,IEEE Transactions on,2007,55(5):1054-1062.

[9]Johnson H,Graham M.High-Speed Digital Design[M].Beijing:Publishing House of Electronic Industry,2004.

[10]李成,程晓宇,毕笃彦,等.基于HyperLynx 的高速DSP 系统信号完整性仿真研究[J].电子器件,2009,32(2):445-451.

[11]李广辉,庄奕琪,曾志斌.基于信号完整性分析的一种视频处理系统设计[J].电子器件,2007,30(4):1325-1328.

[12]张艳丽,安琪,王砚方.基于PCB 仿真的高速时钟电路设计研究[J].计算机仿真,2004,21(9):175-178.