基于FPGA实时处理的视频信号滤波模块设计

来雪梅,张耀政

(中北大学信息与通信工程学院,山西太原030051)

基于FPGA实时处理的视频信号滤波模块设计

来雪梅,张耀政

(中北大学信息与通信工程学院,山西太原030051)

以Xilinx公司生产的FPGA芯片XC4VSX25及其开发系统为实验平台,针对TVP5150视频解码器输出的ITU-R BT.656格式数据,采用帧内滤波方法,通过VHDL硬件语言设计空间域滤波器,实现视频灰度信号的实时提取,并对每帧视频数据在二维空间内进行滤波与处理,这种方法可用于实时处理要求较高的场合。

视频信号;FPGA;滤波

视频信号的处理和图像信号的处理具有很大的不同,视频信号具有连续性,是不间断的图像信号所组成的数据流。视频图像的实时处理对系统性能有很高的要求,可编程逻辑器件能够采用并行处理技术实现数据流的处理。因此,数字视频图像滤波方法主要分为帧内 (空域)滤波方法和帧间(时间域)滤波方法两种。本设计采用帧内滤波方法,将视频中的灰度信号提取出来,对独立的每帧视频数据在二维空间内进行滤波。这样,既可以有效地去除帧与帧之间的相关性和帧内噪声,又可以利用V4系列芯片强大的数字信号处理资源来实现滤波处理的实时性,使得以往滤波实时性和计算量这两个的技术指标能够在最大程度上得到协调统一[1-4]。

1 系统硬件构成

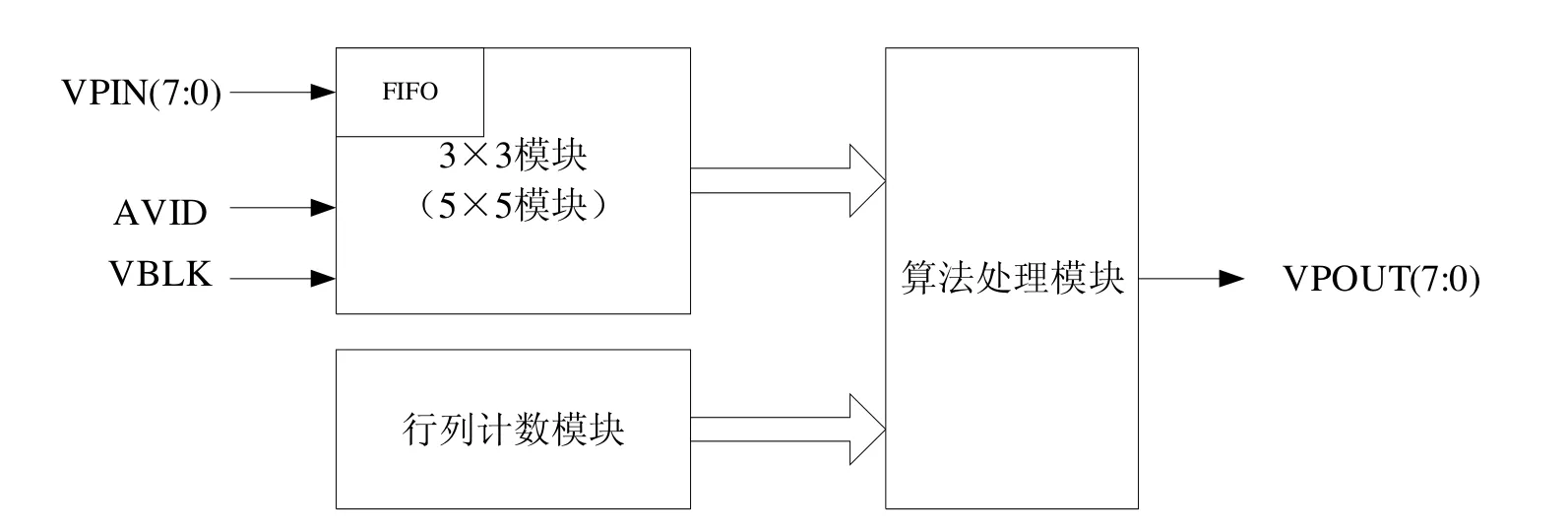

在FPGA硬件电路的图像处理系统的基础上,设计了TVP5150接口模块、缓存模块、EDK嵌入模块、模板生成模块、行列计数器模块以及算法处理模块。TVP5150接口设计模块功能目的是,得到同步信号和数据格式;缓存模块既是模板的基础同时也是数据缓存的重要环节;实现各种图像处理算法所需的基础是模板生成模块的主要功能之一;行列计数器模块是用来确定,正在处理的数据完成图像行列计数功能以及在图像数据阵列中的位置;算法处理模块是实现电路设计中的图像处理的硬件的核心模块,是对模板中数据值进行图像滤波算法处理。系统总体硬件模块框图见图1[5]。

图1 系统硬件结构图

2 滤波模块设计

通过EDK的编程以及配置TVP5150内部寄存器产生VBLK和AVID同步信号,在标准数据流ITU-R BT.656格式下,衰减色度信号为零值,使其成为13.5 MHz频率的只有亮度信号的数据流。在ISE的环境下,利用硬件描述语言VHDL完成滤波模块的设计。整个滤波模块可以分为方形窗口模块(3×3,5×5)、行列计数模块、缓存模块和数据处理模块。其中可以复用的是方形窗口模块和缓存模块,而数据处理模块可根据均值滤波和锐化滤波以及中值滤波的不同特性设置不同算法。

图2 滤波模块总体框图

滤波模块总体框图如图2所示。其中VPIN(7:0)为8位灰度图像信号输入,VPOUT(7:0)为经过图像算法处理后的8位信号输出。当VBLK为低电平、AVID为高电平时,13.5 MHz的数据就进入FIFO缓存模块,然后通过时序的设计,使得数据流依次进入3×3,5×5模板中的各个硬件模块中,当窗口中的值达到滤波条件时,行列计数器和算法处理模块开始进行滤波算法处理,整个数据流通过整个模块后,又按照原来顺序流出,达到了视频图像实时增强处理目的。

2.1 缓存模块

缓存模块采用FIFO(First In First Out)存储器,它是一个具有输入口和输出口两个端口的,能够按照先进先出的顺序,暂时存放数据的存储器件。作为一块数据内存,FIFO具有两个端口:一个将数据存入FIFO之中,另一个从FIFO当中把数据取出。与FIFO操作相关的有两个指针,其中写指针指向要写的内存部分,而读指针则指向要读的内存部分,FIFO控制器对这两个指针则通过外部的读写信号进行控制和操作,FIFO空信号或满信号均由此产生。为了保证模板中每行流出的数据为同一列,FIFO之间采用串联的方式,每个FIFO之间读数据的差值为一行720个有效数据,这样既方便构成模板,也便于后面的算法模块处理。因为读写时钟的不同,选择异步FIFO,数据的宽度选择与视频流的位数相同的8位,深度选择1024(〉720)。

2.2 模板生成模块[6]

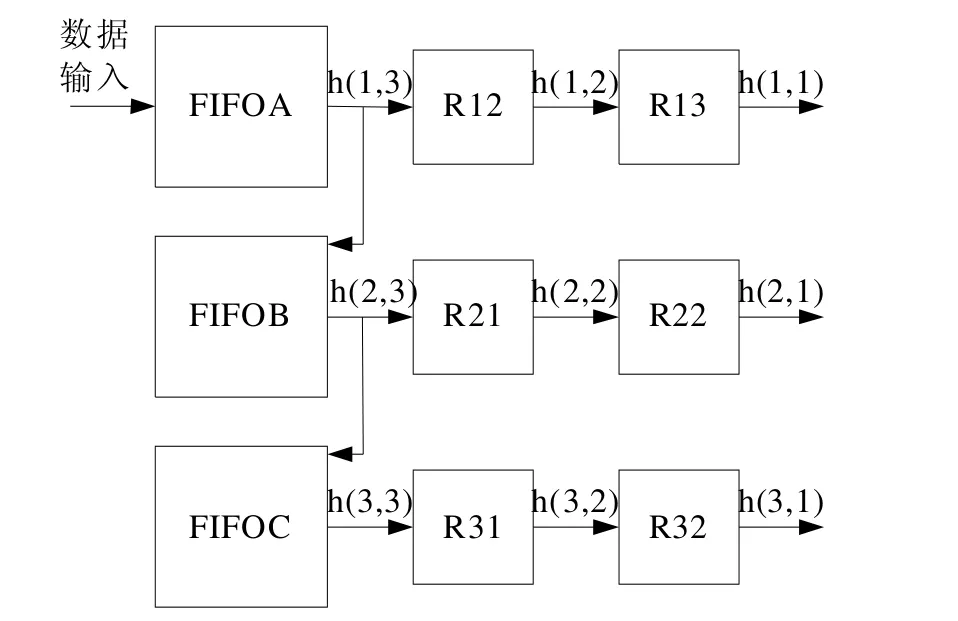

为得到后续的算法处理所需要的行列数据,根据模板窗口大小的不同,模板生成模块,生成3×3和5×5模板,3×3模板和5×5模板分别需要同时提供空间上相邻的9个数据和25个数据。这样模板生成后,在同一时刻把已经缓存好的9个或者25个数据同时提取到数据处理模块。图3为3×3模板图,图4为5×5模板流程图。

图3 3×3模板流程图

以3×3为例,在数据的处理过程中,为了能同时提到模板相应位置的9个数据而采用了三个FIFO存储器,每个FIFO必须存储一行共720个灰度数据。FIFO的深度为1024(〉720),宽度是8位,当AVID,VBLK满足条件时,FIFOA的写使能有效,写时钟为TVP5150同步输出频率为13.5 MHz的时钟SCLK,数据开始进入第一个FIFO中,与此同时相应的计数模块开始计数,FIFOA的读使能在计数达到720后有效,而为了使下个SCLK的上升沿来时第一行的第一个数据不仅能进入FIFOB,而且进入FIFOB的数据线必须有稳定的数据,则FIFOA写时钟要比读时钟早半个周期,这样可以既保证一行的数据量又保证下个写时钟到达时,数据能同步稳定的进入FIFOB和FIFOA。依照此原理,FIFOB的数据按顺序依次导入FIFOC中。这样,数据输入端分别同时输入第一行、第二行和第三行的数据,数据输出端同时输出相应的数据。同时这3个FIFO时序还要和六个寄存器相匹配,当FIFOB写满第一行的数据时,后续处理模块已经可以处理第一行的数据了,因此FIFOB的读使能有效与6个寄存器的写时能是同时有效的,这样第一行和第二行的数据在导入下一个FIFO时,又分别把数据转入后面的寄存器r2、r4、r6中,当下个时钟沿来时,这些数据再进入r3,r5,r7中,这样h(1,1)h(1,2)h(1,3)h(2,1)h(2,2)h(2,3)h(3,1)h(3,2)h(3,3)便构成了3×3的滤波窗口,而中心像素为h(2,2)。

图4 5×5模板流程图

在形成窗口过程时,还必须注意处理边界点。以3×3模板为例,如果不对行、列计数,将会出现每行最后两列和下一行第一列的象素形成滤波窗口或者第一帧的最后两行跟下一帧的第一行的情况,这时形成的滤波窗口不是我们要的滤波窗口,所以对于一帧图像来说,不论采用哪种滤波算法,第一行、第一列、最后一行和最后一列的像素点无法作为窗口中心点进行滤波算法的处理。因此,我们需要设计一个计数模块来对窗口的合理与否进行判断。

视频信号有效与否是通过判断 AVID和VBLK,clk为亮度时钟信号,ccln为列计数,rrow为行计数,这四位为“0000”当滤波模块处理的是合理模板的时候,当滤波模块处于第一行、第一列、最后一行、最后一列等不合理模块时,根据表1的对应关系可以得到不同的处理方式。

表1 3×3行列对应值

5×5模板的边缘检测可按照表2对应关系,多了第二行、倒数第二行、第二列和倒数第二列,因此不合理的窗口要比3×3窗口多。

表2 5×5行列对应值

根据表1和表2设计行列计数模块,根据不同的模板形式,提供不同的算法,从而为后续算法处理模块提供有效的判断标准。对不合理的窗口模块,为保证窗口大小一致性,在图像边缘处的像素无法用模板来覆盖并进行算法处理时把图像边缘不合理的像素区的值设置成0值。

2.3 算法处理模块

均值滤波意为滤除掉信号变化迅速的高频分量,而信号缓慢变化部分低频分量则保留下来,相反的,对于锐化滤波而言,边缘频率分量变化迅速属于高频部分,被保留下来。均值滤波和锐化滤波都是利用空间域的卷积来实现的,均值滤波模版的尺寸为3×3和5×5,锐化滤波为3×3。所使用的均值模板和高通模板分别为:

3 实时性与滤波结果分析

3.1 实时性

在实时性方面,输入和输出的延迟时间是决定实时性的本质,即数字视频数据处理运算的时间越少,实时性越好。在本文设计的视频图像增强系统中,决定实时性的因素主要有两个:模板缓存延迟和数据处理延迟。在模板缓存的设计中,视频流的处理是基于模板操作的,本质上只有当数据处于模板的中间行和中心像素的时候,才符合模板操作的条件,从而进一步进行增强运算。系统分别实现了两种模板两种方式。例如3×3模板,第二行是3×3模板的中心位置,只有当第一行的数字视频流数据进入缓存模块的中间FIFO时,第一行数据才能被处理掉。对于3×3模板而言,模板缓存模块造成了两行的数据延迟时间。每一行除了有效数据外根据视频流的基本格式,还有数据行消隐信号和辅助信号,一切通过缓存模板的输入输出的延迟时间为1728×2个时钟周期 (时钟周期为27MHz),同理运用于5×5模板,数据处理的中心行为第三行,延迟时间需要1728×3个时钟周期。而在数据处理方面,主要采用流水线的处理方式,能在视频流数据的一个时钟周期内运算完成,即:模板缓存的延迟时间是数据处理延迟时间的1728×N倍(N为整数,根据模板大小而定),因此数据处理的延迟影响相比模板缓存造成的延迟很小,可忽略不计。以数据实时处理能够完成为前提,系统的延迟将随着模板范围的不断扩大按一定的关系成比例增加。延迟时间的关系式:

其中,N为奇数方形模板的行列数,1728为一行

数据的采样点数,t为延迟时间。

3.2 滤波结果

(1)实验1。实验结果见图5。

(2)实验2。实验结果见图6。

(3)实验3。实验结果见图7。

4 结论

文章采用VHDL语言,在FPGA芯片XC4VSX25实验平台上实现了FIFO,3×3和5×5窗口模块、行列计数器模块和算法处理模块的滤波模块实时处理功能。通过对实时性的分析,计算了输入输出的延迟;通过实验,显示了不同背景的滤波效果,验证了系统设计的有效性。

图5 原始图像与3×3均值滤波图像对比图

图6 原始图像与3×3锐化滤波图像对比图

图7 原始图像与3×3锐化滤波图像对比图

[1]David Katz,Rick Gentile.Fundamentals of Embedded Video Processing[C].2008:42-45.

[2]田耘,胡彬,徐文波.Xilinx ISEDesign Suite 10.x FPGA开发指南[M].北京:人民邮电出版社,2008.

[3]田耘,徐文波.Xilinx FPGA开发实用教程[M].北京:清华大学出版社,2008.

[4]REC.ITU-R BT.656.Digtal TV System[S].1995.

[5]张耀政.基于FPGA实时处理的视频图像增强技术[D].太原:中北大学,2010.

[6]高金良.基于Adaboost算法的人脸实时脸检测及FPGA设计[D].太原:中北大学,2011.

The Design of F ilter M odule for V ideo S ignal b ase d on R eal-time P rocessing by FPGA

LAIXue-mei,ZHANG Yao-zheng

(School of Information and Communication Engineering,North University of China,Taiyuan Shanxi,030051)

Based on experimental platform of Xilinx Company′s FPGA chip XC4VSX25 and its development system,spatial filtermodule design is implemented to obtain video signals in real-time gray-scale extraction by use of the TVP5150 video decoder outputof ITU-R BT.656 format data,intra-frame filteringmethod and VHDL hardware design language.Video data of each frame is filtered and processed in two-dimensional space.Themethod can be used for situation of requiring real-time processing.

video signal;FPGA;filter〔责任编辑 李海〕

O571.5

A

1674-0874(2012)02-0022-06

2012-02-15

来雪梅(1969-),女,山西五台人,硕士,实验师,研究方向:测控技术。